一种低压电容型SARADC开关的制作方法

一种低压电容型sar adc开关

技术领域

1.本实用新型涉及cmos集成电路设计领域,具体涉及一种低压电容型sar adc开关。

背景技术:

2.电容型sar adc是一种逐次逼近型模数转换器,主要利用电荷重分配原理对输入信号进行量化处理。典型n位sar adc电路如图1所示,n组电容阵列公共端接到比较器输入,通过采样开关接到vin,电容阵列的另一端分别通过3个开关分别接到vdd,vss,vcm,vdd为电源电压,vss为地电压;vcm通常为比较器的输出控制sar logic电路,sar logic电路输出控制信号分别对电容阵列上的开关进行开启或者关断,从而产生电容电荷重分配过程,完成对输入vin的量化处理。随着工艺特征尺寸的降低,sar adc向着高速高精度以及低压供电的趋势发展,传统的cmos开关已经无法满足设计的需求。如图2,举例第s

n

‑1组开关,他们分别接到是vdd,vss,vcm,由于开关的非理想特性,开关存在导通电阻,高速应用需要有更短的建立时间,当开关导通时的电阻为ron,输入大小为vxin的阶跃信号(图2中vxin中可表示vdd,vss,vcm),tset为节点vx建立时间,则:

3.vx=vxin*(1

‑

e

‑

tset/(ron*c)

)

ꢀꢀ

(1)

4.adc速度越快,tset要求越小,sar adc精度越高,vx在tset时间内就必须越接近vxin,即希望开关导通的ron电阻越小越好。

5.传统的mos开关,通常为栅压控制电路,开关导通电阻为:

[0006][0007]

其中un、cox、w、l为常数,由于cmos开关管的寄生电容与l,w成正比,寄生电容过大,寄生电容将会参与电容电荷的从分配过程,所以w/l不能无限大,所以,当w/l固定时,开关导通电阻决定于vgs

‑

vth。如图2所示,连接vdd的开关为pmos管mp1,连接vss的开关为nmos管mn1,连接vcm的开关为nmos管mn2,这3个开关导通时,mn2的导通电阻最大,因为mn2的vgs为:

[0008][0009]

在低压应用中,当接近vth时,开关不能完全导通,即开关导通电阻ron变得很大,从而制约了sar adc的性能。

技术实现要素:

[0010]

发明目的:为了解决现有技术中sar adc开关在低压高速环境中导通电阻过大的问题,本实用新型提供一种低压电容型sar adc开关。

[0011]

技术方案:一种低压电容型sar adc开关,包括mos管、电平转换单元及电压选择单元,电压选择单元包括第一开关及第二开关,mos管的衬底与第一开关一端及第二开关一端连接,第一开关另一端连接最低电压,第二开关另一端连接第一参考电压;第一开关及第二

开关分别由第一控制信号和第二控制信号控制;电平转换单元的输入端连接第二控制信号,输出端连接mos管栅极;mos管输入端连接第一参考电压,mos管输出端输出信号。

[0012]

进一步地,设所述第一参考电压为vcm,vcm=(vdd

‑

vss)/2,其中,vdd为电源电压,vss为最低电压。

[0013]

进一步地,所述最低电压为地电压。

[0014]

进一步地,mos管的输入端为源极,输出端为漏极;或者mos管的输入端为漏极,输出端为源极。

[0015]

进一步地,所述第一控制信号与第二控制信号互为相反。

[0016]

进一步地,还包括正压产生电路,所述正压产生电路连接电平转换单元的供电端口,正压产生电路用于产生大于电源电压的正电压。

[0017]

一种低压电容型sar adc,包括上述的多个低压电容型sar adc开关、多个电容、比较器及sar逻辑单元,各电容的第一端连接比较器输入端,电容的另一端分别经过三个低压电容型sar adc开关连接电源电压、最低电压、第一参考电压,比较器的输入端连接输入信号,比较器的输出端连接sar逻辑单元的输入端,sar逻辑单元输出adc的输出信号,sar逻辑单元还用于产生互为相反的第一控制信号及第二控制信号。

[0018]

有益效果:本实用新型提供一种低压电容型sar adc开关,相比较现有技术,当vcm选通时,开关的导通电阻较小,非常适用于低压高速高精度环境下的sar adc,不会影响sar adc开关的关断性能,可以保证sar adc性能稳定可靠。

附图说明

[0019]

图1为传统sar adc的电路示意图;

[0020]

图2为切换开关等效示意图;

[0021]

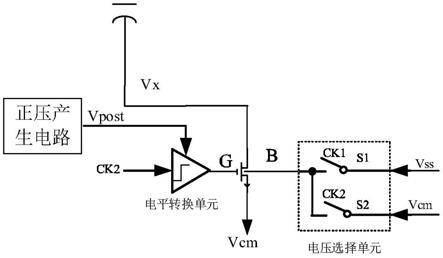

图3为本实施例中低压电容型sar adc开关;

[0022]

图4为电平转换单元的原理图;

[0023]

图5为本实施例中正压产生电路的原理图。

具体实施方式

[0024]

下面结合附图和具体实施例对本发明做进一步解释说明。

[0025]

一种低压电容型sar adc开关,如图3所示,包括mos管、电平转换单元及电压选择单元,电压选择单元包括第一开关s1及第二开关s2,mos管的衬底与第一开关s1、第二开关s2的公共端连接,第一开关s1另一端连接最低电压vss,第二开关s2另一端连接第一参考电压vcm;第一开关s1及第二开关s2分别由第一控制信号ck1和第二控制信号ck2控制;电平转换单元的输入端连接第二控制信号ck2,输出端连接mos管栅极;mos管输入端连接第一参考电压vcm,mos管输出端输出信号vx。

[0026]

设所述第一参考电压为vcm,vcm=(vdd

‑

vss)/2,其中,vdd为电源电压,vss为最低电压。所述最低电压vss为地电压。

[0027]

本实施例以nmos管为例,nmos管的输入端为源极,输出端为漏极;也可以将mos管的漏极作为输入端,源极作为输出端,根据需要选择。

[0028]

所述第一控制信号ck1与第二控制信号ck2互为相反,保证第一开关与第二开关不

同时导通。

[0029]

还包括正压产生电路,如图4所示,所述正压产生电路连接电平转换单元的供电端口,使得电平转换单元在输入ck2为高电平时,输出信号clk_out为比电源电压高的电压vpost。

[0030]

一种低压电容型sar adc,包括上述多个低压电容型sar adc开关、多个电容、比较器及sar逻辑单元,各电容的第一端连接比较器输入端,电容的另一端分别经过三个低压电容型sar adc开关连接电源电压vdd、最低电压vss、第一参考电压vcm,比较器的输入端连接输入信号,比较器的输出端连接sar逻辑单元的输入端,sar逻辑单元输出adc的输出信号adc output,sar逻辑单元还用于产生互为相反的第一控制信号ck1及第二控制信号ck2,用作第一开关s1与第二开关s3的控制及电平转换单元的输入。

[0031]

如图3,当开关关断时,第二控制信号ck2为低电平,第一控制信号ck1为高电平,此时第一开关s1处于闭合状态,第二开关s2处于断开状态,地电压vss连接到nmos的衬底端,同时第二控制信号ck2通过电平转换单元输出为低,nmos开关被关断。

[0032]

当开关导通时,第二控制信号ck2为高电平,第一控制信号ck1为低电平,此时第一开关s1为断开状态,第二开关s2处于闭合状态,vcm电压连接到nmos管的衬底端,设导通电压阈值为vth,由于vth是衬偏电压vbs的函数,且vth的值与vbs成反比,vcm>vss,相比传统衬底接vss的nmos开关而言,vth得到了减小;同时第二控制信号ck2通过电平转换单元输出为高,电平转换单元供电为正电压产生电路,正电压产生电路如图5所示,可以产生vpos的正电压,因此,电平转换单元输出电压为vpos,

[0033]

vpos=vcm+vdd

‑

vss

ꢀꢀ

(4)

[0034]

此时vgs=vpos

‑

vcm=vdd

ꢀꢀ

(5)

[0035]

传统的nmos开关栅端连接vdd时的vgs’=vdd

‑

vcm

ꢀꢀ

(6)。

[0036]

由(5)(6)可知,相比传统开关,vgs得到了增加。

[0037]

由公式(2)可知,本实施例中开关导通时减小了vth,增加了vgs,有效地降低了开关导通时的电阻,克服了sar adc在低压高速高精度应用中,导通开关电阻过大的缺点。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1