电路板叠加结构的制作方法

1.本技术涉及电路板领域,尤其涉及一种电路板叠加结构。

背景技术:

2.现有的电路板叠加结构通常包括射频电路板(rf板)、框架板(fb板)和主板(mlb板)。在该电路板叠加结构的制作过程中,需要先在mlb板上封装元器件,然后再将fb板封装在mlb板上,最后再封装rf板。该制作过程需要经过三次高温封装,对材料具有较高的耐热性要求。同时,由于该制作过程需要多次对位,对rf板、fb板以及mlb板的尺寸精度也要求较高。另外,多次封装也容易降低电路板叠加结构的良率。

技术实现要素:

3.有鉴于此,本技术提供一种能够解决上述至少一种问题的电路板叠加结构。

4.本技术一实施例提供一种电路板叠加结构,包括:

5.射频电路板,所述射频电路板包括第一介质层、位于所述第一介质层相对两表面上的第一导电线路层和第二导电线路层、以及位于所述第一介质层内部的多个第三导电线路层,所述第一导电线路层包括第一焊垫,其中一所述第三导电线路层包括接地线,所述射频电路板中开设有收容槽;

6.主板,所述主板包括第二介质层以及位于所述第二介质层相对两表面上的第四导电线路层和第五导电线路层,所述第四导电线路层包括第二焊垫和第三焊垫,且所述第二焊垫和所述第一焊垫电性连接;以及

7.元器件,所述元器件收容于所述收容槽中,且所述元器件和所述第三焊垫电性连接。

8.在一些可能的实施例中,所述收容槽贯穿所述第一导电线路层以及至少一所述第三导电线路层,且所述收容槽的底部对应所述接地线。

9.在一些可能的实施例中,所述射频电路板中设有第一导电部以及第二导电部,所述第一导电部用于电性连接所述第一导电线路层和与所述第一导电线路层相邻的所述第三导电线路层、电性连接所述第二导电线路层和与所述第二导电线路层相邻的所述第三导电线路层、以及电性连接部分相邻的两个所述第三导电线路层,所述第二导电部用于电性连接部分相邻的两个所述第三导电线路层。

10.在一些可能的实施例中,与所述第一导电线路层相邻的一所述第三导电线路层包括所述接地线,所述收容槽贯穿所述第一导电线路层,且所述收容槽的底部对应所述接地线。

11.在一些可能的实施例中,所述射频电路板中设有第一导电部以及第二导电部,所述第一导电部用于电性连接所述第二导电线路层和与所述第二导电线路层相邻的所述第三导电线路层、以及电性连接部分相邻的两个所述第三导电线路层,所述第二导电部用于电性连接所述第一导电线路层、所述第二导电线路层以及所述第三导电线路层。

12.在一些可能的实施例中,所述射频电路板还包括第一保护层,所述第一保护层位于所述收容槽的内壁和底面上。

13.在一些可能的实施例中,所述收容槽的深度为0.8-1.3mm,所述收容槽横截面面积占所述射频电路板横截面面积的比例为80-95%。

14.在一些可能的实施例中,所述电路板叠加结构还包括导电件,所述导电件用于电性连接所述第一焊垫和所述第二焊垫。

15.在一些可能的实施例中,所述导电件为导电柱。

16.在一些可能的实施例中,所述主板还包括第六导电线路层,所述第六导电线路层位于所述第二介质层中。

17.本技术中的所述射频电路板中开设有所述收容槽,并将所述元器件收容于所述收容槽中,避免使用框架板以降低封装次数,在一定程度上能够降低对所述主板的耐热性要求,并能够提高所述电路板叠加结构的良率。同时,本技术只需所述射频电路板和所述主板对位,无需框架板和所述主板对位,从而降低了对所述射频电路板和所述主板的尺寸精度的要求,进而提高了所述电路板叠加结构的良率。

附图说明

18.图1是本技术第一实施例提供的射频电路板的剖视图。

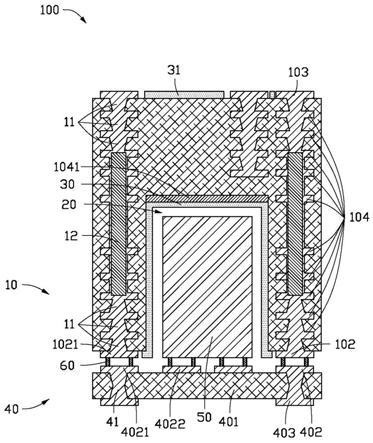

19.图2是将图1所述的射频电路板和主板以及元器件连接后得到的电路板叠加结构的剖视图。

20.图3是本技术第二实施例提供的射频电路板的剖视图。

21.图4是将图3所述的射频电路板和主板以及元器件连接后得到的电路板叠加结构的剖视图。

22.主要元件符号说明

23.电路板叠加结构

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

100、200

24.射频电路板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10、13

25.第一介质层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

101

26.第一导电线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

102

27.第二导电线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

103

28.第三导电线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

104

29.接地线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1041、1042

30.第一导电部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

11、14

31.第二导电部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

12、15

32.收容槽

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20、21

33.第一保护层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

30

34.第二保护层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

31

35.主板

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40

36.第二介质层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

401

37.第四导电线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

402

38.第二焊垫

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4021

39.第三焊垫

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4022

40.第五导电线路层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

403

41.第三导电部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

41

42.元器件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

50

43.导电件

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60

44.如下具体实施方式将结合上述附图进一步说明本技术。

具体实施方式

45.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。

46.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

47.为能进一步阐述本技术达成预定目的所采取的技术手段及功效,以下结合附图及较佳实施方式,对本技术作出如下详细说明。

48.请参阅图1和图2,本技术第一实施例提供一种电路板叠加结构100,所述电路板叠加结构100包括射频电路板10、主板40以及元器件50。

49.在本实施例中,所述射频电路板10包括第一介质层101、位于所述第一介质层101相对两表面上的第一导电线路层102和第二导电线路层103、以及位于所述第一介质层101内部的多个第三导电线路层104。

50.所述第一介质层101的材质可以选自环氧树脂(epoxy resin)、聚丙烯(polypropylene,pp)、bt树脂、聚苯醚(polyphenylene oxide,ppo)、聚酰亚胺(polyimide,pi)、聚对苯二甲酸乙二醇酯(polyethylene terephthalate,pet)以及聚萘二甲酸乙二醇酯(polyethylene naphthalate,pen)等树脂中的一种。在本实施例中,所述第一介质层101的材质为聚丙烯。

51.其中,所述第一导电线路层102包括第一焊垫1021。不与所述第一导电线路层102相邻的一所述第三导电线路层104包括接地线1041。如图1所示,仅仅示出了十个所述第三导电线路层104。实际上,所述射频电路板10中的所述第三导电线路层104的数量可根据需要进行变更。

52.所述射频电路板10中设有第一导电部11以及第二导电部12。其中,所述第一导电部11用于电性连接所述第一导电线路层102和与所述第一导电线路层102相邻的所述第三导电线路层104、电性连接所述第二导电线路层103和与所述第二导电线路层103相邻的所述第三导电线路层104、以及电性连接部分相邻的两个所述第三导电线路层104。所述第二导电部12贯穿部分所述第三导电线路层104,即所述第二导电部12未贯穿全部所述第三导电线路层104。所述第二导电部12用于电性连接部分相邻的两个所述第三导电线路层104。

53.所述射频电路板10中开设有收容槽20。其中,所述收容槽20贯穿所述第一导电线路层102以及至少一所述第三导电线路层104,且所述收容槽20的底部对应所述接地线1041。

54.在本实施例中,所述收容槽20的深度为0.8-1.3mm。在本实施例中,所述收容槽20

横截面面积占所述射频电路板10横截面面积的比例为80-95%。

55.在本实施例中,所述射频电路板10还包括第一保护层30以及第二保护层31。其中,所述第一保护层30位于所述收容槽20的内壁和底面上,所述第二保护层31位于所述第二导电线路层103的间隙中。

56.在本实施例中,所述主板40包括第二介质层401、位于所述第二介质层401相对两表面上的第四导电线路层402和第五导电线路层403、以及位于所述第二介质层401内部的多个第六导电线路层(图未示)。

57.在本实施例中,所述第二介质层401的材质可与所述第一介质层101的材质相同,具体可参考所述第一介质层101的材质,在此不再详述。

58.其中,所述第四导电线路层402包括第二焊垫4021和第三焊垫4022。本技术对所述第六导电线路层的数量不作限制,即所述主板40中的所述第六导电线路层中的数量可根据需要进行变更。

59.请再次参阅图2,所述主板40中设有第三导电部41。其中,所述第三导电部41用于电性连接所述第四导电线路层402和与所述第四导电线路层402相邻的所述第六导电线路层、电性连接两个相邻的所述第六导电线路层、以及电性连接所述第五导电线路层403和与所述第五导电线路层403相邻的所述第六导电线路层。

60.所述元器件50收容于所述收容槽20中,且所述元器件50和所述第三焊垫4022电性连接,以使所述元器件50与所述主板40电性连接。

61.在本实施例中,所述电路板叠加结构100还包括导电件60。其中,所述导电件60用于电性连接所述第一焊垫1021和所述第二焊垫4021,以使所述第一导电线路层102和所述第四导电线路层402电性连接,从而使所述射频电路板10和所述主板40电性连接,进而使所述射频电路板10和所述元器件50电性连接。在本实施例中,所述导电件60可为导电柱。具体地,所述导电柱的材质可为铜。在其他实施例中,所述导电件60也可为导电膏。具体地,所述导电膏可为锡膏以及铜膏等。

62.请参阅图3和图4,本技术第二实施例提供一种电路板叠加结构200,第二实施例提供的所述电路板叠加结构200和第一实施例提供的所述电路板叠加结构100的区别在于:在所述射频电路板13中,与所述第一导电线路层102相邻的一所述第三导电线路层104包括所述接地线1042,所述收容槽21未贯穿任何其中一所述第三导电线路层104。所述第一导电部14用于电性连接所述第二导电线路层103和与所述第二导电线路层103相邻的所述第三导电线路层104、以及电性连接部分相邻的两个所述第三导电线路层104。所述第二导电部15贯穿全部的所述第三导电线路层104,且所述第二导电部15用于电性连接所述第一导电线路层102、所述第二导电线路层103以及所述第三导电线路层104。

63.本技术中的所述射频电路板10中开设有所述收容槽20,并将所述元器件50收容于所述收容槽20中,避免使用框架板以降低封装次数,在一定程度上能够降低对所述主板40的耐热性要求,并能够提高所述电路板叠加结构100的可靠性和良率。同时,本技术只需所述射频电路板10和所述主板40对位,无需框架板和所述主板40对位,从而降低对所述射频电路板10和所述主板40的尺寸精度的要求,进而提高了所述电路板叠加结构100的良率。

64.以上说明仅仅是对本技术一种优化的具体实施方式,但在实际的应用过程中不能仅仅局限于这种实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1