SerDes接口电路以及控制装置的制作方法

serdes接口电路以及控制装置

技术领域

1.本技术中提及的实施例涉及serdes接口电路以及控制装置。

背景技术:

2.近年来,控制机床的计算机数值控制(cnc:computerized numerical control)装置随着安装各种功能而变得高速化,例如,在成为控制对象的机床与cnc装置之间的数据通信中,使用能够进行大容量的高速数据传输的serdes(serializer/deserializer:串行器/解串器)。

3.serdes例如用于将在一方的装置中使用的并行数据变换为串行数据来传输给另一方的装置,在该另一方的装置中,将接收到的串行数据再次变换为并行数据来使用,因此不考虑并行通信中的各比特间的布线长度或杂散电容引起的时滞,另外,能够减少布线或端子数来进行高速数据通信。

4.因此,以往提出了与使用了serdes的数据通信有关的各种方案。

5.现有技术文献

6.专利文献

7.专利文献1:日本特开2019-140489号公报

8.专利文献2:日本特开2009-109488号公报

9.专利文献3:日本特开2011-193068号公报

10.专利文献4:日本特开2016-072772号公报

技术实现要素:

11.发明所要解决的课题

12.如上所述,serdes能够进行大容量的高速数据通信,因此在各种领域中使用。例如,由asic(application specific integrated circuit:专用集成电路)的制造商或技术决定了该serdes能够通信的通信速率范围,因此无法以serdes的下限以下的通信速率使用。因此,难以使用相同的serdes来进行通信速率不同的机型(包括装置、电路块等)的通信。

13.另外,近年来,有时在1个装置中使用不同规格的多个数据(例如,通信速率(动作时钟)不同的多个数据)。因此,例如,要求在一方的装置(本装置)中,使用相同的(1个)serdes将不同通信速率的数据变换为预定通信速率的串行数据,并传输到另一方的装置(对方装置)。在对方装置中,使用serdes或者通过其他通信接口对传输来的串行数据进行处理。

14.具体而言,例如,在本装置为cnc装置的情况下,要求使用相同的serdes将基于180mhz的时钟的16比特并行数据和基于160mhz的时钟的1比特信号变换为通信速率为2.88gbps的串行数据,并传输给对方装置(例如,对机床的伺服电动机进行控制的电动机放大器)。这些装置并不限于cnc装置以及机床,例如,也能够应用机器人控制装置作为本装

置,应用由机器人控制装置控制的工业机器人、协作机器人等作为对方装置。

15.并且,180mhz的16比特并行数据和160mhz的1比特信号只不过是单纯的例子,180mhz、160mhz这样的时钟的频率能够适当变更,16比特的并行数据也不限于16比特。另外,160mhz的1比特信号也是为了简化说明而设为1比特,当然例如也可以是32比特、64比特等多个比特的并行数据。

16.鉴于上述问题,本发明的目的在于提供一种能够使用相同的serdes来进行不同通信速率的数据传输的serdes接口电路以及控制装置。

17.用于解决课题的手段

18.根据本发明的实施方式,提供一种serdes接口电路,其具有:fifo,其接收第一频率的第一时钟、基于所述第一时钟的第一发送数据、以及与所述第一频率不同的第二频率的第二时钟,并基于所述第二时钟,按照输入的顺序输出所述第一发送数据;触发器,其基于所述第二时钟,取入并保持所述fifo的输出;以及输出状态机,其接收所述fifo的输出以及所述触发器的输出,基于所述第二时钟来生成与所述第一发送数据对应的相同数据连续的并行数据。

19.发明效果

20.本公开的serdes接口电路和控制装置起到能够使用相同的serdes来进行不同通信速率的数据传输的效果。

21.特别是通过使用在保护范围中指出的构成要素和组合,能够认识并得到本发明的目的和效果。上述的一般的说明及后述的详细的说明这两者是例示性的以及说明性的说明,并非对保护范围中记载的本发明进行限制。

附图说明

22.图1是表示本发明的控制装置的一实施方式的框图。

23.图2用于说明图1所示的控制装置中的serdes的一例。

24.图3用于说明图1所示的控制装置中的serdes接口电路的第一实施例。

25.图4用于说明图3所示的serdes接口电路的动作。

26.图5是表示图1所示的控制装置中的数据恢复电路的一例的框图。

27.图6用于说明图5所示的数据恢复电路的动作。

28.图7用于说明图3所示的serdes接口电路的另一应用例。

29.图8用于说明图7所示的serdes接口电路的动作。

30.图9用于说明图1所示的控制装置中的serdes接口电路的变形例。

31.图10用于说明图9所示的serdes接口电路中的具有输出数量控制功能的fifo。

具体实施方式

32.以下,参照附图详细描述本发明的serdes接口电路和控制装置的实施例。图1是表示本发明的控制装置的一实施方式的框图。

33.如图1所示,本实施方式的控制装置10具有新通信控制电路1、兼容通信控制电路2、serdes接口电路3、数据恢复(data recovery:dr)电路4、比特变换电路5、选择器6以及serdes(串行器/解串器)7。

34.控制装置10例如通过serdes7将经由新通信控制电路1的180mhz的16比特并行数据(基于频率为180mhz的时钟的16比特并行数据:第二发送数据)以及经由兼容通信控制电路2的160mhz的1比特信号(基于频率为160mhz的时钟的1比特信号:第一发送数据)变换为通信速率为2.88gbps(比特/秒)的串行数据,在与对方装置(通信对象侧的装置)200之间进行收发。

35.例如,在对方装置200中也设置serdes,能够将从控制装置10(本装置100)发送的2.88gbps的串行数据变换为并行数据来使用。即,可以通过对方装置200的serdes将2.88gbps的串行数据变换为180mhz的16比特并行数据和160mhz的信号,并且将其输入到例如由180mhz的16比特并行数据控制的电路和由160mhz的信号控制的电路。

36.或者,也可以不在对方装置200中设置serdes,而利用其他的通信接口电路对发送来的串行数据进行处理。另外,为了简化说明,将经由兼容通信控制电路2的160mhz的信号设为1比特,但如上所述,也可以是多个比特的并行数据。

37.在此,作为本装置100,例如能够举出cnc装置以及机器人控制装置这样的各种控制装置,另外,作为对方装置200,能够举出由cnc装置控制的各种机床以及工业机器人、协作机器人这样的装置(或者,用于控制该机床以及机器人中的电动机的电动机放大器等),但并不限于此。

38.serdes接口电路3从兼容通信控制电路2接收160mhz的1比特信号(第一发送数据),变换为具有与该第一发送数据对应的(相同的)逻辑值的基于180mhz的时钟的并行信号来输出。选择器6接收来自新通信控制电路1的180mhz的16比特并行数据(第二发送数据)和来自serdes接口电路3的180mhz的16比特并行数据,选择其中一方并输出到serdes7的发送用并行数据输入(tx_pdata)。

39.图2用于说明图1所示的控制装置中的serdes的一例。在此,图2的(a)是表示serdes7的输入输出数据的框图,图2的(b)是用于说明serdes7的数据发送时的处理(并行/串行变换处理)的图,图2的(c)是用于说明serdes7的数据接收时的处理(串行/并行变换处理)的图。serdes特别是在高速接口中在并行接口间进行串行连接等情况下使用,但作为本实施方式的控制装置10的serdes7,能够应用一般的serdes。

40.在图2的(a)中,参考符号tx_pdata表示从本装置(设置有控制装置10的这一侧的装置)100向对方装置200发送的发送并行数据(例如,基于180mhz的时钟的16比特并行的发送并行数据:以及发送并行数据的输入),tx_sdata表示将发送并行数据tx_pdata变换为串行数据后向对方装置200发送的发送串行数据(例如,通信速率为2.88gbps的发送串行数据:以及发送串行数据的输出)。

41.此外,在图2的(a)中,参考符号rx_sdata表示从对方装置200发送来的接收串行数据(例如,通信速率为2.88gbps的接收串行数据和接收串行数据的输入),rx_pdata表示将接收串行数据rx_sdata变换为并行数据而得到的接收并行数据(例如,基于180mhz的时钟的16比特并行的接收并行数据:以及接收并行数据的输出)。pclk表示发送并行数据tx_pdata的时钟(例如,180mhz的时钟:以及发送并行数据的时钟的输入),rclk表示通过cdr(clock data recovery:时钟数据恢复)接收接收串行数据并从该接收串行数据再生的恢复时钟(以及恢复时钟的输出)。

42.首先,如图2的(b)所示,在数据发送时,serdes7例如对基于180mhz的pclk的16比

特的发送并行数据tx_pdata进行并行/串行变换,使得从下位比特开始输出,即,基于180mhz

×

16比特变换为通信速率为2.88gbps的发送串行数据tx_sdata,并输出到对方装置200。接下来,如图2的(c)所示,在数据接收时,serdes7从对方装置200接收通信速率为2.88gbps的接收串行数据rx_sdata,将其变换为16比特的接收并行数据rx_pdata并输出。

43.如此,在将动作时钟的频率设为x(例如,180mhz),将并行数据的比特数设为y(例如,16比特)时,serdes7能够使串行数据的通信速率z为z=x

×

y[bps](例如,180mhz

×

16比特=2.88gbps)。

[0044]

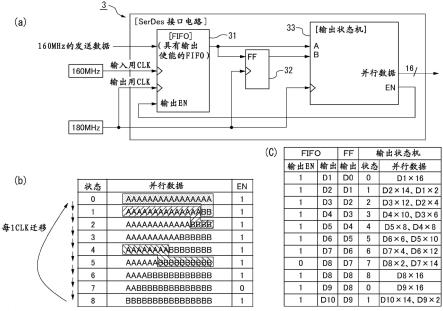

图3用于说明图1所示的控制装置中的serdes接口电路的第一实施例。在此,图3的(a)是表示serdes接口电路的第一实施例的框图,图3的(b)和图3的(c)用于说明图3的(a)所示的serdes接口电路中的输出状态机的动作。如图3的(a)所示,serdes接口电路3具有fifo(具有输出使能(en)的fifo(first in first out:先进先出))31、触发器(ff)32和输出状态机33。

[0045]

fifo31接收频率为160mhz的输入用时钟(第一时钟)、基于160mhz的时钟的1比特的信号(160mhz的发送数据:第一发送数据)、以及频率为180mhz的输出用时钟(第二时钟),并基于第一时钟取入第一发送数据,在输出en为“1”的情况下,基于第二时钟按顺序输出取入的数据。另外,在输出en为“0”的情况下,维持紧前的输出。将fifo31的输出作为信号a输入到输出状态机33,并且输入到触发器32的数据端子。在此,第二时钟的频率与从参照图1说明的新通信控制电路1输出的16比特的并行数据的动作时钟(180mhz)对应。

[0046]

对触发器32的时钟端子输入180mhz的第二时钟,基于第二时钟取入来自fifo31的第一发送数据并保持该数据,将保持的该数据作为信号b输出到输出状态机33。即,输出状态机33接收某个定时的来自fifo31的第一发送数据(a:fifo输出)和比该定时提前第二时钟的1个时钟的定时的来自fifo31的第一发送数据(b:ff输出)。对输出状态机33的时钟输入端子输入第二时钟,另外,对fifo31的输出使能端子输入来自输出状态机33的使能信号(en)。

[0047]

输出状态机33基于输入到端子a的信号(a)和输入到端子b的信号(b),例如在串行数据中生成18比特相同的数据连续(具有相同的逻辑值)的并行数据。在此,在图3的(b)中,例如,状态“1”的数据“b”是由触发器32通过前1个时钟(180mhz)取入的数据,因此具有与状态“0”的数据“a”相同的逻辑值。因此,通过对状态“0”的数据“a”的16比特的并行数据加上状态“1”的数据“b”的2比特的并行数据,生成具有18比特相同的逻辑值的16比特的并行数据。

[0048]

同样地,例如,通过对状态“1”的数据“a”的14比特的并行数据加上状态“2”的数据“b”的4比特的并行数据,生成具有18比特相同的逻辑值的16比特的并行数据,并且,通过对状态“4”的数据“a”的8比特的并行数据加上状态“5”的数据“b”的10比特的并行数据,生成具有18比特相同的逻辑值的16比特的并行数据。另外,由于状态“7”的en为“0”,因此在状态“8”下fifo输出不被更新,将已向状态“7”的“a”和状态“8”的“b”输入的数据的下一个fifo输出数据输入到状态“0”的“a”和状态“1”的“b”。

[0049]

这样,例如,将来自兼容通信控制电路2的160mhz的1比特信号在从状态“0”到状态“8”之间处理8比特,反复进行该处理。图3的(c)表示向图3的(a)的fifo31输入了d0、d1、d2、

…

(在此,d0、d1、d2、

…

分别为“0”或“1”)的数据时的、每1时钟(180mhz)的fifo31、ff32

以及输出状态机33的输入输出信号以及内部状态。

[0050]

如图3的(c)所示,例如,在状态“8”下,“a”不会出现在输出状态机33的并行数据中,因此需要停止fifo31的输出数据的更新,在状态“7”下将en设为“0”。另外,状态“8”下的fifo31的输出“a”和状态“0”下的ff32的输出“b”双方都为d8,但不会影响并行数据(即,由于停止了fifo31的数据更新而为d8,但另外也可以是“0”也可以是“1”)。这样,根据图3的(c)可知,在从状态“0”到状态“8”的1组中,每18比特输出8比特的数据来作为并行数据。

[0051]

在此,在输出状态机33生成的并行数据(16比特并行数据)中,在将与第一发送数据(160mhz的1比特的信号)对应的相同数据连续的比特数设为v(18),将第一时钟的频率设为w(160mhz),将第二时钟的频率设为x(180mhz),并且将基于第二时钟的第二发送数据中的并行数据的比特数设为y(16)时,相同数据连续的比特数v能够通过v=(x

×

y)/w来表示。

[0052]

以上,在输入给fifo31的第一发送数据为多个比特的情况下,例如,在来自兼容通信控制电路2的信号为160mhz的多个信号的情况下,也能够进行实质上同样的处理。

[0053]

图4用于说明图3所示的serdes接口电路的动作。如上所述,作为发送并行数据tx_pdata,将由serdes接口电路3(输出状态机33)生成的“1111111111111111”这样的连续的相同数据输入到serdes7,从而能够降低实质的通信速率。

[0054]

如图4所示,例如,在以2.88gbps的通信速率发送160mbps的信号时,为了以相同的serdes7(相同的通信速率)发送160mbps(mhz)的1比特的信号,成为2.88g/160m=18,所以将160mbps的1比特的信号变换为18比特相同的数据连续的并行数据来输入给serdes7。

[0055]

由此,serdes接口电路3(输出状态机33)输出180mhz的16比特并行数据,但是由于与160mbps的1比特相对应的数据是将相同逻辑值连续18比特的并行数据,因此实际上降低发送串行数据tx_sdata的通信速率来进行数据传输。由此,能够使用相同的serdes7进行不同的通信速率(不同规格)的数据传输。

[0056]

图5是表示图1所示的控制装置中的数据恢复电路的一例的框图,图6用于说明图5所示的数据恢复电路的动作。在图5中,参考符号rx_sdata表示接收串行数据,refclk表示基准时钟,rx_pdata表示n比特的接收并行数据,rclk表示通信速率的1/n的频率的恢复时钟,并且edg_data表示边缘位置数据。另外,参考符号calc_edg表示边缘预测位置数据,sample_point表示采样位置数据,cntup表示用于使相位提前的相位控制信号,cntdn表示用于使相位延迟的相位控制信号,rdata表示恢复数据,并且rdata_en表示数据使能信号。

[0057]

图5所示的数据恢复(dr)电路4对应于在前面记载的专利文献4中公开的数据再生电路。之前,如参照图1以及图2说明的那样,例如,通过serdes7,将通信速率为2.88gbps的接收串行数据rx_sdata变换为基于180mhz的时钟的16比特并行的接收并行数据rx_pdata。然后,如图1所示,将通过该serdes7变换后的接收并行数据rx_pdata输入到dr电路4。另外,dr电路4将2比特的信号与数据使能rdata_en一起输出到比特变换电路5,比特变换电路5根据数据使能rdata_en生成1比特的信号,对兼容通信控制电路2输出160mhz的1比特信号。即,dr电路4和比特变换电路5构成变换处理电路,该变换处理电路接收通过serdes7变换后的接收并行数据rx_pdata,变换为与160mhz的1比特信号(第一发送数据)相同规格的信号,并输出到兼容通信控制电路2。

[0058]

如图5所示,dr电路4接收来自过采样部(serdes)7的信号(接收并行数据rx_pdata和恢复时钟rclk)。过采样部7以比串行数据的通信速率高的频率的时钟对通过串行通信接

收到的串行数据(接收串行数据)rx_sdata进行采样,输出n(n为2以上的整数)比特的接收并行数据rx_pdata以及该采样时钟的1/n的频率的恢复时钟rclk。

[0059]

dr电路4具有边缘检测部41、边缘位置计算部42、数据采样部43以及相位比较部44。如图6所示,边缘检测部41检测并行数据的边缘位置,并作为边缘数据而输出。边缘位置计算部42根据相位比较部44输出的相位控制信号来预测过采样部7输出的下一次的并行数据的边缘位置,并作为边缘预测位置数据而输出,并且,将相对于边缘预测位置数据偏移了半相位的数据作为采样位置数据而输出。

[0060]

相位比较部44将边缘检测部41输出的边缘数据与边缘位置计算部42输出的边缘预测位置数据进行比较,输出相位控制信号(cntup,cntdn)。数据采样部43根据边缘位置计算部42输出的采样位置数据从过采样部7输出的并行数据中提取数据,即,如图6所示,对数据中心进行采样,作为恢复数据(再生数据),与表示数据有效性的数据使能rdata_en一起输出。

[0061]

并且,例如,由比特变换电路5基于数据使能rdata_en使从dr电路4输出的2比特的信号成为1比特的信号,从比特变换电路5对兼容通信控制电路2输出160mhz的1比特信号。这样,控制装置10能够在数据发送以及数据接收的双方中,使用相同的serdes来进行不同通信速率(不同规定)的数据传输。dr电路4和比特变换电路5仅是一例,能够进行各种变更和变形,另外,能够应用公知的各种电路。

[0062]

图7用于说明图3所示的serdes接口电路的另一应用例。在此,图7的(a)是表示serdes接口电路的另一应用例的框图,图7的(b)用于说明图7的(a)所示的serdes接口电路中的输出状态机的动作。此外,图7的(a)的结构实质上与上述的图3的(a)相同,省略其说明。

[0063]

上述的图3和图4表示了将基于180mhz的时钟的16比特并行数据和基于160mhz的时钟的1比特信号经由serdes7变换为2.88gbps的串行数据来传输给对方装置200时的serdes接口电路的应用例,图7和图8表示将基于120mhz的时钟的18比特并行数据和基于90mhz的时钟的1比特信号经由serdes7变换为2.16gbps的串行数据来传输给对方装置200时的serdes接口电路3的应用例。

[0064]

输出状态机33使用输入到端子a的信号(a:fifo输出)和输入到端子b的信号(b:ff输出),生成例如在串行数据中24比特相同的数据连续(具有相同的逻辑值)的并行数据,其中,上述端子b是在1个时钟之前的定时取入上述信号(a)并保持该信号(a)的触发器的输出。从该输出状态机33(ser des接口电路3)输出的信号对应于从新通信控制电路1输出的120mhz的18比特的并行数据。

[0065]

即,如图7的(b)所示,输出状态机33从信号a以及信号b生成具有24比特相同的逻辑值的并行数据,例如状态“1”的数据“b”是由触发器32通过前1个时钟取入的数据,因此具有与状态“0”的数据“a”相同的逻辑值。因此,通过对状态“0”的数据“a”的18比特的并行数据加上状态“1”的数据“b”的6比特的并行数据,来生成具有24比特相同的逻辑值的18比特的并行数据。

[0066]

同样地,例如,通过对状态“1”的信号a的12比特的并行数据加上状态“2”的信号b的12比特的并行数据,生成具有24比特相同的逻辑值的18比特的并行数据。另外,由于状态“2”的en为“0”,因此在状态“3”下fifo31的输出不被更新,将输入到状态“2”的“a”和状态“3”的“b”的数据的下一个的fifo31的输出数据输入到状态“0”的“a”和状态“1”的“b”。这样,例如,将来自兼容通信控制电路2的90mhz的1比特信号在从状态“0”到状态“3”之间处理3比特,反复进行该处理。

[0067]

图8用于说明图7所示的serdes接口电路的动作。如上所述,作为发送并行数据tx_pdata,通过加入由serdes接口电路3(输出状态机33)生成的“111111111111111111”这样的连续的相同数据,能够降低实质的通信速率。

[0068]

即,如图8所示,例如,在以2.16gbps的通信速率发送120mbps的信号时,为了以相同的serdes7(相同的通信速率)发送90mbps的1比特的信号,因为2.16g/120m=24,所以将90mbps的1比特的信号变换为24比特相同的数据连续的并行数据并输入到serdes7即可。

[0069]

由此,serdes接口电路3(输出状态机33)输出120mhz的18比特并行数据,由于90mbps的1比特所对应的数据成为使相同逻辑值连续了24比特的并行数据,因此实际上降低发送串行数据tx_sdata的通信速率来进行数据传输。由此,能够使用相同的serdes7进行不同通信速率的数据传输。

[0070]

在此,在输出状态机33生成的并行数据(18比特并行数据)中,在将与第一发送数据(90mhz的1比特的信号)对应的相同数据连续的比特数设为v(24),将第一时钟的频率设为w(90mhz),将第二时钟的频率设为x(120mhz),并且将基于第二时钟的第二发送数据中的并行数据的比特数设为y(18)时,相同数据连续的比特数v能够通过v=(x

×

y)/w来表示。

[0071]

图9用于说明图1所示的控制装置中的serdes接口电路的变形例。在此,图9的(a)是表示serdes接口电路的变形例的框图,图9的(b)用于说明图9的(a)所示的serdes接口电路中的输出状态机的动作。另外,根据图9的(a)与图3的(a)和图7的(a)之间的比较可知,在本变形例的serdes接口电路3中,使具有输出使能的fifo31为具有输出数量控制功能的fifo31’,与此对应地使输出状态机33为输出状态机33’。并且,在本变形例中,示出了将基于80mhz的时钟的16比特并行数据和基于128mhz的时钟的1比特信号经由serdes7变换为1.28gbps的串行数据来传输给对方装置时的serdes接口电路3的应用例。

[0072]

如图9的(a)所示,fifo31’接收频率为128mhz的输入用时钟(第一时钟)、基于128mhz的时钟的1比特的信号(工作频率为128mhz的发送数据:第一发送数据)、以及频率为80mhz的输出用时钟(第二时钟),基于第一时钟取入第一发送数据,并基于第二时钟按顺序输出所取入的数据。将fifo31’的输出(第一fifo输出)o1作为信号a输入到输出状态机33’,将输出(第二fifo输出)o2作为信号b输入到输出状态机33’,并且输入到触发器32的数据端子。

[0073]

并且,fifo31’通过输出数量控制端子out_num接收从输出状态机33’输出的输出数量控制信号next_num。在本变形例中,例如,为了经由通信速率1.28gbps的serdes7发送80mhz的16比特并行数据和128mhz的1比特的信号,因为1.28g/128m=10,所以将128mhz的1比特的信号变换为10比特相同的数据连续的并行数据来输入给serdes7即可。

[0074]

图10用于说明图9所示的serdes接口电路中的具有输出数量控制功能的fifo,图10的(a)表示out_num=1的情况,图10的(b)表示out_num=2的情况。

[0075]

首先,如图10的(a)所示,在out_num=1的情况下,将最初输入并存储的数据(最初输出的数据:fifo的“1”中存储的数据)输出到输出(第一fifo输出)o2,对输出(第二fifo输出)o1不进行任何输出。接着,如图10的(b)所示,在out_num=2的情况下,将fifo的“1”中存

储的数据输出到输出o1,并且将fifo的“2”中存储的数据(“1”之后输出的数据)输出到输出o2。由此,与上述参照图3以及图4说明的例子以及参照图7以及图8说明的例子同样地,能够使用相同的serdes7进行不同的通信速率(不同规格)的数据传输。

[0076]

即,如图9的(b)所示,输出状态机33’根据端子a的信号(a:o1)、端子b的信号(b:o2)以及端子c的信号(c:触发器32的输出信号)生成10比特相同的数据连续的并行数据。在此,在图9的(b)中,例如,状态“1”的数据“c”是由触发器32通过前1个时钟取入了输出o2的数据,因此具有与状态“0”的数据“b:o2”相同的逻辑值。因此,不仅生成状态“0”的数据“a”的10比特相同的数据连续的并行数据,还生成对状态“0”的数据“b”的6比特的并行数据加上状态“1”的数据“c”的4比特的并行数据而得到的具有10比特相同的逻辑值的并行数据。

[0077]

关于该具有10比特相同的逻辑值的并行数据的生成,例如也能够通过对状态“2”的数据“b”的8比特的并行数据加上状态“3”的数据“c”的2比特的并行数据来同样地生成。这样,通过从输出状态机33’输出的输出数量控制信号next_num来控制fifo31’的输出o1和o2,由此能够进行同样的处理。

[0078]

即,根据来自输出状态机33’的控制信号控制fifo31’不输出第一fifo输出(o1)而仅输出第二fifo输出(o2),或者输出第一fifo输出(o1:“1”的数据)并作为第二fifo输出(o2)输出第一fifo输出的下一个按顺序要输出的数据(“2”)。此外,上述的serdes接口电路3仅是示例,并且可以进行各种变更和变形。

[0079]

在此,在输出状态机33’生成的并行数据(16比特并行数据)中,在将与第一发送数据(128mhz的1比特的信号)对应的相同数据连续的比特数设为v(10),将第一时钟的频率设为w(128mhz),将第二时钟的频率设为x(80mhz),并且将基于第二时钟的第二发送数据中的并行数据的比特数设为y(16)时,相同数据连续的比特数v能够通过v=(x

×

y)/w来表示。

[0080]

至此对实施方式进行了说明,在此记载的全部的例子、条件是为了帮助理解在发明以及技术中应用的发明概念,特别是所记载的例子、条件并不意图限制发明的范围。另外,说明书的这样的记载也不是表示发明的优点和缺点。虽然详细记载了发明的实施方式,但应该理解能够在不脱离发明的精神和范围的情况下进行各种变更、置换、变形。

[0081]

符号说明

[0082]

1 新通信控制电路

[0083]

2 兼容通信控制电路

[0084]

3 serdes接口电路

[0085]

4 数据恢复(dr)电路

[0086]

6 选择器

[0087]

7 serdes(串行器/解串器)、过采样部

[0088]

10 控制装置

[0089]

31 fifo(具有输出使能的fifo)

[0090]

31

’ꢀ

fifo(具有输出数量控制功能的fifo)

[0091]

32 触发器(ff)

[0092]

33、33

’ꢀ

输出状态机

[0093]

41 边缘检测部

[0094]

42 边缘位置计算部

[0095]

43 数据采样部

[0096]

44 相位比较部

[0097]

100 本装置(控制装置)

[0098]

200 对方装置。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1