一种跨多倍频程的数字延时线电路及其数字延时方法

本发明涉及信号处理,尤其涉及一种跨多倍频程的数字延时线电路和其数字延时方法。

背景技术:

1、现代通信标准为了满足高速率应用要求,必须采用高峰均比调制,以实现有限带宽的充分利用,开关式功率放大器可以直接由数字电路驱动,比传统的线性放大器效率更高。这种类型的发射机除了具有灵活性和效率外,更适合在芯片上实现纳米级的cmos技术,这对于降低成本和尺寸十分重要。开关类功放的发展为数字射频前端技术提供了一种高效率的解决方案,即数字射频发射机。数字射频技术的出现,为低功耗的目标提供实际理论基础和可行方案。相位调制器作为数字射频前端的重要组成模块,承担着调制基带相位信息到射频载波的关键作用,其性能好坏直接决定发射信号的质量,从而影响pa及滤波器等模拟器件的设计复杂度。

2、当前,会通过锁相环的闭环提供准确的相对延时精度,使电路具备在不同的pvt(工艺、电压、温度)下高性能工作的能力。

3、参考图1,常用的一种数字相位调制为基于全数字锁相环(all-digital phaselocked loop,adpll)的闭环相位调制。基于adpll的闭环相位调制的原理如下:闭环锁相环的分频比由数据频率控制字与载波频率控制字共同控制,分频的信号与参考频率通过鉴频鉴相器进行对比,所得到的相位差被注入电荷泵,并经过低通滤波器后转换为电压,作为振荡器的控制输入,实现频率调节,该路径为锁相环的低通路径;在高通路径上,数据频率控制字被(digital-analog converter,dac)直接转换为电压信号,加载在振荡器的输入端。但是该相位调制系统对振荡器的非线性十分敏感,限制了adpll调制宽带信号的能力,在有多个相位支路的发射机电路中需要多个adpll,即造成面积功耗的浪费,又可能引起注入牵引的问题。

4、基于数字延时线(digital delay line)的调制器使全数字发射机的研究热点,数字延时线本质上是数字时间转换器(digital to time converter,dtc),通过控制码的不同输出相应的延时波形,基于数控延时链的相位调制器已被应用于各种发射机结构中。但是该电路使用dac将数字控制字转换为模拟信号加载在振荡器的输入端,增加了系统设计的复杂度。

技术实现思路

1、鉴于上述的分析,本发明实施例旨在提供一种跨多倍频程的数字延时线电路和方法,用以解决现有相位调制系统在有多个相位支路的发射机电路中需要多个adpll导致面积功耗的浪费以及dac将数字控制字转换为模拟信号加载在振荡器的输入端,增加了系统设计的复杂度等的问题。

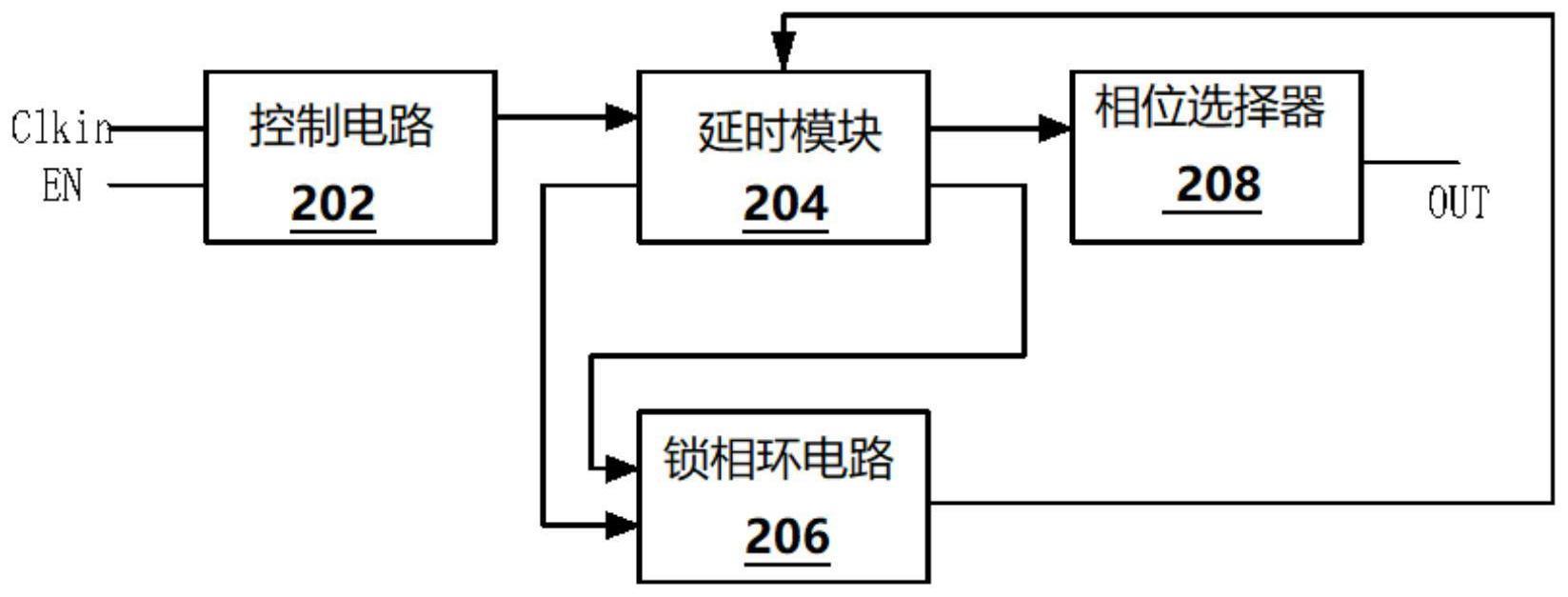

2、一方面,本发明实施例提供了一种跨多倍频程的数字延时线电路,包括:控制电路、延时模块、锁相环电路和相位选择器电路,其中,所述控制电路,用于根据输入的待延时时钟信号的频率信息选择所述延时模块中的延时路径;所述延时模块,用于基于选择的延时路径对所述待延时时钟信号进行延时以生成多个具有不同相位的输出时钟信号,其中,所述多个具有不同相位的输出时钟信号包括延时一个周期的输出时钟信号;所述锁相环电路,用于将所述待延时时钟信号和所述延时一个周期的输出时钟信号进行鉴频鉴相并将鉴频鉴相的信息转换为电压信号,并将所述电压信号反馈到所述延时模块的控制电源;以及所述相位选择器电路,用于对所述多个具有不同相位的输出时钟信号进行选择以获取目标延时时钟信号。

3、上述技术方案的有益效果如下:本技术实施例的数字延时线电路不需要dac和多个adpll,减小了面积功耗和设计复杂度。在闭环回路中将延时模块的输入待延时时钟信号和通过整个延时模块的输出时钟信号进行鉴频鉴相,并将鉴频鉴相的信息转化成电压信号反馈到延时模块的控制电源形成闭环,以获得准确的相对延时精度。

4、基于上述装置的进一步改进,所述控制电路包括幅相控制算法模块和多种组合控制逻辑单元,其中,所述幅相控制算法模块,用于检测输入的待延时时钟信号的频率信息,并将所述频率信息转化为对应的数字控制字;以及所述多种组合控制逻辑单元,用于将所述数字控制字转化为控制使能信号,以控制所述延时模块中的不同延时路径的通断。

5、基于上述装置的进一步改进,所述延时模块包括多个延时路径,以及所述频率信息包括不同频率范围,其中,所述多个延时路径分别对应于所述不同频率范围的待延时时钟信号的延时,并根据所述数字控制字将所述待延时时钟信号分配至对应的延时路径以进行时间延时。

6、基于上述装置的进一步改进,所述延时模块还用于在工作状态下使所述多个延时路径中的一个延时路径运行。

7、基于上述装置的进一步改进,所述延时路径包括串联连接的多个延时单元,其中,所述延时单元,用于对输入时钟信号进行最小单位的时间延时,并且通过每个延时单元后产生具有对应相位信息的时钟信号。

8、基于上述装置的进一步改进,所述锁相环电路包括鉴频鉴相模块、电荷泵模块和电流电压转换模块,其中,所述鉴频鉴相模块,用于将所述待延时时钟信号的频率和相位与延时后的输出时钟信号的频率和相位进行比较;所述电荷泵模块,用于将比较后的频率和相位信息转换为电流信号;以及所述电流电压转换模块,用于将所述电流信号转换为电压信号并将所述电压信号反馈到所述延时单元的控制电源以形成闭环回路。

9、基于上述装置的进一步改进,所述闭环回路用于根据反馈到所述延时单元的控制电源的电压信号调节所述延时模块的延时量,并且所述延时单元的控制电源电压越高,延时量就越低。

10、基于上述装置的进一步改进,所述相位选择器电路包括多种组合选择逻辑单元,其中,所述多种组合选择逻辑单元,用于对所述多个具有不同相位的输出时钟信号进行选择以获取具有相应相位的目标延时时钟信号。

11、另一方面,本发明实施例提供了一种跨多倍频程的数字延时方法,包括:根据输入的待延时时钟信号的频率信息选择所述延时模块中的延时路径;对所述待延时时钟信号进行延时以生成多个具有不同相位的输出时钟信号;将所述待延时时钟信号和所述输出时钟信号进行鉴频鉴相并将所述鉴频鉴相的信息转换为电压信号,并将所述电压信号反馈到所述延时模块的控制电源;以及对所述多个具有不同相位的输出时钟信号进行选择以获取目标延时时钟信号。

12、基于上述方法的进一步改进,根据输入的待延时时钟信号的频率信息选择所述延时模块中的延时路径进一步包括:检测输入的待延时时钟信号的频率信息,并将所述频率信息转化为对应的数字控制字;以及将所述数字控制字转化为控制使能信号,以控制所述延时模块中的不同延时路径的通断。

13、与现有技术相比,本发明至少可实现如下有益效果之一:

14、1、本技术实施例的数字延时线电路不需要dac和多个adpll,减小了面积功耗和设计复杂度。在闭环回路中将延时模块的输入待延时时钟信号和通过整个延时模块的输出时钟信号进行鉴频鉴相,并将鉴频鉴相的信息转化成电压信号反馈到延时模块的控制电源形成闭环,以获得准确的相对延时精度。

15、2、本技术实施例的数字延时线电路具有多倍频程的频率范围覆盖、准确的相对延时精度的优点,适用于数字射频发射机中进行相位调制;

16、3、控制电路通过检测输入待延时时钟信号的频率信息,将其转化为数字控制字对延时模块中的延时路径进行选择;

17、4、相位选择器电路对延时模块产生的具有不同相位信息的多个输出时钟信号进行选择,得到目标输出延时时钟信号。

18、本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

- 还没有人留言评论。精彩留言会获得点赞!