一种用于高精度SARADC的电容阵列权值校准方法

一种用于高精度sar adc的电容阵列权值校准方法

技术领域

1.本发明涉及模数转换器、lms自适应算法、电容阵列排序算法和数字校准技术,特别是将前台的排序重组算法与后台的lms自适应算法相结合,以及对lms算法应用在单通道、单次采样两次转换、具有固定偏置注入情景下,能够很好地校准adc的线性和非线性误差。

背景技术:

2.adc,analog-to-digital converter的缩写,指模数转换器。是指将连续变化的模拟信号转换为离散的二进制数字信号的器件。真实世界的模拟信号,如温度、压力、亮度或磁场强度等在通过传感器转换成模拟电压量后,需要通过adc进一步转换成数字信号以便于存储、处理和传输。

3.对于中高精度的saradc而言,电容阵列的失配是误差的主要来源,将失配误差进行校准可以有效提高adc的性能。而利用数字域的校准方法,相比于模拟校准技术具有成本低和效果好的特点,是现行校准技术的主流。

4.传统的lms算法采用双通道对比的方式进行权值收敛,优点是可以采用分裂电容阵列的方式,使得在同样的电容大小开销情况下,adc整体分裂为两个单位电容较小的通道了,这样每个单独通道的电容失配更严重但是没有额外的模拟硬件开销,利用lms算法校准后结果也能达到预期;缺点是双通道容易收敛到局部最小值而非全局最优解,因此,需要利用较为复杂的算法来适应和避免落入局部最优解,片上实现难度较高。另一种解决方法是,额外使用一个精度较高的参考通道,这时lms算法的收敛效率较高,数字运算可以适当简化,将运算过程的数采用二进制形式表示可以大大简化数字电路的复杂性,但仍面临收敛速度和精度上的矛盾。

技术实现要素:

5.本发明解决现有技术上的精度与速度上的矛盾问题,提供一种用于单通道的saradc电容阵列失配校准方案,提高收敛速度和准确性,同时规避了分离式adc并行通道之间的时钟偏斜和带宽不匹配问题。

6.本发明解决上述技术问题的技术方案如下:一种用于高精度sar adc的电容阵列权值校准方法,包括如下步骤:

7.步骤1:使用电容重组校准的方法,对高位电容阵列进行初步校准,具体步骤如下:

8.步骤1.1:使用sar adc的比较器和开关,对高位电容的单位电容进行排序,得到排序结果;

9.步骤1.2:将排序的中位电容作为二进制电容阵列对应的位,之后其它电容按照排序的结果进行首尾合并组成新的电容阵列,再对新电容阵列进行排序;

10.步骤1.3:重复步骤1.2直到中位电容成为二进制电容阵列的次高位,剩余电容合并后作为电容阵列的最高位,此时电容阵列重组完成;

11.步骤2:利用重组后的电容阵列,进行后台校准:

12.步骤2.1:对输入信号进行采样,采样完成后将电容阵列中用于注入固定偏置的电容接低电平,之后进行模数转换,得到数字码dout1并保存;

13.步骤2.2:重置电容阵列的开关,并将用于注入固定偏置的电容接高电平,再次进行模数转换,得到数字码dout2并保存;

14.步骤2.3:计算两次转换结果的数字码权值:

15.步骤2.3.1:计算两次转换差值:dx=dout1

×

weight

t

–

dout2

×

weight

t

+dither,

16.其中,weight=[w1,w2,w3,

···

,wn],wi为电容阵列对应位置i的权值大小,dither 为注入固定偏置的电容的权值大小;

[0017]

步骤2.3.2:对转换结果的差异位权值进行修改,迭代公式为:

[0018]

weight(i)=weight(i)

–

dx

×u×

(dout1(i)

–

dout2(i)),其中u为权值收敛系数,weight(n)表示weight中的第i个元素,dout1(i)表示dout1中的第i个元素;

[0019]

步骤2.3.3:对固定偏置注入位进行校准,迭代公式为:

[0020]

dither=dither+sign(dx)

×

k,其中k为固定偏置量的校准系数,sign表示取符号的数学运算符。

[0021]

本发明方法采用前台校准与后台校准方法相结合,先用电容重组算法对高位二进制电容阵列进行重组,再利用后台校准逼近最优解。其中后台校准采用单次采样两次转换的方式,与传统的双通道lms算法相比,不需额外的dac作为参考,而只需单个通道在相同的周期内进行更多次比较,将硬件上的开销转移到时序要求上,并利用固定偏置注入使得两次转换数字码不同,达到精度与速度的双重提高。

附图说明

[0022]

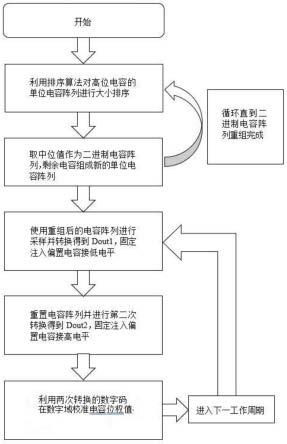

图1为本发明的整体算法流程示意图。

[0023]

图2为本发明的后台校准具体计算流程示意图。

[0024]

图3为本发明的电容重组算法原理示意图。

[0025]

图4为本发明提出的16位adc的电容阵列示意图。

[0026]

图5中(a)为传统的排序算法结果,(b)为本发明方法进行300次蒙特卡洛sfdr仿真结果。

[0027]

图6中(a)为传统的排序算法结果,(b)为本发明方法进行300次蒙特卡洛sndr仿真结果。

[0028]

图7中(a)为直接使用后台校准的误差收敛图,(b)为本发明完整方法的误差收敛图。

[0029]

图8为传统方法校准后的误差收敛图。

[0030]

图9为本发明校准方法后的误差收敛图。

具体实施方式

[0031]

以下对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

[0032]

如图1所示流程,adc在正式工作前,先利用电容重组算法对高位电容的单位电容

进行重组。

[0033]

电容重组算法具体流程如图3所示,将高位电容分割成合适大小的单位电容,如:2的n 次方倍的最小单位电容等,这样既方便比较大小,又可以减少比较次数,还能降低对比较器的精度要求。之后利用排序算法,如:冒泡排序算法,对单位电容进行大小排序并将排序结果以标记的形式存放在数字电路中,则当实际adc工作需要操作到高位电容时,可根据电容重组算法运行结果操作到对应的单元电容,如图3中,在adc工作前先对高位的单位电容进行排序,之后结合大小排序的结果得到中位值并将剩余电容进行重组,重复排序和重组步骤最终可得到一个二进制电容阵列。实际转换时只需操作算法运行结果对应的重组位即可,以此类推。这样经过重组后的高位的失配误差情况会大大改善。

[0034]

然后,如图1所示流程,adc在工作状态下开启后台校准模式,即在正常工作周期内,完成后台校准。

[0035]

具体计算流程如图2所示,首先adc对输入信号进行采样,然后在偏置电容接低的条件下对输入信号进行转换得到dout1,其中dout1以位的形式存放,如第一位(msb)接高时比较器结果为1则dout1的第一位为1,反之为0;dout1的第二位则存放msb-1位的比较器结果,以此类推。转换完成后重置电容阵列的开关,并将偏置电容接高,进行第二次转换,得到dout2 与第一次转换同理。然后将两次转换的结果换算成权重值,则第一次转换的权值为dout1

×ꢀ

weight,其中weight为电容阵列对应的电容权重值,初始值为理想权值;第二次转换的权值为dout2

×

weight

–

dither,其中dither为偏置注入电容的理想权值。这里引入了一个固定偏置,使得两次转换虽然是对同一次的采样信号进行转换,理应得到相同的结果,实际确是得到不同的转换结果。固定偏置加上一定量的冗余电容可以使得第二次转换与第一次相比被校准的位的转换结果必定不同。接下来计算出两次转换实际结果的差值dx,然后根据dx的结果对位权值weight进行迭代。显而易见的是,两次转换中结果相同的位对dx并无影响,故只需对转换结果不同的位的权值进行修改:假设dout1为10100,dout2为10011,则第一第二位结果相同,失配值无法在dx中体现出来,因此本次转换只对第三、四、五位进行修改,修改方法如下:对于第三位,第一次的结果为1而第二次的结果为0,若dx大于0,则需要将第三位的权值改小,同理需将第四、五位的权值改大,使dx在迭代中逐渐减小。具体迭代公式为:weight(n)=weight(n)

–

dx

×u×

(dout1(n)

–

dout2(n)),其中u为收敛系数, u越大收敛速度越快但容易使得修改过度,导致dx的值发生振荡;u越小收敛速度越慢,选择合适的u值可以使dx在适合的转换次数下稳定地减小到合适的范围,本发明u为2的n次方使数字电路的运算难度大大降低。之后由于偏置电容同样存在失配,需要对其进行校准,校准方法也很简单,判断dx是否大于0,取dx的符号,即sign(dx),乘以一个较小的振荡系数k,迭代公式为:dither=dither+sign(dx)

×

k,则当迭代次数足够时,可以保证dither 的量在准确值附近振荡,即偏置注入电容的失配也得到校准。最后,adc的输出结果为:dout1 和(dout2-dither)的平均值,可以使得校准次数未达到一定程度前的adc输出结果有所改善,在校准到dx的值小到一定程度后,两者取平均值也不影响校准结果。

[0036]

综上所述,利用电容重组算法去校准高位电容阵列,具有高效快速的特点,能够帮助算法更快地收敛,节约大量时间,之后再进一步利用算法后台运行的优点,将精度进一步提升。

[0037]

本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本

发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

[0038]

实施例

[0039]

对单独传统的排序算法以及本发明提出的排序算法结合后台校准两种方案进行 matlab仿真,仿真的单位电容失配值取0.003,电容失配按正态分布进行仿真,蒙特卡洛仿真次数为300次,仿真结果得到排序算法与排序算法和后台校准相结合的sfdr 分布情况对比,电容重组算法与电容重组算法和后台校准相结合的sndr分布情况对比,结果如图4、5所示,对结果进行总结得到下表:

[0040][0041]

以下使用一组数据作为实施例展示本发明提出的算法的收敛速度与普通的单通道两次转换lms算法收敛速度对比:

[0042]

高位电容阵列数据为:

[0043]

cp_msb=[16.1716,15.939,16.0764,16.1572,16.1099,16.0564,16.2613, 16.0411,15.8322,16.0607,16.1498,15.8721,15.7693,16.0428,15.8459, 8.0002,3.9912,4.0129,2.0038,1.0010,1.0013,0.9926];

[0044]

cn_msb=[15.9055,16.4575,15.7683,16.1562,15.8322,16.087,16.0084, 15.6583,16.2023,15.4488,16.1401,15.8733,16.0445,15.9865,16.0782, 8.0071,4.0177,3.9029,1.9632,1.0003,1.0011,1.0021];

[0045]

该电容阵列直接作为adc的电容阵列对输入的正弦波进行转换得到的数据的enob、 sfdr、sndr分别为:9.4566、64.1694和58.6880;运行前台排序校准和后台校准(4096 个周期)后的enob、sfdr、sndr分别为:15.6955、112.3802、96.2469,特别地,在使用排序算法前和使用排序算法后的误差收敛图如图7所示,可以看到运行排序算法后,本发明方法误差初值小且收敛速度更快。

[0046]

同时,为了更进一步体现本发明与传统lms算法收敛速度的区别,使用matlab 模拟实际电容阵列失配,仿真的单位电容失配值取0.003,电容失配按正态分布进行仿真,蒙特卡洛仿真次数为100次,将100次仿真的收敛图像叠加得到图8和图9,图8展示了传统的单通道两次转换的误差收敛图,图9则展示了使用本发明校准方法后的误差收敛图。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1