一种基于TGV工艺的小型化滤波器设计方法与流程

一种基于tgv工艺的小型化滤波器设计方法

技术领域

1.本发明涉及小型化滤波器技术领域,尤其涉及一种基于tgv工艺的小型化滤波器设计方法。

背景技术:

2.ipd滤波器由于其工艺特点,电感在整个版图中占据绝大多数的面积,由于ipd平面电感的特点随着面积的减小必然需要减小电感走线宽度及空心率,这样就造成电感损耗偏大、电感q值也变差,这就给ipd无源器件的小型化提高了难度,另外现阶段对滤波器的电性能要求越来越高,对ipd器件更是一种挑战。

3.由上所述,为此我们设计出了一种基于tgv工艺的小型化滤波器设计方法来解决以上问题。

技术实现要素:

4.本发明的目的是为了解决现有技术中存在的缺点,而提出的一种基于tgv工艺的小型化滤波器设计方法。

5.为了实现上述目的,本发明采用了如下技术方案:

6.一种基于tgv工艺的小型化滤波器设计方法,包括滤波器本体,所述滤波器本体包括电感和电容拆分结构,所述电容拆分结构包括电容,主要包括以设计步骤:

7.s1、组装时,将电容融合到电感中去并根据需要将大电容拆分放置;

8.s2、对两个电感之间的位置和方向进行调节,两个电感为l1和l2;

9.s3、在两个电感之间的角度进行改变时,对耦合系数进行计算,得出两个电感之间的耦合系数k;

10.s4、对步骤s2中不同方式摆放下的两个电感之间的耦合系数k进行对比,得出最大的耦合系数k~;

11.s5、根据最大的耦合系数k~来确定两个电感之间的最终摆放位置。

12.优选的,所述滤波器本体包括高阻硅、玻璃、砷化镓材料中的一种或多种,所述滤波器本体为3d inductor工艺制成。

13.优选的,所述步骤s3中,两个电感l1和l2的摆放位置为并排放置、正对放置和垂直放置中的一种。

14.优选的,所述并排放置和正对放置包括电流方向相同设置和电流方向相反设置。

15.优选的,步骤s3中,耦合系数计算公式为:k=m/√(l1l2)。

16.与现有技术相比,本发明的有益效果是:本发明利用tgv电感之间不同的摆放位置可以调整两个电感之间的耦合特点,在设计时根据需要控制各电感之间的耦合,并利用在版图布局时电容对tgv电感影响很小的特点将电容拆分融合到电感区域,进而设计生产出小型化、高性能的ipd滤波器。

附图说明

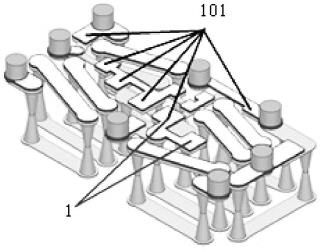

17.图1为带通滤波器的原理图;

18.图2为实施例一种tgv电感两两之间的摆放方式示意图;

19.图3为原理图得到的滤波器传输曲线对比图;

20.图4为有无电感耦合传输曲线对比图;

21.图5为planar ipd滤波器的结构示意图

22.图6为本发明提出的一种基于tgv工艺的小型化滤波器设计方法的tgv ipd滤波器的结构示意图。

23.图中:1电容拆分结构、101电容。

具体实施方式

24.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

25.实施例一

26.参照图6,一种基于tgv工艺的小型化滤波器设计方法,包括滤波器本体,滤波器本体包括电感和电容拆分结构1,电容拆分结构包括电容101,主要包括以设计步骤:

27.s1、组装时,将电容融合到电感中去并根据需要将大电容拆分放置;

28.s2、对两个电感之间的位置和方向进行调节,两个电感为l1和l2;

29.s3、参照图2,在两个电感之间的角度进行改变,对耦合系数进行计算,主要包括以下几种摆放设置方式(a:两电感并排放置(电流方向相同);b:两电感并排放置(电流方向相反);c:两电感正对放置(电流方向相同);d:两电感正对放置(电流方向相反);e:两电感垂直放置):

30.摆放a:电感l1和l2的电磁场存在部分重叠并且方向相同,两电感的耦合系数k约为0.1~0.2;

31.摆放b:电感l1和l2的电磁场存在部分重叠但是方向相反,两电感的耦合系数k约为-0.1~-0.2;

32.摆放c:电感l1和l2的电磁场相对并且方向相同,两电感的耦合系数k约为0.3~0.6;

33.摆放d:电感l1和l2的电磁场相对但是方向相反,两电感的耦合系数k约为-0.3~-0.6;

34.摆放e:电感l1和l2的电磁场垂直,两电感的耦合系数k约为《0.05;s4、对步骤s2中不同方式摆放下的两个电感之间的耦合系数k进行对比,得出最大的耦合系数k~:从耦合方面来说c\d耦合最大;a\b次之;e最小;

35.s5、根据最大的耦合系数k~来确定两个电感之间的最终摆放位置为c\d的摆放方式。

36.根据tgv电感不同摆放两两之间耦合系数k可以调整的特点,我们可以根据需要有效利用电感之间的耦合以提高电性能。

37.更加具体的是,滤波器本体包括高阻硅、玻璃、砷化镓材料中的一种或多种,滤波器本体为3d inductor工艺制成;

38.其中,步骤s3中,耦合系数计算公式为:k=m/√(l1l2);

39.需要说明的是,图1的原理图我们未考虑电感之间的耦合,在进行layout布局时就得以e的方式摆放电感,这样在布局时就很不灵活而且不利于小型化;

40.通过上述,选择图1原理图中l2\l3,通过仿真优化可以做到有效利用它们之间的耦合,原理图如图3;

41.参照图4,可以看出有电感耦合可以明显改善滤波器低频抑制,所以我们可以通过有效利用电感耦合改善滤波器电性能,其中,实线表示无电感耦合;虚线表示有电感耦合。

42.图5-6为planar ipd和tgv ipd滤波器,从图上可以看出planar ipd的电容不管是放置在电感外部还是内部都会影响电感的电性能(电容会阻碍电感磁场)。而tgv ipd由于电感电磁场的方向不同于planar电感,电容对电感电性能基本无影响,这样我们就可以将电容融合到电感中去并且可以根据需要将大电容拆分放置,这样就可以进一步小型化。

43.综上进行tgv滤波器设计是我们可以通过电感的不同摆放位置控制电感之间的耦合并利用电感之间的耦合改善电性能另外利用电容对电感性能基本无影响的特点将电容拆分融合到电感中去,这样就可以实现小型化、高性能的tgv滤波器。

44.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的设备或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

45.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

46.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1