一种数模混合式低功耗自动增益控制放大器

1.本发明涉及通信领域,具体说的是一种数模混合式低功耗自动增益控制放大器。

背景技术:

2.自动增益控制放大器具有广泛的应用范围。在通信领域,自动增益控制放大器一般位于低通滤波器的后级,模数转换器的前级为了抵消无线电波中衰落现象造成的信号损失问题,它的作用是在输入信号幅值变化范围很大的情况下,将输出信号幅值缩小到一个较小的范围内,从而为后级的电路模块提供合适的输入。对于微弱的输入信号,自动增益控制放大器增加放大倍数,使得输出信号满足 adc的量化要求;对于较大的输入信号,自动增益控制放大器的增益减小为负的增益以消减信号的幅度。另外,自动增益控制放大器也广泛应用于有线通信、硬盘读取,雷达、激光等系统中。

3.然而随着科技不断的进步,消费的不断的升级,传统的自动增益运算放大器并不能满足当今芯片的性能要求。cmos工艺的特征尺寸不断的减小,器件的特征截止频率不断的提高,新的工艺下自动增益控制运放的高集成度、低功耗、低成本是当今研究的热点。

技术实现要素:

4.为解决上述技术问题,本发明提供一种数模混合式低功耗自动增益控制放大器,具有低功耗的优点。

5.为实现上述技术目的,所采用的技术方案是:一种数模混合式低功耗自动增益控制放大器,包括超低功耗4bit可编程运放、峰值检测电路、动态比较器、锁存器和verilog rtl控制模块,信号经过超低功耗4bit可编程运放被输送到峰值检测电路中,峰值检测电路将信号的最高值检测并送入到动态比较器中,动态比较器中有两个提前预置好的参考电压vref1和vref2,峰值电压与参考电压 vref1、vref2相比较,将比较器的结果送入到锁存器中并进行存储,并输出二位二进制码,verilog rtl控制模块根据二位二进制码对超低功耗4bit可编程运放进行增益的加减。

6.进一步,所述的超低功耗4bit可编程运放包括全晶体管式开关矩阵、第一运算放大器opa1和等效电阻;全晶体管式开关矩阵具有四个由verilog rtl控制模块根据二位二进制码控制的总控制开关s0、s1、s2、s3,全晶体管式开关矩阵的输出out与第一运算放大器opa1的输出连接,全晶体管式开关矩阵的输入 in与第一运算放大器opa1的负端相连接,第一运算放大器opa1的正端与外部供电连接,全晶体管式开关矩阵的bias端与等效电阻的一端连接,等效电阻的另一端为信号输入端。

7.进一步,所述的等效电阻为nmos晶体管或pmos晶体管,nmos晶体管或pmos晶体管的栅极与bias端连接,nmos晶体管或pmos晶体管的源极与信号输入端连接,nmos晶体管或pmos晶体管的漏极与第一运算放大器opa1 的负端相连接。

8.进一步,全晶体管式开关矩阵包括晶体管m1~m16、开关sw1~sw15、总控制开关s0、s1、s2、s3;

晶体管m1~m16的栅极与偏置电压bias相连接,输入vin与晶体管m1的源极相连接,晶体管m2的源极与开关sw8的0端和晶体管m1的漏极相连接,晶体管m2的漏极与晶体管m3的源极和开关sw8的1端相连接,晶体管m3的漏极与晶体管m4的源极和开关sw7的0端相连接,晶体管m4的漏极与晶体管m5 的源极和开关sw7的1端相连接,晶体管m5的漏极与晶体管m6的源极和开关 sw6的0端相连接,晶体管m6的漏极与晶体管m7的源极和开关sw6的1端相连接,晶体管m7的漏极与晶体管m8的源极和开关sw5的0端相连接,晶体管m8的漏极与晶体管m9的源极和开关sw5的1端相连接,晶体管m9的漏极与晶体管m10的源极和开关sw4的0端相连接,晶体管m10的漏极与晶体管 m11的源极和开关sw4的1端相连接,晶体管m11的漏极与晶体管m12的源极和开关sw3的0端相连接,晶体管m12的漏极与晶体管m13的源极和开关 sw3的1端相连接,晶体管m13的漏极与晶体管m14的源极和开关sw2的0 端相连接,晶体管m14的漏极与晶体管m15的源极和开关sw2的1端相连接,晶体管m15的漏极与晶体管m16的源极和开关sw1的0端相连接,晶体管m16 的漏极与开关sw1的1端连接;

9.开关sw8的单端与开关sw12的0端相连接,开关sw7的单端与开关sw12 的1端相连接,开关sw6的单端与开关sw11的0端相连接,开关sw5的单端与开关sw11的1端相连接,开关sw4的单端与开关sw10的0端相连接,开关 sw3的单端与开关sw10的1端相连接,开关sw2的单端与开关sw9的0端相连接,开关sw1的单端与开关sw9的1端相连接,开关sw12的单端与开关sw14 的0端相连接,开关sw11的单端与开关sw14的1端相连接,开关sw10的单端与开关sw13的0端相连接,开关sw9的单端与开关sw13的1端相连接,开关sw14的单端与开关sw15的0端相连接,开关sw13的单端与开关sw15的 1端相连接,开关sw15的输出端与out端相连接;

10.总控制开关s0与开关sw1、开关sw2、开关sw3、开关sw4、开关sw5、开关sw6、开关sw7、开关sw8相连接;总控制开关s1与开关sw9、开关sw10、开关sw11、开关sw12相连接;总控制开关s2与开关sw13、开关sw14相连接;总控制开关s1与控制开关sw15相连接。

11.进一步,所述的峰值检测电路包括第二运算放大器opa2、晶体管和电容,晶体管为nmos晶体管或pmos晶体管,第二运算放大器opa2的正端与超低功耗4bit可编程运放的输出相连接,第二运算放大器opa2的输出端与晶体管的栅极相连接,晶体管的源极分别与第二运算放大器opa2的负端电容、峰值检测电路输出端相连接。

12.进一步,所述的verilog rtl控制模块根据二位二进制码对超低功耗4bit可编程运放进行增益的大小调节的具体方法为:设定参考电压vref2》参考电压 vref1,锁存器对比较器的输出存储并输出00、01、11两位二进制码;verilog rtl 模块接收两位二进制码并输出控制码cotrol_code,控制码cotrol_code是一个四位的二进制码,具有初始值;当峰值电压低于参考电压vref1时,锁存器的输出为00,此时,控制码 cotrol_code的数值加1,当峰值电压高于vref2时,锁存器的输出为11,控制码cotrol_code的输出数值减1,当峰值电压位于参考电压vref2、vref2之间时,锁存器的输出为01,控制码cotrol_code的输出数值不变;verilog rtl模块具有四个控制码端口,每一个端口输出一位控制码,从高位到低位依次对应连接总控制开关s3、s2、s1、s0,根据每位控制码的值,总控制开关s3,s2,s1,s0控制各自连接的开关与相应值的端点连接,进行增益的加减。

13.本发明有益效果是:1、本发明提出超低功耗4bit可编程运放、峰值检测电路、动态比较器、锁存器和

verilog rtl模块。这与传统的数字控制的自动增益控制运放相比不需要额外的模数转换器模块来进行信号转换。另外本发明采用了动态比较器与传统的静态比较器相比减少了功耗。因此本发明具有更高的集成度和低功耗的特性。

14.2、提出了一种新型的超低功耗4bit可编程运放,该运放通过运用在线性区的mos管取代了通常的电阻阵列,一方面降低电路的整体功耗,减少了因为电阻带来的热损耗。同时在集成电路把版图设计的时候极大的减小了版图面积,节约了流片成本。

15.3、通过本文对可编程运放的改进,极大的改进了verilog rtl控制模块的复杂度。这样带来的好处是减少了verilog rtl控制模块内数字晶体管的数量,这样可以减少数字模块的整体功耗和版图面积,具有更高的集成度。

附图说明

16.图1为本发明的整体结构图;图2为现有技术运放结构图;图3为本发明超低功耗4bit可编程运放结构图;图4为图3中晶体管深线性区示意图;图5为图3中全晶体管式开关矩阵结构图;图6为本发明峰值检测电路图;图7为传统的并联电阻开关阵列图;图8为本发明增益的加减状态转移图;图9为verilog rtl控制模块流程图;图10为本发明的电路仿真图;图11为本发明峰值检测电路仿真图。

具体实施方式

17.如图1所示,一种数模混合式低功耗自动增益控制放大器,包括超低功耗 4bit可编程运放、峰值检测电路、动态比较器、锁存器和verilog rtl控制模块,信号经过超低功耗4bit可编程运放被输送到峰值检测电路中,峰值检测电路将信号的最高值检测并送入到动态比较器中,动态比较器中有两个提前预置好的参考电压vref1和vref2,峰值电压与参考电压vref1、vref2相比较,将比较器的结果送入到锁存器中并进行存储,并输出二位二进制码,verilog rtl控制模块根据二位二进制码对超低功耗4bit可编程运放进行增益的加减。

18.如图3所示,超低功耗4bit可编程运放包括全晶体管式开关矩阵、第一运算放大器opa1和等效电阻;全晶体管式开关矩阵具有四个由verilog rtl控制模块根据二位二进制码控制的总控制开关s0、s1、s2、s3,替代如图7所示的传统的并联电阻开关阵列,全晶体管式开关矩阵的输出out与第一运算放大器 opa1的输出连接,全晶体管式开关矩阵的输入in与第一运算放大器opa1的负端相连接,第一运算放大器opa1的正端与外部供电连接,全晶体管式开关矩阵的bias端与等效电阻的一端连接,等效电阻的另一端为信号输入端。

19.等效电阻为nmos晶体管或pmos晶体管,nmos晶体管或pmos晶体管的栅极与bias端连接,nmos晶体管或pmos晶体管的源极与信号输入端连接, nmos晶体管或pmos晶体管的漏极与第一运算放大器opa1的负端相连接。

rtl模块具有四个控制码端口,每一个端口输出一位控制码,从高位到低位依次对应连接总控制开关s3、s2、s1、s0,根据每位控制码的值,总控制开关s3,s2,s1,s0控制各自连接的开关与相应值的端点连接,进行增益的加减。

27.例如,控制码cotrol_code的初始值为0100,高位到低位依次为0、1、 0、0,此时对应的总控制开关s3连接的开关sw15的0端闭合,总控制开关s2 连接的开关sw13和开关sw12的1端闭合,总控制开关s1连接的开关sw9、开关sw10、开关sw11、开关sw12的0端闭合,总控制开关s0连接的开关sw1、开关sw2、开关sw3、开关sw4、开关sw5、开关sw6、开关sw7、开关sw8 的0端闭合,当控制码cotrol_code由增加1变为0101,在上述基础上,总控制开关s0连接的开关sw1、开关sw2、开关sw3、开关sw4、开关sw5、开关 sw6、开关sw7、开关sw8变换为1端闭合,当控制码cotrol_code由0100 减1变为0011,在上述基础上,总控制开关s2连接的开关sw13和开关sw12 更换为0端闭合,总控制开关s1连接的开关sw9、开关sw10、开关sw11、开关sw12更换为1端闭合,总控制开关s0连接的开关sw1、开关sw2、开关sw3、开关sw4、开关sw5、开关sw6、开关sw7、开关sw8更换为1端闭合,控制码cotrol_code最大增至1111,最小减至0000。

28.图1是可编程运放的整体电路,图2是传统的反比例运放的结构,根据运放的虚短的原理可以知道其输出为:同样的设计图3中的m1可以看作一个深线性区的等效电阻r

m1

,因此这其他mos管可以看作是其整数倍的电阻。所以整个电路的输出可以表示成其中式中的n是二进制控制码所对应的十进制数。

29.图4是图3中晶体管工作在线性区的示意图,晶体管工作在深线性区源漏通道之间可以用一个线性电阻表示,该电阻等于其中,v

gs

为晶体管栅源电压,v

th

晶体管阈值电压,为晶体管宽长比,c

ox

为晶体管栅氧层电容,un为电子真空迁移速率,v

ds

为晶体管漏源电压,晶体管可以看作为一个阻值由过驱动电压控制的电阻,只要v

ds

≤2(v

gs-v

th

),通过控制合适的偏置电压以及宽长比,既可以得到合适的等效电阻。超低功耗4bit可编程运放采用了全晶体管使得反馈模块来替代纯电阻模块其示意图如图5,晶体管替代了电阻。其控制原理是:使用了单刀双掷开关进行逻辑的控制,当输入控制码是 0000的时候,则s0中的所有的单刀双掷开关0端闭合,s1、s2、s3的连接所有开关0端被闭合,因此输入信号只会从s3中的sw15的0端口输入到s2中的sw14 的0端口输入到s1中的sw12,经过sw12信号会进入到s0中的sw8中,因为 sw8是打开的因此sw8的0端打开,因此信号将会流经两个线性区的mos管 m1管。

30.当输入的控制码是0001时,s0中的单刀双掷开关的1端闭合,s1、s2、 s3的0端被闭

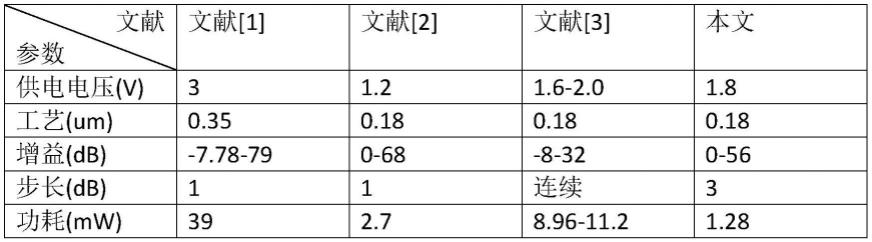

with integrated rssi function[j].ieee journal of solid-state circuits,2005, 40(6):p.1249-1258.[2]姚红燕.数字辅助直流失调消除的自动增益控制电路设计[d].东南大学, 2016.[3]tacconi e j,christiansen c f.a wide range and high speed automatic gain control[c]//particle accelerator conference.ieee,1993。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1