一种新型鉴频鉴相器电路的制作方法

1.本发明属于集成电路设计领域,具体涉及一种新型鉴频鉴相器电路。

背景技术:

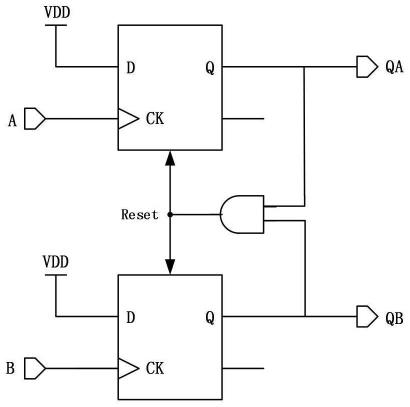

2.鉴频鉴相器是一种将两种输入信号相比较,既能检测相位差,又能检测频率差的电路,可用作脉冲发生器。鉴频鉴相器是锁相环中的关键模块。锁相环是集成电路中的通用模块。在收发机系统中,锁相环可以用来产生本振信号,实现信号的调制和解调;在模拟电路中,锁相环可以用来产生高精度时钟作为模数转换器等元件的输入。

3.随着锁相环的应用越来越广泛,对鉴频鉴相器的要求也越来越高。参照图1,传统的鉴频鉴相器电路包括两个d触发器和一个与门,至少需要38个晶体管,使用晶体管数目多,占用芯片面积大,功耗大;且传统鉴频鉴相器电路输出信号qb的脉冲宽度约为5级门延迟,关键路径延迟时间长,鉴频鉴相精度较低。

技术实现要素:

4.本发明的目的在于针对上述现有技术的不足,提供一种新型鉴频鉴相器电路,旨在减小晶体管使用数目,从而减小占用芯片面积,降低功耗;减小关键路径延迟时间,从而提高鉴频鉴相精度。

5.为了实现上述目的,本发明包括:第一控制模块1、第一逻辑门模块2、第二控制模块3和第二逻辑门模块4;

6.所述第一控制模块1设有四个输入端和一个输出端;其第一输入端连第一输入信号a;其第二输入端连接第三输入信号d;其第三输入端连接第一输出信号qa,形成反馈;其第四输入端连接第二输出信号qb,形成反馈;其输出端输出控制信号vc连接至所述第一逻辑门模块2;

7.所述第一逻辑门模块2设有两个输入端和一个输出端;其第一输入端连接第一输入信号a;其第二输入端连接第一控制模块1输出的控制信号vc;其输出端作为整体电路的第一输出端并输出第一输出信号qa;当控制信号vc为低电平时,第一逻辑门模块2输出的第一输出信号qa为低电平;

8.所述第二控制模块3设有四个输入端和一个输出端;其第一输入端连接第二输入信号b;其第二输入端连接第三输入信号d;其第三输入端连接第一输出信号qa,形成反馈;其第四输入端连接第二输出信号qb,形成反馈;其输出端输出控制信号vd连接至所述第二逻辑门模块4;

9.所述第二逻辑门模块4设有两个输入端和一个输出端;其第一输入端连接电路第二输入信号b;其第二输入端连接第二控制模块3输出的控制信号vd;其输出端作为整体电路的第二输出端并输出第二输出信号qb;当控制信号vd为低电平时,第二逻辑门模块4输出的第二输出信号qb为低电平。

10.上述第一控制模块1或第二控制模块3结构完全相同,以第一控制模块1说明,所述

第一控制模块1包括一个pmos管pm1,四个nmos管nm1、nm2、nm3、nm4,其中:

11.所述第一pmos管pm1源极与vdd相连,其栅极作为第一控制模块1的第一输入端,其漏极作为第一控制模块1的输出端;

12.所述第一nmos管nm1栅极作为第一控制模块1的第二输入端,其漏极与第三nmos管nm3漏极相连接并连接至第一pmos管pm1的漏极,其源极连接所述第二nmos管nm2漏极;

13.所述第二nmos管nm2栅极与第一pmos管pm1栅极相连,其源极连接至gnd;

14.所述第三nmos管nm3源极与所述第四nmos管nm4漏极相连接,其栅极作为第一控制模块1的第三输入端;

15.所述第四nmos管nm4栅极作为第一控制模块1的第四输入端,其源极接地。

16.上述第一逻辑门模块2和所述第二逻辑门模块4结构完全相同,以第一逻辑门模块2进行说明,该第一逻辑门模块2包括三个pmos管pm2、pm3、pm4和三个nmos管nm5、nm6、nm7;

17.所述pmos管pm2、pm3和nmos管nm5、nm6共同构成与非门结构,所述第二pmos管pm2和第三pmos管pm3,其源极均连接至电源电压vdd,其漏极相连并连接至所述第四pmos管pm4和第七nmos管nm7的栅极;所述第二pmos管pm2和所述第六nmos管nm6的栅极相连并作为第一逻辑门模块2第一输入端;所述第三pmos管pm3和所述第五nmos管nm5的栅极相连并作为第一逻辑门模块2第二输入端;所述第五nmos管nm5连接至所述第四pmos管的栅极,其源极连接所述第六nmos管nm6的漏极,该第六nmos管nm6的源极连接gnd;

18.所述第四pmos管pm4和第七nmos管nm7构成非门,第四pmos管pm4的源极连接电源电压vdd,漏极与第七nmos管nm7漏极相连并作为第一逻辑门模块(2)的输出端;该第七nmos管nm7的源极连接gnd。

19.本发明与现有技术相比,具有如下优点:

20.1.与传统鉴频鉴相器电路相比,减少了使用晶体管数目,从而减小了芯片占用面积,降低了功耗。

21.2.巧妙地搭建控制电路模块和逻辑门模块,缩短了关键路径的延迟时间,提高了鉴频鉴相器精度。

附图说明

22.图1是传统鉴频鉴相器电路图。

23.图2是本发明的结构框图。

24.图3是本发明具体实施例的电路图。

25.图4是本发明具体实施例的工作时序图。

具体实施方式

26.以下参照说明书附图对本发明的实施方式作进一步的说明。

27.参照图2,本发明包括:第一控制模块1、第一逻辑门模块2、第二控制模块3和第二逻辑门模块4四个模块。

28.所述第一控制模块1包括四个输入端和一个输出端;其第一输入端连接第一输入信号a;其第二输入端连接第三输入信号d;其第三输入端连接电路最终第一输出信号qa,形成反馈;其第四输入端连接电路最终第二输出信号qb,形成反馈;其输出端输出控制信号vc

连接所述第一逻辑门模块2的第二输入端。

29.所述第一逻辑门模块2包括两个输入端和一个输出端;其第一输入端连接第一输入信号a;其第二输入端连接第一控制模块1输出的控制信号vc;其输出端作为整体电路的第一输出端输出第一输出信号qa。

30.所述第二控制模块3包括四个输入端和一个输出端;其第一输入端连接第二输入信号b;其第二输入端连接第三输入信号d;其第三输入端连接电路最终第一输出信号qa,形成反馈;其第四输入端连接电路最终第二输出信号qb,形成反馈;其输出端输出控制信号vd连接所述第二逻辑门模块4的第二输入端。

31.所述第二逻辑门模块4包括两个输入端和一个输出端;其第一输入端连接电路总输入端输入信号b;其第二输入端连接第二控制模块3输出控制信号vd;其输出端作为整体电路的第二输出端输出信号qb。

32.参照图3,第一控制模块1包括一个pmos管pm1,四个nmos管nm1、nm2、nm3、nm4,,其中:所述第一pmos管pm1源极与vdd相连,栅极连接第一输入信号a,漏极与第一nmos管nm1漏极、第三nmos管nm3连接;所述第一nmos管nm1与所述第二nmos管nm2串联,nm1源极连接nm2漏极;所述第一nmos管nm1漏极与第一pmos管pm1漏极连接,其栅极连接第三输入信号d;所述第二nmos管nm2源极接地,其栅极连接第一输入信号a;所述第三nmos管nm3与所述第四nmos管nm4串联,nm3源极连接nm4漏极;所述第三nmos管nm3漏极与第一pmos管pm1漏极连接,其栅极连接最终第一输出信号qa,形成反馈;所述第四nmos管nm4源极接地,其栅极连接最终第二输出信号qb,形成反馈。第一控制模块1输出控制信号vc控制第一逻辑门模块2,当控制信号vc为低电平时,第一逻辑门模块2输出第一输出信号qa为低电平。

33.所述第一控制模块3和第二控制模块1结构完全相同,包括一个pmos管pm5,四个nmos管nm8、nm9、nm10、nm11,,其中:所述第一pmos管pm5源极与vdd相连,栅极连接第二输入信号b,漏极与第一nmos管nm8漏极、第三nmos管nm10连接;所述第一nmos管nm8与所述第二nmos管nm9串联,nm8源极连接nm9漏极;所述第一nmos管nm8漏极与第一pmos管pm5漏极连接,其栅极连接第三输入信号d;所述第二nmos管nm9源极接地,其栅极连接第二输入信号b;所述第三nmos管nm10与所述第四nmos管nm11串联,nm10源极连接nm11漏极;所述第三nmos管nm10漏极与第一pmos管pm5漏极连接,其栅极连接最终第一输出信号qa,形成反馈;所述第四nmos管nm11源极接地,其栅极连接最终第二输出信号qb,形成反馈。所述第二控制模块3输出控制信号vd控制第二逻辑门模块4,当控制vd为低电平时,第二逻辑门模块4输出第二输出信号qb为低电平。

34.第一逻辑门模块2包括三个pmos管pm2、pm3、pm4和三个nmos管nm5、nm6、nm7;所述pmos管pm2、pm3和nmos管nm5、nm6共同构成与非门结构,所述第二pmos管pm2和第三pmos管pm3,其源极均连接至电源电压vdd,其漏极相连并连接至所述第四pmos管pm4和第七nmos管nm7的栅极;所述第二pmos管pm2和所述第六nmos管nm6的栅极相连并作为第一逻辑门模块2第一输入端连接第一输入信号a;所述第三pmos管pm3和所述第五nmos管nm5的栅极相连并作为第一逻辑门模块2第二输入端连接控制信号vc;所述第五nmos管nm5连接至所述第四pmos管的栅极,其源极连接所述第六nmos管nm6的漏极,该第六nmos管nm6的源极连接gnd;所述第四pmos管pm4和第七nmos管nm7构成非门,第四pmos管pm4的源极连接电源电压vdd,漏极与第七nmos管nm7漏极相连并作为第一逻辑门模块2的输出端输出第一输出信号qa;该

第七nmos管nm7的源极连接gnd。

35.第二逻辑门模块4包括三个pmos管pm6、pm7、pm8和三个nmos管nm12、nm13、nm14;所述pmos管pm13、pm7和nmos管nm12、nm13共同构成与非门结构,所述第二pmos管pm6和第三pmos管pm7,其源极均连接至电源电压vdd,其漏极相连并连接至所述第四pmos管pm8和第七nmos管nm14的栅极;所述第二pmos管pm6和所述第六nmos管nm13的栅极相连并作为第一逻辑门模块2第一输入端连接第二输入信号b;所述第三pmos管pm7和所述第五nmos管nm12的栅极相连并作为第一逻辑门模块2第二输入端连接控制信号vd;所述第五nmos管nm12连接至所述第四pmos管的栅极,其源极连接所述第六nmos管nm13的漏极,该第六nmos管nm13的源极连接gnd;所述第四pmos管pm8和第七nmos管nm14构成非门,第四pmos管pm8的源极连接电源电压vdd,漏极与第七nmos管nm14漏极相连并作为第一逻辑门模块2的输出端输出第二输出信号qb;该第七nmos管nm14的源极连接gnd。

36.参照图4,本发明的工作原理为:设第三输入信号d连接低电平,第一输入信号a和第二输入信号b连接频率相等的信号,且第二输入信号b相位滞后与第一输入信号a。初始上电时,第一输出信号qa、第二输出信号qb均输出低电平。当第一输入信号a的上升沿到来时,第一逻辑门模块2的第一输入端为高电平,第一逻辑门模块2的第二输入端为高电平,则第一输出信号qa开始输出高电平。同理,当第二输入信号b的上升沿到来时,第二输出信号qb开始输出高电平。此时第一输出信号qa、第二输出信号qb均输出高电平控制nmos管nm3、nm4、nm10、nm11导通,使得第一逻辑门模块2的第二输入端和第二逻辑门模块4的第二输入端为低电平,则第一输出信号qa、第二输出信号qb恢复低电平。整个过程中,qb只存在短暂的高电平时间,所以可以用输出信号qa的脉冲宽度表示输入信号两个上升沿之间的时间间隔。本发明只需要22个晶体管。相比于传统结构,本发明大大减少了鉴频鉴相器的晶体管使用数目,减小了芯片占用面积,降低了功耗。且本发明中输出信号qb的脉冲宽度约为2级门延迟。减小了关键路径延迟时间,提高了鉴频鉴相精度。

37.以上实施例仅表达了本发明的一种具体实施方式,其描述较为具体和详细,但并不能因此而理解为对本发明专利的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1