存储阵列及存储阵列的制备方法与流程

本技术涉及半导体器件领域,尤其涉及存储阵列及存储阵列的制备方法。

背景技术:

1、随着大数据时代的到来,信息量呈现爆炸式增长,人们对于信息处理、传输速度以及存储容量的需求日益严苛。动态随机存储器(dynamic random-access memory,dram)是半导体产业中最为重要的组成部分。

2、dram包括多个存储单元。每个存储单元可以采用1晶体管和1电容(1transistorand1capacitor,1t1c)结构。但采用1t1c结构的dram数据读取的读取窗口较小。

3、为了增大读取窗口,dram中的存储单元可以采用增益结构(gain cell)。增益结构dram中的存储单元可以包括预充晶体管和感知晶体管。在数据写入时导通,使得信号线中的数据写入另一个感知晶体管的栅极。在数据读出时导通,根据感知晶体管的源极和漏极之间的电阻,或流经感知晶体管的源极和漏极的电流,可以读出存储在感知晶体管的栅极的数据。

4、可以在衬底的不同区域形成预充晶体管和感知晶体管,以实现动态随机存储器中的存储单元的功能。但是,在衬底的不同区域形成两个晶体管,需要占用较大的面积,存储密度较低。

技术实现思路

1、本技术提供一种存储阵列及存储阵列的制备方法,能够提高存储密度。

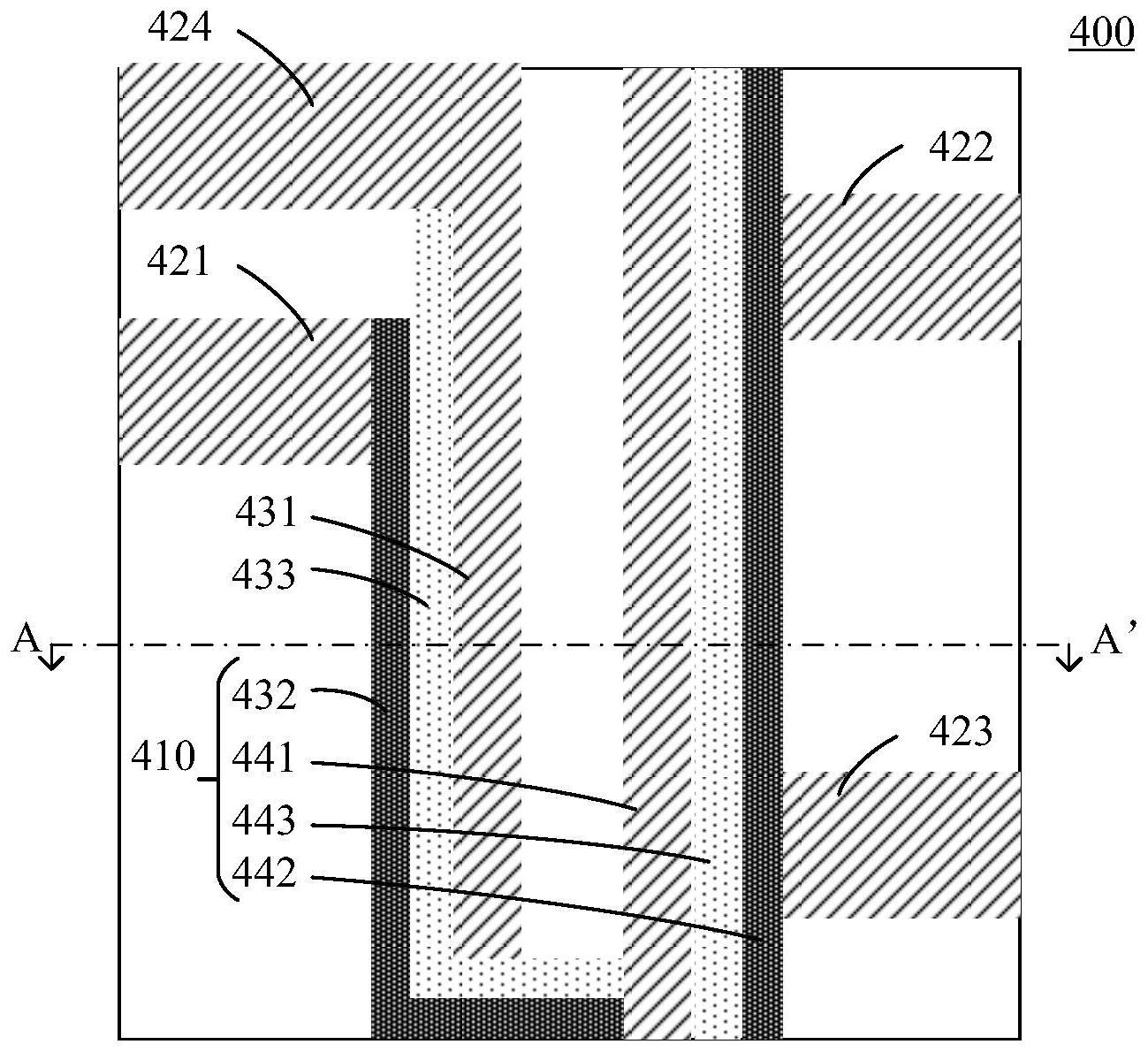

2、第一方面,提供了一种存储阵列,包括多个存储单元,每个所述存储单元包括:通孔结构、第一导电结构、第一电介质层、第一导体层、相互绝缘的第二导体层和第三导体层,所述通孔结构贯穿所述第二导体层、所述第三导体层中的至少一层;所述通孔结构包括第二导电结构、第一半导体层、第二半导体层、第二电介质层,所述第一半导体层、所述第二半导体层、所述第二导电结构沿所述通孔结构的侧壁方向设置,所述第二电介质层位于所述第二半导体层和所述第二导电结构之间;所述第一导电结构用于控制所述第一导体层与所述第二导电结构之间的电连接状态,所述第一导电结构位于所述通孔结构的内侧或外侧,所述第一电介质层位于所述第一导电结构和所述第一半导体层之间;所述第二导电结构用于控制所述第二导体层与所述第三导体层之间的电连接状态。

3、在晶体管中,栅极可以用于控制半导体层,以切换源极与漏极之间的电连接状态。源极与漏极的电连接状态可以是导通状态,也可以是断开状态。在导通状态下,源极与漏极电连接。在断开状态下,源极与漏极之间不存在电连接。

4、第一导电结构可以作为一个晶体管的栅极,第一导体层、第二导电结构可以分别作为该一个晶体管的源极和漏极。第二导电结构可以作为另一个晶体管的栅极,第二导体层、第三导体层可以分别作为该另一个晶体管的源极和漏极。

5、通孔结构贯穿第二导体层、第三导体层中的至少一层,第一半导体层、第二半导体层、第二导电结构沿通孔结构的侧壁方向设置,第一导电结构位于通孔结构的内侧或外侧,从而,利用通孔结构形成两个晶体管,使得两个晶体管位于衬底表面同一个区域内,降低了对面积的占用,提高存储密度。

6、结合第一方面,在一些可能的实现方式中,所述第一导电结构位于所述通孔结构的外侧,且位于所述第二导体层远离所述第三导体层的一侧,所述第一半导体层、所述第二半导体层为相同的半导体层,所述第二电介质层还位于所述第二半导体层与第二导电结构之间。

7、通过将第一导电结构设置在通孔结构的外侧,且位于所述第二导体层远离所述第三导体层的一侧,使得两个晶体管沿通孔侧壁的方向设置,能够进一步降低各个存储单元占用的面积,提高存储密度。

8、结合第一方面,所述第一导体层与所述第二导体层为相同的导体层。利用同一个导体层实现第一导体层与第二导体层的功能,实现金属层的复用,可以降低存储阵列制备的工艺复杂度。

9、结合第一方面,在一些可能的实现方式中,所述存储单元还包括第三导电结构和电容;所述第一导体层、所述第三导体层、所述第一导电结构沿远离衬底的方向依次设置,所述第三导电结构设置在所述第二导电结构远离所述衬底的一侧且与所述第二导电结构接触,所述第三导电结构与所述第一半导体层接触,所述第三导电结构与所述电容电连接。

10、在第二导电结构需要与电容电连接的情况下,通过将第三导电结构设置在第二导电结构远离所述衬底的一侧,即设置在通孔结构顶部,使得第三导电结构能够使得第一半导体层和第二导电结构电连接,并且使得第二导电结构与电容电连接,使得存储单元的结构更为简单,降低存储阵列制备的工艺复杂度。

11、结合第一方面,在一些可能的实现方式中,所述第一半导体层、所述第二半导体层分别位于所述通孔结构方向相对的侧壁;所述第一导电结构位于所述通孔结构的内侧,并且沿所述通孔结构的侧壁方向设置。

12、第一半导体层、所述第二半导体层可以分别位于所述通孔结构方向相对的侧壁,从而,可以将第一导电结构设置在通孔结构的内侧。从而使得位于通孔结构内部且沿通孔结构侧壁方向设置的第一导电结构、第二导电结构分别用于对第一半导体层、所述第二半导体层是否导电进行控制。

13、在通孔结构不同方向的侧壁分别形成两个晶体管,从而降低对面积的占用,提高存储密度。

14、结合第一方面,在一些可能的实现方式中,在所述通孔结构位于所述第二导体层与所述第三导体层之间的部分,沿从所述通孔结构的侧壁指向所述通孔结构的中心的方向,依次设置有所述第二半导体层、所述第二电介质层、所述第二导电结构;在所述通孔结构位于所述第二导电结构与所述第一导体层之间的部分,沿从所述通孔结构的侧壁指向所述通孔结构的中心的方向,依次设置有所述第一半导体层、所述第一电介质层、所述第一导电结构,所述第二导电结构与所述第一半导体层接触。

15、在通孔结构中与不同高度的部分,分别形成两个晶体管,从而降低对面积的占用,提高存储密度。

16、结合第一方面,在一些可能的实现方式中,所述多个存储单元堆叠设置。

17、通过将存储单元堆叠设置,可以提高存储密度。

18、第二方面,提供一种存储器,包括存储控制器和第一方面所述的存储阵列,所述控制器和所述存储阵列电连接。

19、存储控制器可以用于生成控制信息,所述控制信号传输至第一导电结构,以使得所述第一导电结构控制所述第一半导体层。

20、在控制信号使得第一导体层与第二导电结构之间的电连接状态为导通状态时,可以实现数据写入。

21、存储控制器还可以用于获取所述第二半导体层与第三半导体层之间的电学参数。从而,可以实现数据读出。

22、第三方面,提供一种电子设备,包括电路板和第二方面所述的存储器,所述存储器设置于所述电路板上且与所述电路板电连接。

23、第四方面,提供一种存储阵列的制备方法,包括:形成第一导体层,以及相互绝缘的第二导体层和第三导体层;形成通孔结构,所述通孔结构贯穿所述第二导体层、所述第三导体层中的至少一层,所述通孔结构包括第二导电结构、第一半导体层、第二半导体层、第二电介质层,所述第一半导体层、所述第二半导体层、所述第二导电结构沿所述通孔结构的侧壁方向设置,所述第二电介质层位于所述第二半导体层和所述第二导电结构之间;形成第一导电结构和第一电介质层,所述第一导电结构位于所述通孔结构的内侧或外侧,所述第一导电结构用于控制所述第一导体层与所述第二导电结构之间的电连接状态,所述第二导电结构用于控制所述第二导体层与所述第三导体层之间的电连接状态。

24、结合第四方面,在一些可能的实现方式中,所述第一半导体层、所述第二半导体层为相同的半导体层,所述第二电介质层还位于所述第二半导体层与第二导电结构之间。

25、结合第四方面,在一些可能的实现方式中,所述第二导体层与所述第三导体层为相同的导体层。

26、结合第四方面,在一些可能的实现方式中,所述第一导体层、所述第三导体层、所述第一导电结构沿远离衬底的方向依次设置,所述方法还包括:形成第三导电结构,所述第三导电结构设置在所述第二导电结构远离所述衬底的一侧且与所述第二导电结构接触,所述第三导电结构与所述第一半导体层接触;设置电容,所述电容与所述第三导电结构电连接。

27、结合第四方面,在一些可能的实现方式中,所述形成通孔结构,包括:刻蚀通孔,所述通孔贯穿所述第二导体层、所述第三导体层中的至少一层;在所述通孔方向相对的侧壁分别形成所述第一半导体层和所述第二半导体层。所述形成第一导电结构和第一电介质层,包括:在所述通孔结构内侧形成所述第一导电结构和所述第一电介质层,所述第一导电结构沿所述通孔结构的侧壁方向设置。

28、结合第四方面,在一些可能的实现方式中,所述形成通孔结构,包括:在所述通孔结构位于所述第二导体层与所述第三导体层之间的部分,沿从所述通孔结构的侧壁指向所述通孔结构的中心的方向,依次设置所述第二半导体层、所述第二电介质层、所述第二导电结构;在所述通孔结构位于所述第二导电结构与所述第一导体层之间的部分,沿从所述通孔结构的侧壁指向所述通孔结构的中心的方向,依次设置所述第一半导体层;所述形成第一导电结构和第一电介质层,包括:沿从所述通孔结构的侧壁指向所述通孔结构的中心的方向,在所述第一半导体层内侧依次设置所述第一电介质层、所述第一导电结构,所述第二导电结构与所述第一半导体层接触。

29、上述第二方面至第四方面中任一方面中的任一可能实现方式可以达到的技术效果,可以相应参照上述第一方面中任一方面中的任一可能实现方式可以达到的技术效果描述,重复之处不予论述。

- 还没有人留言评论。精彩留言会获得点赞!