半导体结构及其制造方法与流程

本公开实施例涉及半导体领域,特别涉及一种半导体结构及其制造方法。

背景技术:

1、随着动态存储器的集成密度朝着更高的方向发展,在对动态存储器阵列结构中晶体管的排布方式以及如何缩小动态存储器阵列结构中单个功能器件的尺寸进行研究的同时,也需要考虑小尺寸的功能器件对半导体结构整体电学性能的影响。

2、利用垂直的全环绕栅极(gaa,gate-all-around)晶体管结构作为动态存储器选择晶体管(access transistor)时,其占据的面积可以达到4f2(f:在给定工艺条件下可获得的最小图案尺寸),原则上可以实现更高的密度效率,但是对小尺寸的功能器件之间的电连接精度以及导电性能提出了更高的要求,对半导体结构整体的电学性能也提出了更高的要求。

技术实现思路

1、本公开实施例提供一种半导体结构及其制造方法,至少有利于提高半导体结构的电学性能。

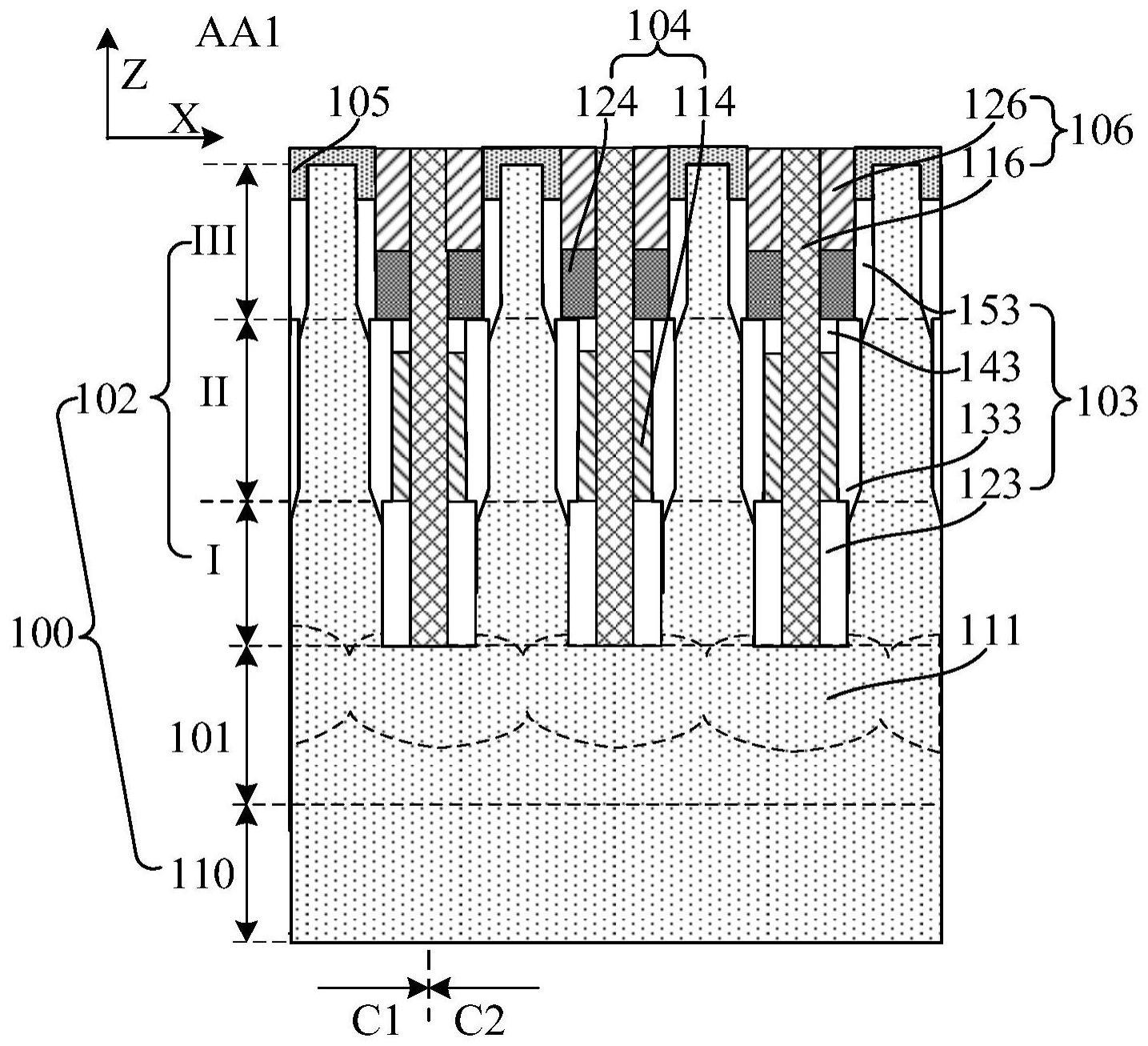

2、根据本公开一些实施例,本公开实施例一方面提供一种半导体结构,包括:基底,所述基底包括间隔排布的位线和半导体通道,所述位线沿第一方向延伸,所述半导体通道位于所述位线的部分顶面,且沿所述位线指向所述半导体通道的方向上,所述半导体通道包括依次排列的第一区、第二区以及第三区;介质层,位于相邻所述位线之间且位于所述半导体通道侧壁;栅极结构,至少环绕所述第二区的所述介质层且沿第二方向延伸,所述第一方向与所述第二方向不同;电连接层,覆盖所述第三区顶面且延伸至所述半导体通道的部分侧壁,所述电连接层和所述介质层共同覆盖所述半导体通道表面;绝缘层,位于同一所述位线上的相邻所述半导体通道之间,所述绝缘层隔离位于相邻所述介质层上的所述栅极结构和所述电连接层。

3、在一些实施例中,所述电连接层中包括镧系元素中的至少一者和/或锆元素。

4、在一些实施例中,沿所述位线指向所述半导体通道的方向上,位于所述第三区顶面的所述电连接层的厚度为10nm~50nm。

5、在一些实施例中,沿垂直于所述半导体通道侧壁的方向上,位于所述半导体通道侧壁的所述电连接层的宽度与所述第三区的所述半导体通道的宽度的比值为1/5~3/5。

6、在一些实施例中,沿所述位线指向所述半导体通道的方向上,位于所述半导体通道侧壁的所述电连接层的高度与所述第三区的所述半导体通道的高度的比值为1/5~3/5。

7、在一些实施例中,所述电连接层在所述位线上的正投影与所述栅极结构在所述位线上的正投影不重合或部分重合。

8、在一些实施例中,在垂直于所述半导体通道侧壁的平面中,所述第一区的所述半导体通道的截面面积、所述第二区的所述半导体通道的截面面积以及所述第三区的所述半导体通道的截面面积依次减小。

9、在一些实施例中,所述栅极结构包括:第一栅极层,环绕所述第二区的所述介质层且沿所述第二方向延伸;第二栅极层,环绕所述第三区的所述介质层,在垂直于所述位线顶面的方向上,所述第二栅极层与所述第一栅极层间隔设置。

10、在一些实施例中,沿所述第一方向上,所述第二栅极层远离所述半导体通道侧壁的侧面与所述第一栅极层远离所述半导体通道侧壁的侧面齐平。

11、在一些实施例中,在垂直于所述半导体通道侧壁的方向上,所述第一栅极层的厚度小于所述第二栅极层的厚度。

12、在一些实施例中,沿所述位线指向所述半导体通道的方向上,环绕所述第二区侧壁的所述第一栅极层的高度与所述第二区的所述半导体通道的高度的比值为1/2~9/10。

13、在一些实施例中,沿所述位线指向所述半导体通道的方向上,环绕所述第三区侧壁的所述第二栅极层的高度与所述第三区的所述半导体通道的高度的比值为1/2~9/10。

14、在一些实施例中,所述半导体结构还包括:金属半导体化合物结构,至少位于与所述绝缘层底面正对的所述位线中。

15、在一些实施例中,沿位于所述绝缘层两侧的所述半导体通道指向所述绝缘层的方向上,所述金属半导体化合物结构的深度逐渐增大。

16、根据本公开一些实施例,本公开实施例另一方面还提供一种半导体结构的制造方法,包括:提供基底,所述基底包括间隔排布的位线和半导体通道,所述位线沿第一方向延伸,所述半导体通道位于所述位线的部分顶面,且在垂直于所述位线顶面的方向上,所述半导体通道包括依次排列的第一区、第二区以及第三区;形成介质层,所述介质层位于相邻所述位线之间且位于所述半导体通道侧壁;形成栅极结构,所述栅极结构至少环绕所述第二区的所述介质层且沿第二方向延伸,所述第一方向与所述第二方向不同;形成电连接层,所述电连接层覆盖所述第三区顶面且延伸至所述半导体通道的部分侧壁,所述电连接层和所述介质层共同覆盖所述半导体通道表面;形成绝缘层,所述绝缘层位于同一所述位线上的相邻所述半导体通道之间。

17、在一些实施例中,提供基底的步骤包括:提供初始基底,所述初始基底内具有沿所述第一方向延伸的初始第一介质层;图形化所述初始基底和所述初始第一介质层,以形成间隔排布的所述位线和所述半导体通道,以及位于相邻位线间的所述初始第一介质层,且所述初始第一介质层顶面不低于所述半导体通道顶面,所述半导体通道侧壁、所述初始第一介质层侧壁和所述位线的部分顶面围成沟槽,所述沟槽沿所述第二方向延伸。

18、在一些实施例中,所述栅极结构包括第一栅极层和第二栅极层,形成所述介质层、所述栅极结构以及所述绝缘层的步骤包括:在所述第一区的所述沟槽侧壁形成第二介质层;形成第一绝缘层,所述第一绝缘层位于所述沟槽内且隔离相邻所述第二介质层,所述第一绝缘层顶面不低于所述半导体通道顶面;在所述第二区的所述沟槽侧壁形成第三介质层和所述第一栅极层,所述第三介质层顶面高于所述第一栅极层顶面;形成第四介质层,所述第四介质层位于所述第一绝缘层和所述第三介质层之间;在所述第三区的所述沟槽侧壁形成第五介质层和所述第二栅极层,所述第五介质层顶面高于所述第二栅极层顶面;形成第二绝缘层,所述第二绝缘层位于所述第一绝缘层和所述第五介质层之间,所述绝缘层包括所述第一绝缘层和所述第二绝缘层。

19、在一些实施例中,在形成所述沟槽之后,在形成所述第二介质层之前,对所述沟槽露出的所述位线的部分顶面进行金属硅化处理,以形成金属半导体化合物结构。

20、在一些实施例中,形成所述电连接层的步骤包括:以所述绝缘层为掩膜,刻蚀所述第五介质层至露出所述第三区顶面和部分侧壁,以在所述绝缘层和所述第三区之间形成凹槽;形成填充满所述凹槽的所述电连接层。

21、在一些实施例中,所述制造方法还包括:在所述电连接层中掺入镧系元素中的至少一者和/或锆元素。

22、本公开实施例提供的技术方案至少具有以下优点:

23、在基底中形成垂直的gaa晶体管,且位线埋入基底中并位于半导体通道下方,因而可以构成3d堆叠的半导体结构,晶体管达到4f2的排列方式,以提高半导体结构的集成密度。而且,电连接层和介质层共同覆盖半导体通道表面,其中,电连接层不仅覆盖半导体通道的第三区顶面而且延伸至半导体通道的部分侧壁,如此有利于增大电连接层与半导体通道之间的接触面积,以减小电连接层与半导体通道的第三区之间的接触电阻,有利于提高电信号在电连接层与半导体通道的第三区之间的传输性能,以改善半导体结构的电学性能;而且,后续在电连接层上做其他功能器件的导电结构时,有利于改善电信号在其他导电结构与半导体通道的第三区之间的传输性能。因此,本公开实施例有利于提高通过电连接层传递给半导体通道的电信号对半导体通道的控制能力,从而有利于提高gaa晶体管的导通/关断灵敏度。

- 还没有人留言评论。精彩留言会获得点赞!