存储器及其制备方法、电子设备与流程

本技术涉及半导体,尤其涉及一种存储器及其制备方法、电子设备。

背景技术:

1、在动态随机动态存储器(dynamic random access memory,dram)、铁电随机存储器(ferroelectric random access memory,feram)或其他存储器中,存储单元可以包括晶体管和电容器。其中,晶体管设置于衬底上,电容器位于晶体管远离衬底的一侧,晶体管和电容器之间电连接。

2、随着电子工业的快速发展和用户的要求,电子设备中存储器的尺寸也逐渐减小,存储单元的集成密度越来越高,存储单元的尺寸越来越小。晶体管中与电容器连接的源极或漏极的尺寸也相应减小,源极或漏极与电容器直接连接难度较大。基于此,相关技术中在晶体管与电容器之间构造了接触层,使得电容器可以与接触面积较大的接触层接触,再与源极或漏极电连接。

3、然而,在对接触层进行图案化的过程中,需要使用两次自对准双重成像技术(self-aligned double patterning,sadp),使用两张光罩,工艺过程十分复杂,制备成本也较高。

技术实现思路

1、本技术实施例提供一种存储器及其制备方法、电子设备,用于简化存储器的制备工艺,降低存储器制备成本,提高存储器的良率。

2、为达到上述目的,本技术的实施例采用如下技术方案:

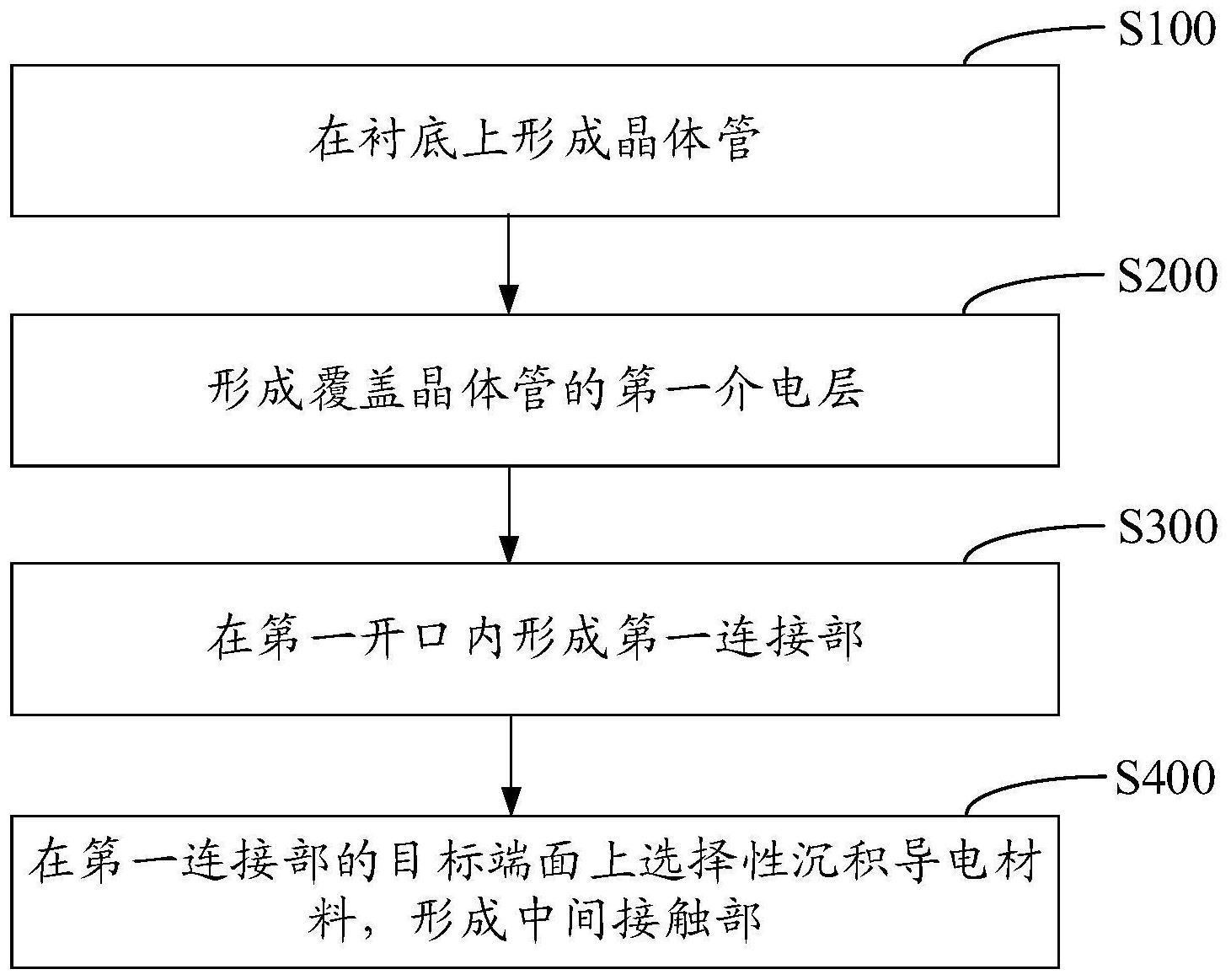

3、第一方面,提供了一种存储器的制备方法,该制备方法包括:在衬底上形成晶体管,所述晶体管包括第一极,所述第一极为源极或漏极。形成覆盖所述晶体管的第一介电层,所述第一介电层包括第一开口,所述第一开口暴露所述晶体管的第一极。在所述第一开口内形成第一连接部。在所述第一连接部的目标端面上选择性沉积导电材料,形成中间接触部;所述目标端面为所述第一连接部的远离所述衬底的端面。

4、本技术上述实施例所提供的存储器的制备方法中,直接在第一连接部的目标端面上选择性沉积导电材料,即可形成中间接触部,无需利用两次自对准双重成像技术,而使得存储器的制备工艺更加简单,存储器的制备成本更低。

5、且由于本技术上述实施例所提供的存储器的制备方法中,无需利用两张光罩形成接触部,因此存储器制备工艺中使用的光罩的总的数目减少。这样,一方面能够进一步降低存储器的制备成本,另一方面还能够省去两次不同角度自对准双重成像技术的两张光罩对位的过程,以及两次不同角度自对准双重成像技术两张光罩与制备位线的光罩对位的过程,进一步简化存储器的制备工艺。同时,存储器制备工艺中使用的光罩的总的数目的减少,还有利于降低因各光罩对位出现偏差,导致存储器中导电膜层之间接触短路,影响存储器的良率的风险。

6、在一些实施例中,所述在所述第一连接部的目标端面上选择性沉积导电材料之前,还包括:对所述目标端面进行表面处理。这样,可以使得目标端面的表面能较大,目标端面的表面能与第一介电层远离衬底的表面的表面能之间相差也较大。由于表面能越大,沉积导电材料时,导电材料的沉积速度越快。因此,对目标端面进行表面处理后,在沉积导电材料时,目标端面上的导电材料的沉积速度较快,第一介电层远离衬底的表面上的导电材料的沉积速度较慢,此时通过控制沉积的时间、速度或其他条件即可选择性的在目标端面上形成中间接触部。

7、在一些实施例中,所述对所述目标端面进行表面处理,包括:将所述目标端面暴露在设定气体环境中;或者,在所述目标端面上涂覆还原性溶液。

8、在一些实施例中,所述在所述第一开口内形成第一连接部,包括:形成覆盖所述第一介电层的导电层,所述导电层包括嵌入所述第一开口的部分;对所述导电层进行平坦化处理至暴露出所述第一介电层,以在所述第一开口内形成所述第一连接部。

9、在一些实施例中,在所述形成覆盖所述第一介电层的导电层之前,还包括:形成中间粘接层,所述中间粘接层覆盖所述第一介电层远离所述衬底的表面,以及所述第一开口的侧壁和底壁;在对所述导电层进行平坦化处理至暴露出第一介电层的过程中,去除所述中间粘接层中位于所述第一介电层远离所述衬底的表面的部分,以在所述第一开口的侧壁和底壁上形成粘接层。

10、在一些实施例中,所述在所述第一开口内形成第一连接部之前,还包括:在所述第一开口内形成第二连接部,所述第二连接部的厚度小于所述第一介电层的厚度。这样,与第一极直接与包括金属材料的第一连接部接触相比,第一极与包括多晶硅材料的第二连接部接触,接触电阻更小,各存储单元的功耗也可以较小。

11、在一些实施例中,所述制备方法还包括:形成覆盖所述中间接触部的第二介电层;去除第一预设厚度的第二介电层,并去除第二预设厚度的中间接触部,剩余的中间接触部形成接触部;所述第一预设厚度小于所述第二介电层的厚度,所述第二预设厚度小于所述中间接触部的厚度。

12、这样,第二介电层陷入相邻两个中间接触部之间,使得相邻两个中间接触部之间相互绝缘,从而有利于改善因相邻两个中间接触部连接,造成相邻两个存储单元之间出现短接的问题,进而有利于提高存储器的良率。本技术实施例去除第二预设厚度的中间接触部,使得接触部远离衬底的表面为平面,接触部与电容器之间的接触面积较大,从而有利于提高接触部与电容器之间的接触稳定性。

13、在一些实施例中,所述制备方法还包括:形成电容器,所述电容器与所述接触部相连。

14、第二方面,提供了一种存储器,该存储器包括衬底、晶体管、第一介电层、第一连接部、接触部、第二介电层。其中,晶体管位于所述衬底上,所述晶体管包括第一极,所述第一极为源极或漏极。第一介电层位于所述晶体管上。第一连接部穿过所述第一介电层与所述第一极电连接。接触部位于所述第一连接部上,且与所述第一连接部电连接。所述接触部远离所述第一连接部的端面为第一端面,所述接触部的与所述第一连接部电连接的端面为第二端面,所述接触部还包括连接第一端面和第二端面的侧面,所述侧面为曲面。所述第二介电层的至少部分位于任意相邻的两个所述接触部之间。

15、在一些实施例中,所述第一端面呈圆形或椭圆形。

16、在一些实施例中,所述第一连接部的与所述接触部电连接的端面为目标端面,所述第一端面的面积大于所述目标端面的面积。

17、在一些实施例中,所述第二端面的面积大于所述目标端面的面积;沿垂直于所述衬底且远离所述衬底的方向,所述接触部的径向尺寸逐渐减小。

18、在一些实施例中,所述第二端面包括第一子端面和第二子端面;所述第一子端面与所述第一连接部接触;所述第二子端面至少部分围绕所述第一子端面,所述第二子端面与所述第一介电层远离所述衬底的表面接触。

19、在一些实施例中,所述第二介电层远离所述衬底的表面与所述接触部远离所述衬底的表面平齐。

20、在一些实施例中,所述存储器还包括粘接层。粘接层位于所述第一连接部与所述第一介电层之间;所述粘接层包括第一子粘接层和第二子粘接层,所述第一子粘接层围绕所述第一连接部的侧面设置,所述第二子粘接层位于所述第一连接部的远离所述接触部的端面。

21、在一些实施例中,所述存储器还包括第二连接部。第二连接部位于所述第一连接部与所述第一极之间,且与所述第一连接部和所述第一极电连接;所述第二连接部的厚度小于所述第一介电层的厚度。

22、在一些实施例中,所述存储器还包括电容器,所述电容器与所述接触部相连。

23、第三方面,提供了一种电子设备,该电子设备包括处理器和存储器,所述处理器与所述存储器耦接;所述存储器为上述任一实施例所述的存储器。

24、其中,第二方面和第三方面中任一种设计方式所带来的技术效果可参见第一方面中不同设计方式所带来的技术效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!