LED驱动集成电路及LED驱动系统的制作方法

led驱动集成电路及led驱动系统

技术领域

1.本公开的实施例涉及电子电路,特别涉及发光二极管(led)驱动电路。

背景技术:

2.为了车辆的审美及功能,当今车辆的后端会使用led依序点亮。在led依序点亮中,大量的led灯串依序地被点亮。由于一个一般的led驱动集成电路可驱动的led灯串数量是有限制的,通常会使用多于一个的led驱动集成电路来驱动所需要的led灯串的数量。因此,需要解决如何同步时间差的问题,此时间差是在其中一个led驱动集成电路驱动而点亮其所驱动的最后一个led灯串和下一个led驱动集成电路驱动而点亮其所驱动的第一个led灯串之间的延时。

技术实现要素:

3.为了实现上述和其他目的,依据本发明的一实施例提供了一种用于驱动多个led灯串的led驱动集成电路,包括使能引脚、多个led使能电路、下游使能电路、控制电路以及下游使能引脚。使能引脚用以提供使能信号。多个led使能电路一对一的对应多个led灯串,其中每一个led使能电路耦接至对应的一个led灯串,并用以在led使能电路被使能时,激发对应的led灯串。下游使能电路用以提供下游使能信号,其中当下游使能电路被使能时,下游使能信号为使能状态。控制电路耦接至使能引脚以接收使能信号,其中控制电路响应于使能信号依序使能多个led使能电路,并在led使能电路均被使能之后使能下游使能电路控制电路。下游使能引脚耦接至下游使能电路,并用以输出下游使能信号。

4.依据本发明的一实施例还提供了一种用于驱动多个led灯串的led驱动集成电路,包括使能引脚、控制电路、多个led使能电路、下游使能开关以及下游使能引脚。使能引脚用以接收使能信号。控制电路耦接至使能引脚以接收使能信号,并用以基于使能信号产生多个led使能控制信号及下游使能控制信号。多个led使能电路一对一的对应多个led灯串及多个led使能控制信号,其中每一个led使能电路耦接至控制电路以接收对应的led使能控制信号,且每一个led使能电路耦接至对应的一个led灯串,并用以响应于对应的led使能控制信号激发或停止激发对应的led灯串。下游使能开关耦接至控制电路以接收下游使能信号,并用以基于下游使能控制信号提供下游使能信号。下游使能引脚耦接至下游使能开关,并用以输出下游使能信号。

5.依据本发明的一实施例还提供了一种led驱动系统,包括第一led驱动集成电路及第二led驱动集成电路,分别用以驱动两组led阵列,每组led阵列包含多个led灯串。第一led驱动集成电路及第二led驱动集成电路各包括使能引脚、多个led使能电路、下游使能电路、控制电路以及下游使能引脚。使能引脚用以接收使能信号。led使能电路一对一的对应led灯串,其中每一个led使能电路耦接至对应的一个led灯串,并用以在led使能电路被使能时,激发对应的led灯串。下游使能电路用以提供下游使能信号,其中当下游使能电路被使能时,下游使能信号为使能状态。控制电路耦接至使能引脚以接收使能信号,其中控制电

路响应于使能信号依序使能多个led使能电路,并在led使能电路被使能之后使能下游使能电路控制电路。下游使能引脚耦接至下游使能电路,并用以输出下游使能信号。其中第二led驱动集成电路的使能引脚耦接至第一led驱动集成电路的下游使能引脚。

附图说明

6.参照下列详细描述和附图以更进一步的理解本发明,其中相似的组件具有相似的附图标记。以下附图仅用于说明,因此可能仅示出装置的一部分,并且不一定按实际比例绘制。

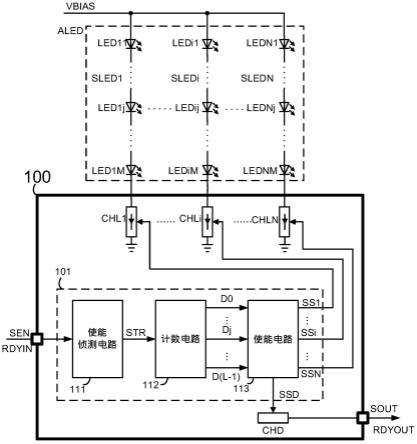

7.图1为依据本发明一实施例的led驱动集成电路100的示意图。

8.图2a为依据本发明一实施例的使能检测电路200的示意图。

9.图2b为依据本发明另一实施例的使能检测电路210的示意图。

10.图3为依据本发明一实施例的示例性使能电路113w的波形示意图。

11.图4为依据本发明一实施例的led驱动集成电路400的示意图。

12.图5为依据本发明一实施例的led驱动集成电路400的波形图。

13.图6为依据本发明一实施例的led驱动系统600的示意图。

14.图7为依据本发明一实施例的另一下游使能电路的示意图。

具体实施方式

15.下面将详细说明本发明的一些实施例。在接下来的描述中,一些具体的细节,例如实施例中和图示中的具体电路结构和这些电路组件的具体参数,都用于对本发明的实施例提供更好的理解,而不必然限制本发明。在阅读本文描述后明显可知本发明可以多种方式修改。除此之外,本发明可以装置、方法、软件等方式实施。据此,本发明可以纯硬件、纯软件或软件结合硬件的方式实施。因此,下列描述不应用于限制本发明。

16.在整个说明书和权利要求书中,复数形式的“多个”或“该些”等术语,除非前后文明确限制为复数,并不排除单数引用。举例来说,“多个led灯串”或“该些led灯串”也可以只包括一个led灯串。再举另一个例子,“多个led”或“该些led”也可以只包括一个led。此外,术语“一”,“一个”和“该”包括复数引用。

17.图1绘示了依据本发明一实施例的led驱动集成电路100的示意图。如图1所示,led驱动集成电路100用以驱动led阵列aled。led阵列aled包括多个led灯串sled1、

……

、sledi、

……

、sledn,其中i表示范围从1到n的整数,且n为大于等于1的整数。led灯串sledi(i=1,2、

……

、n)包含多个led(ledi1、

……

、ledij、

……

、ledim),每一个led都有第一端(如阳极)和第二端(如阴极),其中j表示范围从1到m的整数,且m为大于等于1的整数。多个led(ledi2、

……

、ledim)的第一端如图所示一对一的分别耦接至多个led(ledi1、

……

、ledi(m-1))的第二端,ledi1的第一端用以接收偏置电压vbias作为输入电源供应。

18.如图1所示,led驱动集成电路100用以包括使能引脚rdyin以接收使能信号sen及下游使能引脚rdyout。led驱动集成电路100可进一步地用以包括多个led使能电路chl1、

……

、chli、

……

、chln,该些led使能电路一对一的对应于所述多个led灯串sled1、

……

、sledi、

……

、sledn。更详细地说,led使能电路chli耦接至led灯串sledi,并用以在led使能电路chli被使能时,激发led灯串sledi,或在led使能电路chli被禁能时,停止

激发led灯串sledi。

19.在一实施例中,「激发」led灯串意味着允许足够的电流流经led灯串以点亮led灯串而输出光源,相反地,「停止激发」led灯串意味着抑制足够的电流流经led灯串以使led灯串不被点亮而不输出光源。

20.在一实施例中,当led使能电路chli(i=1、2、

……

、或n)被使能时,建立电流路径以允许足够的电流流经led使能电路chli,且因此流经led灯串sledi。相反地,当led使能电路chli被禁能时,则不建立电流路径而致使没有足够的电流流经led使能电路chli及led灯串sledi。

21.在一实施例中,led使能电路chli(i=1、2、

……

、或n)可以包含如图4所示的led使能开关si。led使能开关si具有第一端、第二端及控制端。led使能开关si的第一端耦接至对应的led灯串sledi的第二端,且led使能开关si的第二端耦接至参考地(例如通过电阻)。led使能开关si用以在其控制端接收led使能控制信号ssi,且响应于led使能控制信号ssi选择性地导通(「使能」)或关断(「禁能」)led使能开关si。更详细地说,当led使能控制信号ssi为激发状态(例如为逻辑“1”)时,导通led使能开关si,而当led使能控制信号ssi为非激发状态(例如为逻辑“0”)时,关断led使能开关si。在一实施例中,led使能开关si可以用金属氧化物半导体场效晶体管(mosfet)来实现。在另一实施例中,mosfet可以是n型的。

22.如图1所示,led驱动集成电路100可进一步地用以包括下游使能电路chd用以提供下游使能信号sout。当下游使能电路chd被使能时,下游使能信号sout为使能状态(例如为逻辑“1”),而当下游使能电路chd被禁能时,下游使能信号sout为禁能状态(例如为逻辑“0”)。下游使能引脚rdyout耦接至下游使能电路chd,且下游使能引脚rdyout用以输出下游使能信号sout。

23.在一实施例中,使能信号sen表示用于依序激发多个led灯串sled1、

……

、sledi、

……

、sledn的操作信息。举例来说,在汽车应用中,使能信号sen可表示依序点亮车尾灯的用户指令。

24.在一实施例中,下游使能电路chd可以包括如图4所示的反相器inv及下游使能开关sd。反相器inv具有输入端及输出端。反相器inv的输入端耦接至使能电路113以接收下游使能控制信号ssd,且反相器inv将下游使能控制信号ssd反相并在反相器inv的输出端输出反相下游使能控制信号ssd1。下游使能开关sd具有第一端、第二端及控制端。下游使能开关sd的第一端耦接至供电电压vcc并用以提供下游使能信号sout。在如图4所示的实施例中,下游使能开关sd的第一端通过电阻rpup耦接至供电电压vcc。下游使能开关sd的第二端耦接至参考地。下游使能开关sd用以在其控制端接收反相下游使能控制信号ssd1,且响应于下游使能控制信号ssd(或反相下游使能控制信号ssd1)选择性地导通(「使能」)或关断(「禁能」)下游使能开关sd。更详细地说,当下游使能控制信号ssd为激发状态(例如为逻辑“1”)而反相下游使能控制信号ssd1为非激发状态(例如为逻辑“0”)时,关断下游使能开关sd。因此,下游使能信号sout为高电压电平,而为使能状态。另一方面,当下游使能控制信号ssd为非激发状态(例如为逻辑“0”)而反相下游使能控制信号ssd1为激发状态(例如为逻辑“1”)时,导通下游使能开关sd。因此,下游使能信号sout为低电压电平,且为禁能状态。在一实施例中,下游使能开关sd为n型的mosfet。

25.在另一实施例中,如图7所示,下游使能电路chd可包括反相器inv、第一下游使能

开关sd1及第二下游使能开关sd2。反相器inv具有输入端及输出端。反相器inv的输入端耦接至使能电路113以接收下游使能控制信号ssd,且反相器inv将下游使能控制信号ssd反相并在反相器inv的输出端输出反相下游使能控制信号ssd1。第一下游使能开关sd1和第二下游使能开关sd2都具有第一端、第二端及控制端。第一下游使能开关sd1的第一端耦接至供电电压vcc,第二下游使能开关sd2的第一端耦接至第一下游使能开关sd1的第一端并用以提供下游使能信号sout,且第二下游使能开关sd2的第二端耦接至参考地。第一下游使能开关sd1的控制端和第二下游使能开关sd2的控制端都用以分别接收反相下游使能控制信号ssd1,并响应于下游使能控制信号ssd(或反相下游使能控制信号ssd1)选择性地导通(「使能」)或关断(「禁能」)第一下游使能开关sd1和第二下游使能开关sd2。更详细地说,当下游使能控制信号ssd为激发状态(例如为逻辑“1”)且反相下游使能控制信号ssd1为非激发状态(例如为逻辑“0”)时,导通第一下游使能开关sd1且关断第二下游使能开关sd2。因此,下游使能信号sout为高电压电平,且为使能状态。另一方面,当下游使能控制信号ssd为非激发状态(例如为逻辑“0”)且反相下游使能控制信号ssd1为激发状态(例如为逻辑“1”)时,关断第一下游使能开关sd1且导通第二下游使能开关sd2。因此,下游使能信号sout为低电压电平,且为禁能状态。在一实施例中,第一下游使能开关sd1为p型的mosfet而第二下游使能开关sd2为n型的mosfet。

26.再参照图1,led驱动集成电路100可进一步地用以包括控制电路101,控制电路101耦接至使能引脚rdyin以接收使能信号sen。控制电路101用以响应于使能信号sen产生多个led使能控制信号ss1、

……

、ssi、

……

、ssn及下游使能控制信号ssd。控制电路101用以使用该多个led使能控制信号ss1、

……

、ssi、

……

、ssn依序使能所述多个led使能电路chl1、

……

、chli、

……

、chln,并使用下游使能控制信号ssd使能下游使能电路chd。在一实施例中,如图3所示,在该多个led使能电路chl1、

……

、chli、

……

、chln均被使能之后使能下游使能电路chd。也就是说,控制电路101依序使能led使能电路chl1、led使能电路chl2、

……

、直到使能led使能电路chln,在此之后,控制电路101才将下游使能电路chd使能。

27.在一实施例中,如图3所示,控制电路101启动依序使能操作,响应于使能信号sen的使能状态使多个led使能电路chl1、

……

、chli、

……

、chln及下游使能电路chd依序使能。在一实施例中,在使能信号sen转换到使能状态之后,控制电路101启动顺序使能操作。在另一实施例中,在使能信号sen转换到使能状态之后,在一个或多个条件满足时,控制电路101启动顺序使能操作。

28.在一实施例中,控制电路101在多个使能时刻t1、

……

、ti、

……

、tn及td使能多个led使能电路chl1、

……

、chli、

……

、chln及下游使能电路chd,其中每两个相继相邻的使能时刻之间具有预设时间间隔td。也就是说,控制电路101分别在每个使能时刻t1、

……

、ti、

……

、tn一对一的对应使能多个led使能电路chl1、

……

、chli、

……

、chln,并且在使能时刻td使能下游使能电路chd。此外,该多个使能时刻t1、

……

、ti、

……

、tn的每两个相继相邻的使能时刻之间具有预设时间间隔td,且在使能led使能电路chln的使能时刻tn和使能下游使能电路chd的使能时刻td之间具有预设时间间隔td。

29.本领域技术人员可理解的是,在上述实施例中,多个使能时刻t1、

……

、ti、

……

、tn的每两个相继相邻的的使能时刻之间的预设时间间隔皆相等,且与在使能时刻tn和使能

时刻td之间的预设时间间隔相等。然而,在另一实施例中,在使能时刻tn和使能时刻td之间的预设时间间隔和多个使能时刻t1、

……

、ti、

……

、tn的每两个相继相邻的的使能时刻之间的预设时间间隔可以不相同。

30.再参照图1,控制电路101用以包括使能检测电路111、计数电路112和使能电路113。使能检测电路111用以接收使能信号sen以产生触发信号str。在一实施例中,使能检测电路111用以接收使能信号sen和使能阈值信号sth1并基于比较使能信号sen和使能阈值信号sth1以产生触发信号str。

31.图2a绘示了依据本发明一实施例的使能检测电路200的示意图。该使能检测电路200可以用作图1中的所述使能检测电路111。使能检测电路200可以包括比较器cmp,比较器具有第一端、第二端及输出端,其中第一端用以接收使能信号sen,第二端用以接收使能阈值信号sth1。在一实施例中,比较器cmp的第一端为非反相输入端且比较器cmp的第二端为反相输入端。比较器cmp比较使能信号sen和使能阈值信号sth1并基于比较结果在输出端产生触发信号str,其中当使能信号sen的电平高于使能阈值信号sth1的电平时,触发信号str为激发状态(例如为逻辑“1”),而当使能信号sen的电平不高于使能阈值信号sth1的电平时,触发信号str为非激发状态(例如为逻辑“0”)。

32.在另一实施例中,如图2b所示,使能检测电路210可以包括比较器cmp,比较器cmp可进一步包括第三输入端,用以接收另一使能阈值信号sth2,在此实施例中,比较器cmp将使能信号sen与使能阈值信号sth1及使能阈值信号sth2进行比较、并基于比较结果在输出端产生触发信号str,其中当使能信号sen的电平高于使能阈值信号sth1的电平时,触发信号str为激发状态(例如为逻辑“1”),而当使能信号sen的电平低于使能阈值信号sth2的电平时,触发信号str为非激发状态(例如为逻辑“0”)。

33.计数电路112用以接收触发信号str并产生具有计数值的计数信号sct,其中计数电路112用以响应于触发信号str的激发状态(例如为逻辑“1”)在每一个预设时间间隔td增加该计数信号sct的该计数值。也就是说,计数电路112用以在触发信号str转换到激发状态之后每经过一个预设时间间隔td即进行一次增加计数信号sct的计数值的操作。

34.在一实施例中,比如可进一步参考图5辅以理解,计数电路112用以接收时钟信号clk,时钟信号clk具有与所述预设时间间隔td相等的时钟周期,且计数电路112响应于时钟信号clk的每一个周期增加所述计数信号sct的计数值。在另一实施例中,时钟信号clk具有多个上升缘,该多个上升缘是在时钟信号clk从非激发状态(例如为逻辑“0”)转换到激发状态(例如为逻辑“1”)时产生,并且每两个相继相邻的上升缘之间具有所述预设时间间隔td。在此实施例中,计数电路112响应于时钟信号clk的每一个上升缘增加所述计数信号sct的计数值。在另一实施例中,计数电路112将所述计数信号sct的计数值从初始计数值l0增加到预设最大计数值lm。

35.表一示出了依据本发明一实施例的示范的计数电路112t的操作。计数电路112t可实现如图1的计数电路112。在一实施例中,如图4所示,计数电路112t用以接收触发信号str及时钟信号clk,且计数电路112t基于触发信号str及时钟信号clk输出计数信号sct,计数信号sct具有计数值,以表1所示的l个连续的数字位元d[l-1]、

……

、d[0]表示,其中l为大于0的整数。更详细地说,当触发信号str为非激发状态(例如为逻辑“0”)时,计数信号sct的计数值为初始值l0,而在触发信号str从非激发状态(例如为逻辑“0”)转换到激发状态(例

如为逻辑“1”)之后,计数电路112t在时钟信号clk的每个上升缘使计数信号sct的计数值增加一,直至使该计数信号sct的计数值从初始计数值l0增加到预设最大计数值lm。以表1所示的l=4为例,计数电路112t有64个状态s1、

……

、s64。假设计数电路112t的初始计数值在触发信号str为非激发状态(例如为逻辑“0”)时为00000,当触发信号str转换为激发状态(例如为逻辑“1”)之后时钟信号clk的第一个上升缘到达时,计数电路112t的计数值从初始计数值00000增加到00001。相似地,当时钟信号clk的下一个上升缘到达时,计数电路112t的计数值接着从00001增加到00010。计数电路112t重复上述操作直到该计数信号sct的计数值达到预设最大计数值lm。在一实施例中,可由led灯串的数量决定预设最大计数值lm。举例来说,当led驱动集成电路100驱动16个led灯串时,预设最大计数值lm可被设为10001。在另一实施例中,数字位元l的数量被设定以使2

l

≥lm。

[0036]

表1

[0037]

状态d[4]d[3]d[2]d[1]d[0]s100000s200001s300010s400011s500100s600101s700110s800111s901000s1001001s1101010s1201011s1301100s1401101s1501110s1601111s1710000s1810001

………………

s6411111

[0038]

使能电路113用以基于计数信号sct产生多个led使能控制信号ss1、

……

、ssi、

……

、ssn及下游使能控制信号sout,其中该多个led使能控制信号ss1、

……

、ssi、

……

、ssn一对一的对应所述多个led使能电路chl1、

……

、chli、

……

、chln,且被分别用以选择性地使能或禁能该多个led使能电路chl1、

……

、chli、

……

、chln,而下游使能电路sout用以选择性地使能或禁能下游使能电路chd。更详细地说,对于每一个i从1到n,当led使能控制信号ssi为激发状态(例如为逻辑“1”)时,使能对应的led使能电路chli,而当led使能控制信号ssi为非激发状态(例如为逻辑“0”)时,禁能对应的led使能电路chli。类

似地,当下游使能控制信号sout为激发状态(例如为逻辑“1”)时,使能下游使能电路chd,而当下游使能控制信号sout为非激发状态(例如为逻辑“0”)时,禁能下游使能电路chd。

[0039]

图3为依据本发明一实施例的示例性使能电路113w的波形示意图。使能电路113w可实现如图1所示的使能电路113。为方便起见,以下描述将在假设led驱动集成电路100用来驱动16个led使能电路的情况下说明使能电路113的操作。使能电路113w用以将数字形式的计数信号sct转换为模拟形式的多个led使能控制信号ss1、

……

、ssi、

……

、ssn及模拟形式的下游使能控制信号ssd。详细地说,使能电路113w用以接收计数信号sct,且当计数信号sct的计数值从00000转换为00001时,led使能控制信号ss1从非激发状态(例如为逻辑“0”)转换为激发状态(例如为逻辑“1”)以使能led使能电路chl1。相似地,当计数信号sct的计数值从00001转换为00010时,led使能控制信号ss2从非激发状态(例如为逻辑“0”)转换为激发状态(例如为逻辑“1”)以使能led使能电路chl2。使能电路113w重复上述操作直到当计数信号sct的计数值从01111转换为10000时led使能电路chl16被使能。之后,当计数信号sct的计数值从10000转换为10001时,下游使能控制信号ssd从非激发状态(例如为逻辑“0”)转换为激发状态(例如为逻辑“1”)以使能下游使能电路chd。

[0040]

图4为依据本发明一实施例的led驱动集成电路400的示意图。在led驱动集成电路400中,使能检测电路可由图2a中的比较器cmp实施,在另一实施例中,可由图2b的比较器cmp实施。计数电路可由上述的计数电路112t实施,使能电路可由使能电路113w实施,led使能电路chli(i=1、2、

……

、或n)可由led使能开关si实施,且下游使能电路chd可由反相器inv及下游使能开关sd实施。

[0041]

图5为led驱动集成电路400的波形图。接下来,参照图5说明led驱动集成电路400的操作。为方便起见,以下描述将在假设led驱动集成电路100用来驱动16个led使能电路的情况下说明使能电路113的操作。当使能信号sen的电平高于使能阈值信号sth1的电平(例如2v)时,在时间点t0,比较器cmp输出的触发信号str转换为激发状态(例如为逻辑“1”),使得计数电路112将计数信号sct的计数值从初始值(如图5所示的00000)开始增加计数。如图5所示,当触发信号str转换为激发状态之后时钟信号clk的第一个上升缘到达时,在时间点t1,计数信号sct从00000增加到00001,使得使能电路113输出的led使能控制信号ss1为激发状态(例如为逻辑“1”)。因此,激发状态的led使能控制信号ss1导通led使能开关s1,而随之激发对应的led灯串sled1。接着,在经过预设时间间隔td之后,在时间点t2,时钟信号clk的第二上升缘到达,使得计数信号sct从00001增加到00010,因此使使能电路113输出的led使能控制信号ss2为激发状态(例如为逻辑“1”)。该激发状态的led使能控制信号ss2导通led使能开关s2,而因此激发对应的led灯串sled2。重复地执行上述操作直到计数信号sct从01111增加到10000,最后一个led灯串sled16在时间点t16被激发,且led使能控制信号ss16因此转换为激发状态(例如为逻辑“1”)。

[0042]

接下来,在时间点t17,时钟信号clk的下一个上升缘到达时,计数信号sct从10000增加到10001,使得使能电路113输出的下游使能控制信号ssd为激发状态(例如为逻辑“1”),且由反相器inv输出的反相下游使能控制信号ssd1为非激发状态(例如为逻辑“0”)。因此,非激发状态的反相下游使能控制信号ssd1关断下游使能开关sd,使得下游使能信号sout为高电压电平且为使能状态(例如为逻辑“1”)。

[0043]

图6为依据本发明一实施例的led驱动系统600的示意图。led驱动系统600用以包

括第一led驱动集成电路ic1及第二led驱动集成电路ic2。第一led驱动集成电路ic1用以驱动led阵列aled1,led阵列aled1具有如图1所示的led阵列aled设置。第二led驱动集成电路ic2用以驱动led阵列aled2,led阵列aled2具有如图1所示的led阵列aled设置。第一led驱动集成电路ic1及第二led驱动集成电路ic2可以是上述实施例描述的led驱动集成电路。在一实施例中,第一led驱动集成电路ic1及第二led驱动集成电路ic2可以是如图1所示的驱动集成电路100。在另一实施例中,第一led驱动集成电路ic1及第二led驱动集成电路ic2可以是如图4所示的led驱动集成电路400。第二led驱动集成电路ic2的使能引脚rdyin耦接至第一led驱动集成电路ic1的下游使能引脚以从第一led驱动集成电路ic1接收下游使能信号sout以作为第二led驱动集成电路ic2的使能信号sen。

[0044]

接下来说明具有led驱动系统600的操作。当从第一led驱动集成电路ic1接收的使能信号sen的电平高于使能阈值信号sth1的电平(例如2v)时,在时间点t0,比较器cmp输出的触发信号str转换为激发状态(例如为逻辑“1”),使得计数电路112将计数信号sct的计数值从初始值(如图5所示的00000)开始增加计数。如图5所示,当触发信号str转换为激发状态之后时钟信号clk的第一个上升缘到达时,在时间点t1,计数信号sct的计数值从00000增加到00001,使得使能电路113输出的led使能控制信号ss1为激发状态(例如为逻辑“1”)。因此,激发状态的led使能控制信号ss1导通led使能开关s1,而随之激发对应的led灯串sled1。接着,在预设时间间隔td之后,在时间点t2,时钟信号clk的第二上升缘到达,使得计数信号sct的计数值从00001增加到00010,因此使使能电路113输出的led使能控制信号ss2为激发状态(例如为逻辑“1”)。该激发状态的led使能控制信号ss2导通led使能开关s2,而因此激发对应的led灯串sled2。重复地执行上述操作直到计数信号sct的计数值从01111增加到10000,最后一个led灯串sled16在时间点t16被激发,且led使能控制信号ss16因此转换为激发状态(例如为逻辑“1”)。

[0045]

接下来,在时间点t17,时钟信号clk的下一个上升缘到达时,计数信号sct的计数值从10000增加到10001,使得使能电路113输出的下游使能控制信号ssd为激发状态(例如为逻辑“1”),且由反相器inv输出的反相下游使能控制信号ssd1为非激发状态(例如为逻辑“0”)。因此,非激发状态的反相下游使能控制信号ssd1关断下游使能开关sd,使得下游使能信号sout为高电压电平且为使能状态(例如为逻辑“1”)。由于第二led驱动集成电路ic2从第一驱动集成电路ic1接收下游使能信号sout作为第二led驱动集成电路ic2的使能信号sen,第一驱动集成电路ic输出的激发状态的下游使能信号sout的电平会高于第二led驱动集成电路ic2的使能阈值信号sth1的电平(例如2v),因此第二led驱动集成电路ic2会重复地执行上述第一驱动集成电路ic的操作以激发第二led驱动集成电路ic2驱动的多个led灯串sled1、sledi、

……

、sled16。

[0046]

由上面描述的led驱动系统600的操作可知,第一驱动集成电路ic1可从下游使能引脚rdyout输出下游使能信号sout到第二led驱动集成电路ic2以在第一驱动集成电路ic1激发其所驱动的led阵列aled1中的最后一个led灯串sled 16的时间到第二led驱动集成电路ic2激发其所驱动的led阵列aled2中的第一个led灯串sled 1的时间的这段期间支持延迟信息的通信。这大幅度地简化了同步两个邻近的led驱动集成电路点亮led灯串的时间的架构。特别是,与传统的所有集成电路从微控制器单元接收使能信号的差分接口解决方案相比,本发明的led驱动集成电路会从微控制器单元释放出资源。

[0047]

本领域技术人员可知,本发明不限于上述的特定内容与细节。相对地,本发明的保护范围由权利要求所定义,包含前述多种不同特征的组合及部分组合,还包含在这些组合或部分组合的基础上,本领域技术人员在阅读上述描述后可以了解且不属于现有技术的变型及修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1