1.本技术实施例涉及电路板技术领域,尤其涉及一种多层印制电路板。

背景技术:2.印制电路板(printed circuit board,简称为pcb)是电子工业的重要部件之一。几乎每种电子设备,小到电子手表、计算器,大到计算机、通信电子设备、军用武器系统,只要有集成电路等电子元件,为了使各个元件之间的电气互连,都要使用印制电路板。

3.印制电路板包括单面印制电路板、双面印制电路板以及多层印制电路板。在相关技术中,具有单端走线的多层印制电路板包括多层单端走线层以及多层参考层,每个单端走线层均对应一个参考层,相对应的单端走线层与参考层相邻,且相对应的单端走线层与参考层之间设置有绝缘介质层。具有单端走线的多层印制电路板在设计时,为了使单端走线的特性阻抗与目标阻抗(与单端走线连接的芯片的协议阻抗)匹配,部分单端走线的线宽较小,但是单端走线的线宽较小时,其载流能力较差,影响单端走线信号传输的质量。

技术实现要素:4.本技术实施例提供一种多层印制电路板,用以解决部分单端走线由于线宽较小,影响单端走线信号传输的质量的技术问题。

5.本技术实施例为解决上述技术问题提供如下技术方案:

6.本技术实施例提供了一种多层印制电路板,包括沿第一方向依次层叠设置的第一单端走线层和n层参考层,n为大于1的正整数,所述参考层为实铜层;

7.所述第一单端走线层包括多条单端走线,在多条所述单端走线中,至少一条所述单端走线为加宽走线;

8.靠近所述第一单端走线层的前m层参考层上设置有至少一个通孔组,所述通孔组包括多个通孔,各所述通孔贯穿靠近所述第一单端走线层的前m层参考层,m为小于n的正整数;

9.所述通孔组与所述加宽走线一一对应,所述通孔组用于使对应所述通孔组的所述加宽走线透过该通孔组参考第m+1层参考层,以升高所述加宽走线的特性阻抗。

10.本技术实施例的有益效果:本技术实施例提供的多层印制电路板对单端走线层中至少部分宽度较小的单端走线进行加宽处理,即对本技术实施例的第一单端走线层的至少一条单端走线进行加宽处理以形成加宽走线,在参考层不变的情况下,加宽走线加宽处理后,其特性阻抗减小,为了使加宽走线加宽后,其特性阻抗与目标阻抗匹配,本技术实施例在靠近第一单端走线层的前m层参考层上设置与加宽走线对应的通孔组,以使加宽走线透过通孔组参考第m+1层参考层,从而使得加宽走线与参考层之间的电容减小,加宽走线与参考层之间的电容减小使得加宽走线的特性阻抗升高,为了使加宽走线的特性阻抗与目标阻抗匹配,需要增加加宽走线的宽度以降低加宽走线的特性阻抗,从而实现了在保证单端走线的特性阻抗与目标阻抗相匹配的情况下,对宽度较小的单端走线进行加宽处理,以增加

单端走线信号传输的质量的目的。

11.在一种可能的实施方式中,在相对应的所述通孔组与所述加宽走线中,所述通孔组的多个所述通孔呈两排分布,所述加宽走线在第一平面上的正投影位于两排所述通孔在第一平面上的正投影之间,所述第一平面与所述第一方向垂直。

12.在一种可能的实施方式中,在相对应的所述通孔组与所述加宽走线中,所述通孔组的多个所述通孔沿所述加宽走线的长度方向呈一排分布,所述加宽走线在第一平面上的正投影与呈一排分布的多个所述通孔在第一平面上的正投影平行,所述第一平面与所述第一方向垂直。

13.在一种可能的实施方式中,在相对应的所述通孔组与所述加宽走线正投影于所述第一平面上时,所述通孔组的各所述通孔靠近所述加宽走线的一侧与所述加宽走线之间的垂直距离不小于5mil。

14.在一种可能的实施方式中,所述通孔为梯形孔,且所述梯形孔的下底边与所述加宽走线平行,且所述梯形孔的下底边位于靠近所述加宽走线的一侧。

15.在一种可能的实施方式中,所述梯形孔的下底边的长度等于所述加宽走线的宽度。

16.在一种可能的实施方式中,在同一排所述通孔中,相邻两个所述梯形孔的下底边之间的间距不大于所述梯形孔的下底边的长度。

17.在一种可能的实施方式中,在正投影于所述第一平面上的所述通孔组的两排通孔中,其中一排所述通孔在第一直线上的正投影形成多个间隔分布的第一线段,另一排所述通孔在所述第一直线上的正投影形成多个间隔分布的第二线段,所述第一直线位于所述第一平面内,且所述第一直线与各排通孔延伸的方向平行;

18.多条所述第一线段与多条所述第二线段在所述第一直线上交替排布,且任意相邻的所述第一线段与所述第二线段至少部分重合。

19.在一种可能的实施方式中,所述参考层为接地层。

20.在一种可能的实施方式中,所述加宽走线的线宽大于3mil。

附图说明

21.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。

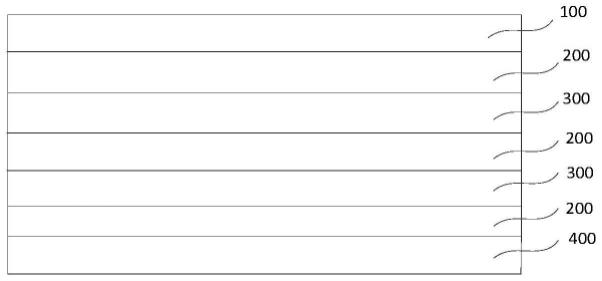

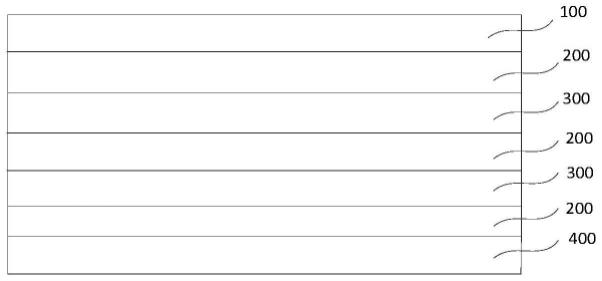

22.图1为本技术实施例多层印制电路板的一种结构示意图;

23.图2为本技术实施例通孔组在第一平面上的正投影;

24.图3为本技术实施例加宽走线与对应的两排通孔在第一平面上的正投影;

25.图4为本技术实施例加宽走线与对应的一排通孔在第一平面上的正投影;

26.图5为本技术实施例的多层印制电路板与相关技术的多层印制电路板的hfss仿真结果对比图。

27.附图标记说明:

28.100、单端走线层;

29.110、加宽走线;

30.200、绝缘介质层;

31.300、参考层;

32.310、通孔;

33.400、第二走线层;

34.500、第一平面。

35.通过上述附图,已示出本技术明确的实施例,后文中将有更详细的描述。这些附图和文字描述并不是为了通过任何方式限制本技术构思的范围,而是通过参考特定实施例为本领域技术人员说明本技术的概念。

具体实施方式

36.在相关技术中,具有单端走线的多层印制电路板包括多层单端走线层以及多层参考层,每个单端走线层均对应一个参考层,相对应的单端走线层与参考层相邻,且相对应的单端走线层与参考层之间设置有绝缘介质层。为了保证信号传输的质量,避免反射,单端走线的特性阻抗要与目标阻抗(与单端走线连接的芯片的协议阻抗)匹配,但是由于位于单端走线层与参考层之间的绝缘介质层的厚度通常较薄,使得相邻的单端走线层与参考层之间的距离过近,从而使得单端走线在设计时,部分单端走线的线宽较小,而线宽较小的单端走线的载流能力较差,影响单端走线信号传输的质量。另一方面,当单端走线的线宽小于3mil时,单端走线的加工较为困难,由此使得在单端走线的实际加工过程中,线宽小于3mil的单端走线加工误差较大,使得单端走线的特性阻抗与目标阻抗不匹配,进而影响信号传输的质量。

37.有鉴于此,本技术实施例通过在靠近单端走线的前m层参考层上设置通孔组,以使单端走线透过通孔组参考第m+1层参考层,从而使得单端走线与参考层之间的电容减小,加宽走线与参考层之间的电容减小使得单端走线的特性阻抗升高,为了使加宽走线的特性阻抗与目标阻抗匹配,需要增加单端走线的宽度以降低加宽走线的特性阻抗,从而实现了在保证单端走线的特性阻抗与目标阻抗相匹配的情况下,对宽度较小的单端走线进行加宽处理,以增加单端走线信号传输的质量的目的。

38.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术的一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

39.图1为本技术实施例多层电路板的一种结构示意图;图2为本技术实施例通孔组在第一平面上的正投影;图3为本技术实施例加宽走线与对应的两排通孔在第一平面上的正投影;图4为本技术实施例加宽走线与对应的一排通孔在第一平面上的正投影;图5为本技术实施例的多层印制电路板与相关技术的多层印制电路板的hfss仿真结果对比图。

40.本技术实施例提供的多层印制电路板可以为四层结构、六层结构、八层结构或者更多层结构。示例性的,当多层印制电路板为六层结构时,六层印制电路板包括沿第一方向依次层叠设置的第一单端走线层和三层参考层,其中,靠近第一单端走线层的参考层为第一参考层,位于中间的参考层为第二参考层,远离第一单端走线层的参考层为第三参考层,六层印制电路板还包括与第二参考层对应的第二走线层以及与第三参考层对应的第三走线层,也就是说,六层印制电路板包括沿第一方向依次层叠设置的第一单端走线层、第一参

考层、第二走线层、第二参考层、第三参考层、第三走线层,且相邻两层之间设置有绝缘介质层。再例如,如图1所示,当多层印制电路板为四层结构时,四层印制电路板包括沿第一方向依次层叠设置的第一单端走线层100和两层参考层300,四层印制电路板还包括与远离第一单端走线层100的参考层300对应的第二走线层400,也就是说,四层印制电路板包括沿第一方向依次层叠设置的第一单端走线层100、参考层300、参考层300、第二走线层400,且相邻两层之间设置有绝缘介质层200,即四层印制电路板包括沿第一方向依次层叠设置的第一单端走线层100、绝缘介质层200、参考层300、绝缘介质层200、参考层300、绝缘介质层200、第二单端走线层100。也就是说,本技术实施例提供的多层印制电路板包括沿第一方向依次层叠设置的第一单端走线层100和n层参考层300,n为大于1的正整数,参考层300为实铜层。

41.可以理解的是,上述第一方向为多层印制电路板的厚度方向。

42.在本技术实施例中,如图2、图3和图4所示,第一单端走线层100包括多条单端走线,在多条单端走线中,至少一条单端走线为加宽走线110。也就是说,在多条单端走线中至少有一条单端走线做加宽处理以形成上述的加宽走线110,对单端走线做加宽处理后,能够提高该单端走线的载流能力,且便于加工。为了使加宽处理后的单端走线的特性阻抗与目标阻抗匹配,本技术实施例在靠近第一单端走线层100的前m层参考层300上设置至少一个通孔组,通孔组与加宽走线110一一对应,也就是说,加宽走线110设置一条,通孔组设置一个;加宽走线110设置两条,通孔组设置两个;加宽走线110设置五条,通孔组设置五个。

43.通孔组包括多个通孔310,各通孔310贯穿靠近第一单端走线层100的前m层参考层300,m为小于n的正整数。通孔组用于使对应通孔组的加宽走线110透过该通孔组参考第m+1层参考层300,加宽走线110透过通孔组参考第m+1层参考层300时,加宽走线110透过通孔组参考第m+1层参考层300的电容减小,即加宽走线110与相关联的参考层300之间的电容减小,加宽走线110与相关联的参考层300之间的电容减小使得加宽走线110的特性阻抗升高,为了使加宽走线110的特性阻抗与目标阻抗匹配,需要增加加宽走线110的宽度以降低加宽走线110的特性阻抗,从而实现了在保证单端走线的特性阻抗与目标阻抗相匹配的情况下,对宽度较小的单端走线进行加宽处理,以增加单端走线信号传输的质量的目的。

44.对于上述分析,示例性说明如下,在靠近第一单端走线层100的前m层参考层300上不设置通孔组时,即参考层300为不开设通孔组的实铜层,此时,第一单端走线层100中具有宽度较小的单端走线,例如其中一条宽度较小的单端走线为第一单端走线,第一单端走线在设计时,其宽度为2.5mil,特性阻抗(等于目标阻抗)为50ohm,第一单端走线的宽度较小,使得加工难度较大且载流能力较差,可以通过加宽处理以提高其载流能力以及便于加工,加宽处理的方式为,在靠近第一单端走线层100的前m层参考层300上设置一个与第一单端走线对应的通孔组,此时,第一单端走线透过通孔组参考第m+1层参考层300,以使得第一单端走线的特性阻抗升高,例如第一单端走线的特性阻抗升高至80ohm(示例性说明),而与第一单端走线对应的目标阻抗为50ohm,此时需要降低第一单端走线的特性阻抗,降低第一单端走线的特性阻抗的方式可以为增加第一单端走线的宽度,即将第一单端走线的宽度调增为4mil以使得第一单端走线的特性阻抗降至50ohm,因此,本技术实施例通过在单端走线的前m层参考层300上设置通孔组来实现加宽单端走线的目的。可以理解的是,上述的第一单端走线即为第一单端走线层100的加宽走线110。

45.值得说明的是,m可以为1,2或3等,m的取值根据单端走线的加宽需求设计,例如,

在靠近第一单端走线层100的一层参考层300上开设通孔组,以使加宽走线110参考第二层参考层300时既能够满足加宽走线110加宽的需求,那么,该多层印制电路板既可以只在靠近第一单端走线层100的一层参考层300上开设通孔组。如果只在靠近第一单端走线层100的一层参考层300上开设通孔组不能够满足需求,加宽走线110在加宽后依旧较窄,那么可以在靠近第一单端走线层100的两层参考层300上开设通孔组,以使加宽走线110参考第三层参考层300,以进一步减小加宽走线110与相关联的参考层300之间的电容,从而进一步增加加宽走线110的宽度。

46.此外,值得说明的是,在加宽走线110参考第三层参考层300或更下一层参考层300时,位于靠近加宽走线110的一层参考层300与加宽走线110透过通孔组参考的参考层300之间的走线层的各走线均避让开通孔组的各通孔310。

47.在靠近第一单端走线层100的前m层参考层300上设置与加宽走线110对应的通孔组能够增加加宽走线110的宽度的原理如下:

[0048][0049][0050]

i=kt

0.44a0.75

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(3)

[0051]

公式(1)中,c为电容,ε是介电常数,每一种材料都有自己的介电常数,是不变值,s是电容器两极板的正对面积,kd是电容器两极板之间的距离。

[0052]

公式(2)中,c是电容,z0是走线特性阻抗,l是单位长度传输线的固有电感。

[0053]

公式(3)中,k为修正系数,一般覆铜线在内层时取0.024,在外层时取0.048,t为最大温升,单位为摄氏度(铜的熔点是1060℃),a为覆铜截面积,单位为平方mil,i为容许的最大电流,单位为安培(amp)。

[0054]

以上述的第一单端走线为例进行说明,第一单端走线的目标阻抗为50ohm,由于第一单端走线与临近第一单端走线的参考层300之间的距离较小,使得第一单端走线在设计时,其线宽较窄,为2.5mil,为增加第一单端走线的线宽,在临近第一单端走线的参考层300上开设通孔组,临近第一单端走线的参考层300为第一参考层300,从公式中分析其实现原因:在第一参考层300上开设通孔组时,返回电流流经第一参考层300的通孔组时,电流会参考到下一层参考层300(第二参考层300),也就是公式(1)中的kd增大,则会引起电容c减小,将电容c带入公式(2)中,电容c减小引起第一单端走线的特性阻抗增高,此时为维持第一单端走线的特性阻抗保持50ohm,需要将第一单端走线加宽(第一单端走线变宽,则特性阻抗降低),因此满足了设计线宽高于3mil的要求。

[0055]

此外,从公式3可以看出,覆铜截面积a越小,走线载流能力i越差,从而避免在开关电源时产生的大电流对第一单端走线造成的损害。其中,覆铜截面积a为覆铜的厚度乘以覆铜线径的宽度。

[0056]

在本技术的一些实施例中,如图4所示,在相对应的通孔组与加宽走线110中,对于宽度较小的单端走线(加宽处理后即为加宽走线110)首先预设一个线宽,计算预设线宽的单端走线的特性阻抗,当预设线宽的单端走线的特性阻抗与目标阻抗的差值小于10ohm时,通孔组的多个通孔310沿加宽走线110的长度方向呈一排分布,加宽走线110在第一平面500

上的正投影与呈一排分布的多个通孔310在第一平面500上的正投影平行,第一平面500与第一方向垂直,也就是说,多个通孔310呈一排设置,且该排通孔310位于加宽走线110的一侧。由于预设线宽的单端走线的特性阻抗与目标阻抗的差值小于10ohm,即预设线宽的单端走线需要加宽的量较小时,只需在与该单端走线对应的参考层300上开设一排通孔310即可,此时,由于通孔310设置的数量较少,通孔310不易分为两排,因为两排通孔310会较为分散使得该单端走线的特性阻抗分布不均匀,进而影响信号的传输。

[0057]

在本技术的另一些实施例中,如图2和图3所示,在相对应的通孔组与加宽走线110中,当参考层300未对应加宽走线110设置通孔组时,对于宽度较小的单端走线(加宽处理后即为加宽走线110)首先预设一个线宽,计算预设线宽的单端走线的特性阻抗,当加宽走线110的特性阻抗与目标阻抗的差值大于10ohm时,通孔组的多个通孔310呈两排分布,加宽走线110在第一平面500上的正投影位于两排通孔310在第一平面500上的正投影之间,第一平面500与第一方向垂直。也就是说,多个通孔310分为两排,每排通孔310均在加宽走线110的长度方向上延伸,且两排通孔310位于加宽走线110的两侧,由于预设线宽的单端走线的特性阻抗与目标阻抗的差值大于10ohm,即预设线宽的单端走线需要加宽的量较大时,此时,通孔310设置的数量较多,通孔310分为两排,便于通孔310的设置,并且能够增加通孔310的数量,且两排通孔310位于加宽走线110的两侧,对返回电流的影响较小。当然,当在靠近加宽走线110的参考层300开设两排通孔310不能满足需求时,可以同时在第二层参考层300开设通孔组,或者在第二层参考层300和第三层参考层300开设通孔310。

[0058]

在单排通孔310的设置以及两排通孔310的设置中,在相对应的通孔组与加宽走线110正投影于第一平面500上时,通孔组的各通孔310靠近加宽走线110的一侧与加宽走线110之间的垂直距离不小于5mil。此设置能够避免参考层300上开设通孔组对返回电流的影响。

[0059]

在本技术的一些实施例中,通孔310为梯形孔,且梯形孔的下底边与加宽走线110平行,且梯形孔的下底边位于靠近加宽走线110的一侧。此设置使得梯形下部较大面积的区域靠近加宽走线110,此设置能够使得加宽走线110与相关参考层300之间的电容减小的更多,利于加宽走线110的特性阻抗的提高,而梯形上部面积较小的区域远离加宽走线110,此设置能够在保证通孔组对加宽走线110起作用的同时,尽量减小通孔组对其他单端走线的影响。此外,梯形孔相较于三角形孔具有更大的面积,梯形孔相较于三角形孔能够使得加宽走线110与相关参考层300之间的电容减小的更多,利于加宽走线110的特性阻抗的提高,并且,在第一单端走线层100具有多条单端走线的情况下,梯形孔与矩形孔、圆形孔等相比具有可穿插性,能够节省空间。可选的,为了避免通孔组的设置引起的加宽走线110的特性阻抗不连续的情况,梯形孔的下底边的长度等于加宽走线110的宽度。可选的,在同一排通孔310中,相邻两个梯形孔的下底边之间的间距不大于梯形孔的下底边的长度。

[0060]

当通孔组的多个通孔310呈两排设置时,如图2所示,在正投影于第一平面500上的通孔组的两排通孔310中,其中一排通孔310在第一直线上的正投影形成多个间隔分布的第一线段,另一排通孔310在第一直线上的正投影形成多个间隔分布的第二线段,第一直线位于第一平面500内,且第一直线与各排通孔310延伸的方向平行,也就是说,第一直线为平行于加宽走线110的长度方向的直线,其可以为其中一排的各通孔310的中心的连线。多条第一线段与多条第二线段在第一直线上交替排布,且任意相邻的第一线段与第二线段至少部

分重合。也就是说,任意相邻的第一线段与第二线段可以是端点重合,也可以是部分线段重合,此设置能够使得加宽走线110的特性阻抗的连续性较好,避免加宽走线110的特性阻抗分布不均匀,影响信号的传输。

[0061]

在本技术实施例中,各参考层300为接地层(ground,简写为gnd),且加宽走线110的线宽大于3mil,也就是说,加宽走线110经过加宽处理后,其宽度大于3mil,此设置便于加宽走线110的加工。

[0062]

本技术实施例提供的多层印制电路板与相关技术的多层印制电路板的hfss(high frequency simulator structure,简写为hfss,hfss为一种3d建模工具)仿真结果对比图如图5所示,在本技术实施例提供的多层印制电路板与相关技术的多层印制电路板的仿真过程中,除了本技术实施例在对应宽度较小的单端走线的参考层上设置通孔组,其他参数均不变,图中1为相关技术中多层印制电路板的宽度较小的单端走线的阻抗曲线,2为本技术实施例提供的多层印制电路板中相应的单端走线的阻抗曲线,对比两条曲线可知,在对应宽度较小的单端走线的参考层上设置通孔组可以显著提高单端走线的特性阻抗,为了使得单端走线的特性阻抗与目标阻抗一致,需要将单端走线加宽,因此能够满足单端走线加宽的需求,并且单端走线加宽后对信号噪声、畸变等具有良好的抑制作用。

[0063]

本技术旨在涵盖本技术的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本技术的一般性原理并包括本技术未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本技术的真正范围和精神由下面的权利要求书指出。

[0064]

应当理解的是,本技术并不局限于上面已经描述并在附图中示出的精确结构,并且可以在不脱离其范围进行各种修改和改变。本技术的范围仅由所附的权利要求书来限制。