基于IGBT驱动的电平识别方法与流程

基于igbt驱动的电平识别方法

技术领域

1.本发明涉及igbt驱动领域,具体涉及一种基于igbt驱动的电平识别方法。

背景技术:

2.目前变频控制普遍使用ipm(intelligent power module)或多个igbt(insulated gate bipolar transistor)与驱动芯片作为驱动电路,ipm输入信号和驱动芯片的输入信号的逻辑电平既存在高电平有效(即输入端输入高电平时,输出有效信号驱动igbt导通,低电平则igbt截止)也存在低电平有效(即输入端输入低电平时,输出有效信号驱动igbt导通,高电平则igbt截止),在变频控制过程中,必须严格按照ipm或驱动芯片的要求进行逻辑驱动,否则会引起驱动混乱或烧毁器件的后果。

3.虽然,针对既定的ipm或驱动芯片的有效逻辑电平是不变的,但在控制端(如mcu)通过相应的软硬件设置实现有效逻辑电平的切换时,均涉及到软件硬件的不统一,不清楚驱动芯片是高电平有效还是低电平有效,导致在生产管控、物资齐套等方面存在许多问题。

技术实现要素:

4.本发明的目的是提供一种基于igbt驱动的电平识别方法,实现了驱动芯片有效逻辑电平的准确识别,可有效提高物料通用化程度,降低由于物料不匹配带来的器件损坏不能工作的风险。

5.本发明采取如下技术方案实现上述目的,基于igbt驱动的电平识别方法,用于对驱动电路中驱动芯片的有效电平进行识别,所述驱动电路包括控制模块,控制模块的输出端与驱动芯片的输入端连接,驱动芯片的输出端与igbt的栅极连接,igbt的发射极通过电阻接地,集电极与外部第一电源连接,所述电平识别方法包括:

6.控制模块输出pwm控制信号至驱动芯片,驱动芯片对控制信号进行处理后输出至igbt栅极,并在pwm控制信号为高电平或低电平时,分别对电阻上的信号进行采样,得到第一信号值以及第二信号值,并进行判断,若第一信号值>第二信号值,则判断驱动芯片高电平有效;若第二信号值>第一信号值,则判断驱动芯片低电平有效。

7.进一步的是,所述igbt的数量为多个,至少一个igbt作为上桥臂,至少一个igbt作为下桥臂,上桥臂以及下桥臂的igbt的栅极分别与驱动芯片的输出引脚连接,上桥臂igbt的发射极分别与下桥臂igbt的集电极以及外部第二电源连接,上桥臂igbt的集电极与外部第一电源连接,下桥臂igbt的发射极通过电阻接地;所述电平识别方法包括:

8.驱动电路上电后,设置控制模块的io引脚处于高阻态,然后控制模块输出pwm控制信号至驱动芯片对应引脚,驱动芯片对控制信号进行处理后输出至对应下桥臂igbt的栅极,并在pwm控制信号为高电平或低电平时,分别对电阻进行信号采样,得到第一信号值以及第二信号值,并进行判断,若第一信号值>第二信号值,则驱动芯片高电平有效;若第二信号值>第一信号值,则驱动芯片低电平有效。这样对较为复杂的igbt驱动电路,也能实现驱动芯片的电平识别,提高了适应性。

9.进一步的是,所述第一信号值与第二信号值为电流值或电压值。

10.所述电平识别方法还包括:

11.若第一电流值>第二电流值,且第一电流值大于设定电流阈值,则驱动芯片高电平有效;若第二电流值>第一电流值,且第二电流值大于设定电流阈值,则驱动芯片低电平有效。将第一电流值与设定的电流阈值进行比较,能够再次提高有效电平识别的准确性。

12.进一步的是,所述电平识别方法还包括:

13.若第一电压值>第二电压值,且第一电压值大于设定电压阈值,则驱动芯片高电平有效;若第二电压值>第一电压值,且第二电压值大于设定电压阈值,则驱动芯片低电平有效。将第一电压值与设定的电压阈值进行比较,能够再次提高有效电平识别的准确性。

14.进一步的是,所述电平识别方法还包括:

15.在输出pwm控制信号为高电平或低电平时,按照设定的采样间隔时间分别对电阻进行电流或电压采样,得到第一波形以及第二波形,计算第一波形与第二波形的平均值、有效值或最大值,计算结果为i1与i2,并对i1与i2的大小进行判断,若i1>i2+

△

i1,则判断驱动芯片为高电平有效;若i2>i1+

△

i2,则判断驱动芯片为低电平有效;

△

i1、

△

i2分别为第一波形以及第二波形对应的补偿值。通过波形图的平均值、有效值或最大值的比较实现有效电平的识别,能够增加识别方法的多样性,并且包含了补偿值的计算,能够提高识别的准确性。

16.本发明通过控制模块输出pwm控制信号至驱动芯片,驱动芯片对控制信号进行处理后输出至igbt栅极,并在pwm控制信号为高电平或低电平时,分别对电阻上的信号进行,得到第一信号值以及第二信号值,若第一信号值>第二信号值,表示pwm控制信号为高电平时igbt导通,进一步表示驱动芯片高电平有效;若第二信号值>第一信号值,表示pwm控制信号为低电平时igbt导通,进一步表示驱动芯片低电平有效。实现了驱动芯片有效逻辑电平的准确识别,可有效提高物料通用化程度,降低由于物料不匹配带来的器件损坏不能工作的风险。

附图说明

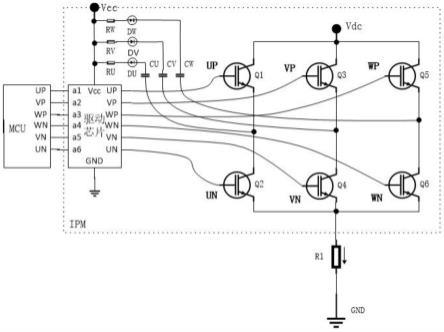

17.图1是本发明实施例提供的基于多个igbt的驱动电路图。

18.附图中,r1为电阻,rw为第一电阻,rv为第二电阻,ru为第三电阻,dw、dv、du为二极管,cu、cv、cw为电容,q1、q2、q3、q4、q5、q6为igbt,up、vp、wp、un、vn、wn为mcu芯片、以及驱动芯片对应的输出引脚,vdc为第一电源,vcc为第二电源。

具体实施方式

19.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

20.下面结合附图对本发明的具体实施方式进行详细说明。

21.通常用于变频驱动的方式有两种:1、使用集成的ipm模块进行驱动;2、使用驱动电路/芯片对6个igbt进行驱动,而ipm模块其内部亦可看作将驱动电路/芯片和6个igbt封装

到一个器件中,本发明所指的驱动芯片既包括ipm模块内部的驱动电路/芯片,也包括单独的驱动电路/芯片。所指的igbt既包括ipm内部集成的igbt,也包括外部独立的igbt。

22.本发明基于igbt驱动的电平识别方法,用于对驱动电路中驱动芯片的有效电平进行识别,所述驱动电路包括控制模块,控制模块的输出端与驱动芯片的输入端连接,驱动芯片的输出端与igbt的栅极连接,igbt的发射极通过电阻接地,集电极与外部第一电源连接,所述电平识别方法包括:

23.控制模块输出pwm(pulse width modulation)控制信号至驱动芯片,驱动芯片对控制信号进行处理后输出至igbt栅极,并在pwm控制信号为高电平或低电平时,分别对电阻上的信号进行采样,得到第一信号值以及第二信号值,并进行判断,若第一信号值>第二信号值,则判断驱动芯片高电平有效;若第二信号值>第一信号值,则判断驱动芯片低电平有效。

24.在本发明的一种实施例中,igbt的数量可以为多个,至少一个igbt作为上桥臂,至少一个igbt作为下桥臂,上桥臂以及下桥臂的igbt的栅极分别与驱动芯片的输出引脚连接,上桥臂igbt的发射极分别与下桥臂igbt的集电极以及外部第二电源连接,上桥臂igbt的集电极与外部第一电源连接,下桥臂igbt的发射极通过电阻接地;所述电平识别方法包括:

25.驱动电路上电后,设置控制模块的io引脚处于高阻态,然后控制模块输出pwm控制信号至驱动芯片对应引脚,驱动芯片对控制信号进行处理后输出至对应下桥臂igbt的栅极,并在pwm控制信号为高电平或低电平时,分别对电阻进行信号采样,得到第一信号值以及第二信号值,并进行判断,若第一信号值>第二信号值,则驱动芯片高电平有效;若第二信号值>第一信号值,则驱动芯片低电平有效。这样对较为复杂的igbt驱动电路,也能实现驱动芯片的电平识别,提高了适应性。

26.其中第一信号值与第二信号值可以为电流值或电压值。

27.上述电平识别方法还包括:

28.若第一电流值>第二电流值,且第一电流值大于设定电流阈值,则驱动芯片高电平有效;若第二电流值>第一电流值,且第二电流值大于设定电流阈值,则驱动芯片低电平有效。将第一电流值与设定的电流阈值进行比较,能够再次提高有效电平识别的准确性。

29.上述电平识别方法还包括:

30.若第一电压值>第二电压值,且第一电压值大于设定电压阈值,则驱动芯片高电平有效;若第二电压值>第一电压值,且第二电压值大于设定电压阈值,则驱动芯片低电平有效。将第一电压值与设定的电压阈值进行比较,能够再次提高有效电平识别的准确性。

31.上述电平识别方法还包括:

32.在输出pwm控制信号为高电平或低电平时,按照设定的采样间隔时间分别对电阻进行电流或电压采样,得到第一波形以及第二波形,计算第一波形与第二波形的平均值、有效值或最大值,计算结果为i1与i2,并对i1与i2的大小进行判断,若i1>i2+

△

i1,则判断驱动芯片为高电平有效;若i2>i1+

△

i2,则判断驱动芯片为低电平有效;

△

i1、

△

i2分别为第一波形以及第二波形对应的补偿值。通过波形图的平均值、有效值或最大值的比较实现有效电平的识别,能够增加识别方法的多样性,并且包含了补偿值的计算,能够提高识别的准确性。

33.实施例

34.本发明实施例对应的驱动电路图如图1所示,三个igbt,q1、q3、q5作为上桥臂,三个igbt,q2、q4、q6作为下桥臂,q1、q3、q5以及q2、q4、q6的栅极分别与驱动芯片的引脚up、引脚vp、引脚wp、引脚un、引脚vn、引脚wn连接,上桥臂的igbt的集电极与第一电源vdc连接,q1的发射极与q2的集电极连接,并通过电容cu、二极管du、第三电阻ru与第二电源vcc连接;q3的发射极与q4的集电极连接,并通过电容cv、二极管dv、第二电阻rv与第二电源vcc连接;q5的发射极与q6的集电极连接,并通过电容cw、二极管dw、第一电阻rw与第二电源vcc连接;下桥臂igbt的发射极通过电阻r1接地;mcu(microcontroller unit,微控制单元)的输出控制引脚up、vp、wp、wn、vn、un分别与控制芯片的引脚a1、a2、a3、a4、a5、a6连接。

35.在一种实施方式中,针对上述驱动电路的驱动芯片电平识别方法具体包括:

36.s100.在上电完成后,mcu的up、vp、wp、un、vn、wn引脚设置为输入状态或高阻态,此时驱动芯片由于内部上拉/下拉电阻使驱动芯片对应的输出端up、vp、wp、un、vn、wn全部为低电平,6个igbt全部关断,此时流过r1的相电流为0。

37.s101.mcu检查内部flash中是否存有驱动芯片有效逻辑电平信息,若没有,则执行步骤s102,否则执行s103。

38.s102.mcu通过引脚un输出至少一个周期的pwm控制信号至控制芯片的a6引脚,控制信号经过驱动芯片处理后,通过对应un引脚输出至q2,并在pwm控制信号为高电平或低电平时分别检测电阻r1上的电流或电压,若pwm控制信号为高电平时检测到的电流或电压远远大于pwm控制信号为低电平时的电流或电压,表示驱动芯片为高电平有效,反之则为低电平有效。

39.s103.进行正常驱动控制。

40.在本实施方式中,mcu可以通过引脚un、vn输出至少一个周期的pwm控制信号,最终控制q2与q4;或者mcu可以通过引脚un、vn、wn输出至少一个周期的pwm控制信号,最终控制所有下桥臂的igbt。

41.在另一种实施方式中,针对上述驱动电路的电平识别方法具体包括:

42.s100.在上电完成后,mcu的up、vp、wp、un、vn、wn引脚设置为输入状态或高阻态,此时驱动芯片由于内部上拉/下拉电阻使驱动芯片对应的输出端up、vp、wp、un、vn、wn全部为低电平,6个igbt全部关断,流过r1的相电流为0。

43.s101.mcu检查内部flash中是否存有驱动芯片有效逻辑电平信息,若没有,则执行步骤s102,否则执行s111。

44.s102.开启mcu对相电流的采样,即通过检测流过r1的电流,具体的,通过测试检测r1两端的电压为vr1,则相电流=vr1/r1。

45.s103.设置mcu的un脚为输出状态,并输出低电平。

46.s104.持续检测相电流,并记录每次检测的相电流值,记为波形1。

47.s105.等待时间ti1后,设定mcu的un脚为高电平。

48.s106.持续检测相电流值,并记录每次检测的相电流值,记为波形2。

49.s107.等待时间ti2后,设定mcu的un脚为输入状态或高阻态。

50.s108.计算波形1和波形2对应的平均值iavg1和iavg2,并进行判断。

51.s109.若iavg1》iavg2+

△

i1,则判断驱动芯片为低电平有效。若iavg1《iavg2

‑△

i2,则判断驱动芯片为高电平有效。否则,无法判定驱动芯片有效电平,并报出故障。

△

i1、

△

i2分别为第一波形以及第二波形对应的补偿值。

52.s110.将检测到的逻辑电平信息保存到flash中。

53.s111.进行正常驱动控制。

54.综上所述,本发明通过上述软件方法能够自动识别ipm或驱动芯片的有效逻辑电平,可有效提高物料通用化程度,降低由于物料不匹配带来的器件损坏不能工作的风险。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1