1.本发明属于电源管理技术领域,具体的说是涉及一种基于锁相环同步外部时钟的时钟产生电路。

背景技术:2.在电源管理技术领域,通常的芯片控制技术需要内部具有一个时钟用于给斜坡产生电路提供时钟参考,或者用于产生开启功率管的逻辑时钟,因此,一颗电源管理芯片至少需要具有一个时钟产生电路用于给芯片提供内部的时钟。此外,随着技术、芯片功率密度等等的发展,多相位交错控制技术越来越多的应用于电源芯片的控制中。对于多相位交错控制电源管理技术,其需要芯片的时钟根据相位的个数具有不同相位差的时钟信号,例如双相控制,两个相位的时钟需要相差180

°

,这样多相位交错控制才能实现输出电压纹波的最小化、无源功率器件的缩小等优点。因此,时钟产生电路除了产生其初始相位的时钟外,还需要能够产生与初始相位具有相位差的其它时钟。多相交错控制技术除了在一颗芯片内实现多个相位控制外,还有多颗芯片并联实现多相位交错控制技术,因此芯片内的时钟需要具有与片外时钟同步的能力,这样才能让并联的时钟初始相位与另一颗芯片具有确定的相位差。

技术实现要素:3.针对上述时钟产生电路在多相交错控制电源管理芯片中的设计需求,本发明提出一种同步片外时钟并具有多种相位时钟输出的锁相环时钟产生电路。在没有芯片外时钟输入时,本发明自身通过一个方波产生电路可以产生固定频率的时钟,在芯片外输入时钟后,本发明通过一个锁相环同步片外时钟。此外,本发明除了产生时钟信号外,还能够产生多种占空比与相位差的其它时钟信号用于多相位交错控制技术的芯片当中。

4.本发明的技术方案为:

5.一种基于锁相环同步外部时钟的时钟产生电路,其特征在于,包括鉴相与电荷泵模块、时钟频率产生模块和分频分相模块;

6.所述鉴相与电荷泵模块包括第一与非门、第二与非门、第三与非门、第一反相器、第二反相器、第三反相器、第一d触发器、第二d触发器、第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第一nmos管、第二nmos管、第三nmos 管、第四nmos管、第五nmos管、第六nmos管、第七nmos管、第八nmos管、第一电流源、第一电阻、第一电容、第二电容;其中,第一与非门的一个输入端接内部初始相位时钟,其另一个输入端接启动信号,输出端接第一反相器的输入端;第二与非门的一个输入端接外部时钟,其另一个输入端接启动信号,输出端接第二反相器的输入端;第一d触发器的时钟信号端接第二反相器的输出端,第一d触发器的r端接第三反相器的输出端;第二 d触发器的时钟信号端接第二反相器的输出端,第二d触发器的r端接第三反相器的输出端;第三反相器的输入端接第三与非门的输出端,第三与非门的一个输入端接第一d触发器的q 输出端,第三与非门的另一个输入

端接第二d触发器的q输出端;第一pmos管的源极接电源,其栅极和漏极互连,其漏极接第二nmos管的漏极;第二nmos管的栅极接第一nmos 管的栅极和漏极、第一电流源的输出端,第二nmos管的源极和第一nmos管的源极接地;第二pmos管的源极接电源,其栅极接第一d触发器的q非输出端;第三pmos管的源极接第二pmos管的漏极,第三pmos管的栅极接第一pmos管的漏极;第八nmos管的漏极接第三pmos管的漏极,第七nmos管的漏极接第八nmos管的源极,第七nmos管的栅极和第八nmos管的栅极接启动信号;第四nmos管的漏极接第七nmos管的源极,第四nmos管的栅极接第一电流源的输出端;第三nmos管的漏极接第四nmos管的漏极,第三nmos管的栅极接第二d触发器的q输出端,第三nmos管的源极接地;第四pmos 管的源极接电源,其栅极接第一pmos管的漏极;第五pmos管的源极接第四pmos管的漏极,第六pmos管的源极接第五pmos管的漏极,第五pmos管的栅极和第六pmos管的栅极接启动信号;第六nmos管的漏极和栅极接第六pmos管的漏极,第五nmos管的漏极和栅极接第六nmos管的源极,第五nmos管的源极接地;第八nomos管源极、第七nmos管漏极、第五pmos管漏极、第六pmos管源极与第一电阻一端和第一电容一端相连作为鉴相与电荷泵模块的输出端,第一电阻另一端通过第二电容后接地,第一电容的另一端接地;

7.所述时钟频率产生模块包括第七pmos管、第八pmos管、第九pmos管、第十pmos 管、第十一pmos管、第十二pmos管、第十三pmos管、第十四pmos管、第十五pmos 管、第十六pmos管、第十七pmos管、第十八pmos管、第十九pmos管、第二十pmos 管、第九nmos管、第十nmos管、第十一nmos管、第十二nmos管、第十三nmos 管、第十四nmos管、第十五nmos管、第十六nmos管、第十七nmos管、第十八nmos 管、第十九nmos管、第二十nmos管、第二十一nmos管、第二十二nmos管、第二十三nmos管、第四反相器、第五反相器、第六反相器、第七反相器、第二电流源、第二电阻、第三电阻、第三电容;其中,第七pmos管的栅极接鉴相与电荷泵模块的输出端,其源极接第十二pmos管的漏极、第八pmos管的源极,第七pmos管的漏极接第十三nmos管的栅极和漏极、第十四nmos管的栅极;第十三nmos管的源极和第十四nmos管的源极接地;第十二pmos管的源极接第十一pmos管的漏极,第十二pmos管的栅极接第十一pmos 管的栅极、第九pmos管的栅极、第十pmos管的栅极和漏极、第十三pmos管的栅极、第十四pmos管的栅极、第十一nmos管的漏极;第九pmos管的源极接电源,其漏极接第十pmos管的源极;第十一nmos管的栅极接第九nmos管的栅极和漏极、电流源的输出端、第十nmos管的栅极、第十二nmos管的栅极;第十nmos管的漏极接第九nmos 管的源极,第十nmos管的源极接地;第十二nmos管的漏极接第十一nmos管的源极,第十二nmos管的源极接地;第八pmos管的栅极接参考电压,其漏极接第十四pmos管的漏极、第十四nmos管的漏极、第十五nmos管的漏极和栅极、第十九nmos管的栅极和第二十nmos管的栅极;第十四nmos管的源极接地;第十四pmos管的源极接第十三 pmos管的漏极;第十六nmos管的漏极接第十五nmos管的源极,第十六nmos管的源极接地;第十五pmos管的源极接电源,其栅极接第十六pmos管的栅极和漏极、第十七 pmos管的栅极、第十八pmos管的栅极、第十七nmos管的漏极,第十五pmos管的漏极接第十六pmos管的源极;第十八nmos管的漏极接第十七nmos管的源极,第十八 nmos管的源极接地;第十八pmos管的源极接第十七pmos管的漏极,第十八pmos管的漏极接第二十四nmos管的漏极、第二十pmos管的源极、第二十三nmos管的源极;第十九pmos管的源极接电源,栅极接第六反相器的输出端,其漏极接第十九nmos管的漏极、第二十一pmos管的源极、第二十一nmos管的源极;第二十nmos管的漏极接第十九nmos管的源极,第二十nmos管的源极接地;第二十

pmos管的栅极接第七反相器的输出端,其漏极接第二十三nmos管的漏极、第四反相器的输入端、第二十二nmos管的漏极、第二十一pmos管的漏极、第二十一nmos管的漏极、第三电容的一端;第二十三 nmos管的栅极接第六反相器的输出端;第二十二nmos管的栅极接启动信号,其源极接地;第二十一pmos管的栅极接第六反相器的输出端,第二十一nmos管的栅极接第七反相器的输出端;第五反相器的输入端接第四反相器的输出端,第五反相器的输出端接第六反相器的输入端、第二电阻的一端,第二电阻的另一端接第三电容的另一端和第三电阻的一端,第三电阻的另一端接地;第六反相器的输出端输出6倍时钟频率信号并接第七反相器的输入端,第七反相器输出控制信号;所述6倍时钟频率信号为外部时钟的6倍时钟频率信号;

8.所述分频分相模块的输入为6倍时钟频率信号,6倍时钟频率信号经过分频分相模块后产生占空比为1/12、1/6、1/3、1/2的时钟输出。

9.本发明增益效果:本发明提出的一种同步片外时钟并具有多种相位时钟输出的锁相环时钟产生电路,通过将锁相环、频率产生电路以及分频电路相结合,实现同步片外时钟功能并能输出多种占空比时钟、多种相位差的时钟信号。

附图说明

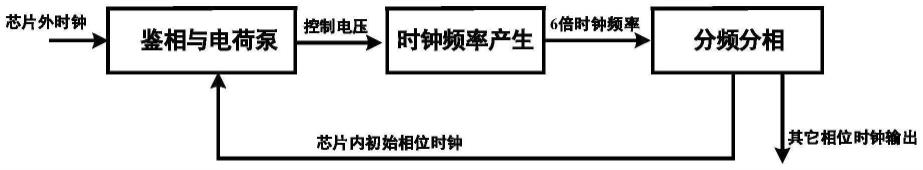

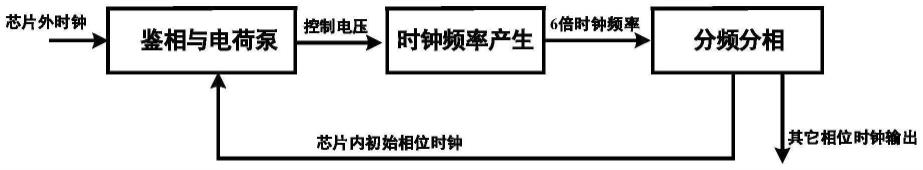

10.图1为本发明的系统框图。

11.图2为鉴相与电荷泵的具体实现电路。

12.图3为时钟频率产生的具体实现电路。

13.图4为分频分相模块的具体实现电路。

14.图5为分频分相电路中状态机状态的具体设置。

15.图6为同步片外650khz时钟信号时的仿真工作波形。

16.图7为图6仿真波形局部图。

17.图8为本发明多种相位与占空比时钟信号输出的仿真波形。

具体实施方式

18.下面结合附图对本发明进行详细描述。

19.图1为本发明的具体设计框图,通过图1可以知道本发明的技术实现过程,首先,通过鉴相与电荷泵模块,将芯片外的时钟与芯片内的初始相位时钟的相位差转换为控制电压,其具体转换过程见图2及其说明,通过控制电压的大小不同,时钟频率产生模块会相应的更改其输出的6倍时钟频率的大小,以实现芯片内初始相位时钟与芯片外时钟的同步,其具体实现电路见图3及其说明,为了实现多种占空比与多种相位的时钟输出,本发明时钟产生模块产生的时钟为芯片外时钟的6倍频率,这样通过分频分相模块首先可以得到除了与片外时钟同频同相的时钟外,还有与片外时钟具有相位差的不同占空比时钟信号,其具体实现电路见图4及其说明。

20.图2为鉴相与电荷泵模块的电路实现,由于本发明适合用于电源管理芯片中,因此可以用到电源管理芯片内部数字电路常用的2.4v电压vcc1作为本发明鉴相与电荷泵模块的电源轨,其具体工作原理为:启动信号通常为整个电源芯片上电过程中的一个逻辑电压信号,电源管理芯片一般都具有这个信号,当电压管理芯片内部电源轨vcc1建立好之后,启

动信号由低电平转变为高电平,图2所示电路开始工作,首先通过逻辑门q1~q6,d1~d2组成的鉴相电路检测芯片外时钟与芯片内时钟的上升沿之差,其中芯片外时钟与芯片内时钟可能为具有不同占空比的电压信号,其上升沿之差会反应到由mos管mn1~mn8、mp1~mp6以及片外补偿rs、cs和cp组成的电荷泵电路中的mos管mp2与mn3的开启与关断上,例如,当启动信号由低电平变为高电平后,mos管mn8与mos管mn7开启,如果芯片外时钟上升沿先于芯片内初始相位时钟,则触发器d1的qn为低,而d2的输出也为低,那么此时 mp2打开,mn3关闭,则会有电流通过镜像mos管mp3给片外补偿元件充电,控制电压上升,本发明的后级电路会利用这个控制电压的上升调整芯片内初始相位时钟的频率大小,直到芯片内初始相位时钟的上升沿不再滞后于芯片外时钟。当芯片外时钟与芯片内初始相位时钟上升沿都已经到来时,触发器d1与d2在q的输出会将d1与d2同时重置,这样可以保证鉴相功能只鉴相相位差而与时钟信号占空比无关。此外,由于片外补偿元件通常为较大的电容和电阻,通过mos管mn4和mn3的微安级电流充放电来让控制电压由0v上升到稳定的电压需要一定的时间,因此本发明具有由mos管mp4~mp6、mn5和mn6组成初始化电路结构,在启动信号为低的时间段,mos管mp5与mp6打开,mp4管流过的电流在mos 管mn6与mn5上产生两倍栅源电压,在bcd工艺中,低压器件阈值电压一般在0.6v~0.75v 之间,因此通过设置mp4管的镜像电流大小以及mos管mn5~mn6的尺寸,可以让控制电压初始值在1.2v~1.5v之间,接近本发明后级产生电路的中心频率所在的控制电压大小1.2v,锁相环通过中心频率向高频与低频调整控制电压相对于从0v电压开始更好。

21.图3为本发明的时钟频率产生模块的具体实现电路,其中mos管mn9~mn29与 mp9~mp18所在的跨导放大器结构用到的电压vcc2为电源管理芯片内常有的5v电压轨,而反相器q5~q8仍然使用vcc1作为电源轨,参考电压的大小通常为1.2v电压,因此图2 中的电路将控制电压初始值设置在1.2v左右及保证初始频率在中心频率,时钟频率产生模块其具体工作过程为,ib为镜像电流其通过镜像管mn9~mn12、mp9~mp14镜像得到ia与is 两股镜像电流,而mos管mp7、mp8、mp11、mp12、mn13、mn14组成的传统差分结构将控制电压的压差转为mp8管漏端的电流流入流出,因此,当控制电压等于参考电压时,电流ig为0,流入镜像管mn15和mn16漏端的电流为is,根据差分对的跨导,电流ic与is 满足如下关系

22.ic=is+gm(δv)

ꢀꢀꢀ

(1)

23.式中gm表示由mos管mp7、mp8、mp11、mp12、mn13、mn14组成的传统差分放大器结构的跨导,而

△

v表示控制电压与参考电压之差。

24.因此电流ic的大小通过控制电压进行调整,而电流ic在通过mos管mn15~mn20和 mp15~mp18组成的电流镜进行镜像,令其镜像的电流大小为nic,而mos管mn15~mn24、 mp15~mp21、反向器q5~q8、电阻r1和r2、电容c1组成频率产生电路中的方波产生结构,其过程为,初始信号通过在上电阶段短暂打开mos管mn22将电容c1上的电压拉低到0v,此时6倍时钟频率为高电平,控制信号1为低电平,由mp20和mn23组成的传输门打开而由mp21与mn21组成的传输门关闭,由于mp19管子的开启,通过mos管mn19和mn20 镜像的电流mp19流过,不影响电容c1,由于mn24关断,通过mos管mp17和mp18流过的电流流入电容c1,电容c1上极板上的电压开始上升,当其超过反向器q5的阈值电压约为1.2v时,反相器输出2.4v的高电平,由于r1=r2,电容c1的下极板抬升1.2v,那么 c1的上极板瞬间抬升至2.4v,此时6倍时钟频率为低电平,控制信号1为高电平,那么由 mp20和mn23组成的传输门关闭而由mp21

与mn21组成的传输门打开,mn19与mn20 镜像的电流开始给电容c1的上极板放电,直到其小于1.2v,反相器q6输出低电平,电容 c1下极板由1.2v变为0v,其上极板也变为0v,即恢复到初始值,通过上述过程的循环,反相器q7可以输出占空比越为0.5的方波电压,其频率大小可以表达为下式

[0025][0026]

式中f

6倍频

表示6倍时钟频率的大小,其大小通过锁相环以及后级分频电路的1/6分频功能会被设置在6倍的片外时钟频率,v

th

为反相器q5的阈值电压,通常为1.2v,c1为电容 c1的容值大小,n为mos管mn15~mn20和mp15~mp18组成的电流镜的镜像比例。

[0027]

由is设置的中心频率大小在兆赫兹范围,本发明通过反相器固有的状态锁存与低延时特点可以有效实现多个兆赫兹频率的有效产生,而不会存在过长的方波上升延时与下降延时,影响具体占空比的设置。通过式(1)(2)可以知道本发明的频率控制基于一个中心频率,中心频率对应控制电压为1.2v,此时ic=is,频率的最大值与最小值分别约为

[0028]

通过本发明的时钟频率产生模块,可以将鉴相与电荷泵模块产生的控制电压转化为围绕is 设置的中心频率进行变化的6倍时钟频率,之所以设置6倍时钟频率,原因在于,6倍时钟频率的周期长度为片外时钟的1/6其自身周期的占空比也为1/2,因此通过分频分相模块可以实现最小1/12占空比的同步片外时钟信号以及最小30

°

的相位差,其具体实现过程见图4与图5。

[0029]

由于本发明结合了锁相环结构,时钟频率产生模块的频率为片外时钟的6倍,分频分相电路利用图4中的触发器l1~l3组成了一个8位状态机,其状态切换顺序如图5所示,通过格雷码的形式将状态s2~s7组成6个循环状态,6倍时钟频率每次上升沿到来时,状态切换一次,将s2~s7每循环一次组成一个输出时钟信号的周期,即可完成对6倍时钟频率的6分频功能。例如如图4虚线框中芯片内初始相位时钟为一个1/12占空比同步与片外时钟的信号,将状态s2的中6倍时钟频率的高电平作为输出时钟信号的高电平输出,即可完成1/12占空比的产生,由于状态s2与s7状态码的有效设置,舍去了000状态与111状态,因此s2~s7 每个状态只需要用两位d触发器的输出即可表示,在加上占空比为1/2的6倍时钟频率的高电平输入到与非门中,1/12占空比的芯片内初始相位时钟即可产生,此外由于引入了触发器 l1~l3的时钟信号即6倍时钟频率作为与非门的输入,为了避免时钟jitter,由下降沿触发的反相器l5与l4输入也需要引入到1/12占空比时钟的产生当中其原理就是利用其下降沿触发的特点,锁住与非输出的状态,而不让与非门输出在6倍频时钟变化时发生抖动,只有在需要用到6倍时钟频率作为与非门输入的时候才需要用到触发器l4和l5,其余不需要。

[0030]

利用图5中的各种状态,本发明可以输出占空比为1/12、1/6、1/3、1/2的时钟输出,通过将状态s2~s7中的1个或多个输出作为输出时钟的高电平其余作为低电平输出,具体见图 4虚线框例子,同时本发明还能输出相对于芯片内初始相位时钟由最小30

°

相位差的时钟信号,如虚线框中所示,状态s2输出的初始相位,状态s3中低电平时的6倍时钟频率即为与状态s2有90

°

相位差的时钟。

[0031]

本发明整体工作于锁相环的环路当中,因此涉及到其环路稳定性问题,需要通过图2中的片外补偿进行稳定性设置,锁相环的环路增益表达式为

[0032][0033]

式中i

cp

为鉴相与电荷泵电路中流过mos管mp3和mn4的电流,n、gm、c1、v

th

同式(1),rs,cs,cp为图2中片外补偿电阻阻值与电容容值。通过式(3)可以知道环路相位裕度可以很容易通过cp与rs组成的第二极点与rs与cs组成的零点设置在60

°

左右,带宽通过式(4)进行设置

[0034][0035]

图6所示为本发明同步片外650khz时钟时的工作波形,图7为锁相完成后的局部波形,通过图6可以看到上电时,控制电压被初始化到1.2v左右,即中心频率所在控制电压,此时由于片外时钟频率大于中心频率500khz,控制电压开始上升,直到片外时钟与芯片内初始相位时钟同相,如图7,图中还能看出芯片内初始相位时钟占空比为1/12,符合本发明的预期设计。

[0036]

图8为本发明多种相位与多种占空比输出仿真波形。通过图8的仿真波形可以知道本发明可以实现不同占空比与相位差的时钟信号输出,符合发明的预期。

[0037]

综上所述,本发明结合锁相环,方波产生电路以及数字分频分相的各自特点,发明了一种能够同步芯片外时钟,并且能够输出多种占空比与相位差的时钟电压信号,可以适用于采用了多相交错控制技术的电源芯片当中。此外,本发明锁相环自带初始化功能,避免了上电时同步片外时钟用时过长,本发明的6倍时钟频率方波产生电路有效利用反相器的高速低延时特点,保证在多个兆赫兹频率方波的工作中,上升下降延时不会过大,同时本发明通过对 6倍于片外时钟的6倍时钟频率进行分频分相可以输出多种占空比与相位差的时钟信号,适用于如今的各种电源管理芯片的控制技术。