一种时钟信号电磁辐射抑制电路、电路板及方法与流程

1.本发明涉及电磁兼容技术领域,特别涉及一种时钟信号电磁辐射抑制电路,电路板及方法。

背景技术:

2.随着信息技术类设备向高速、高灵敏度、高集成化、高稳定性的方向发展,对电磁兼容的要求也越来越苛刻,设备设计前期必须考虑电磁兼容的问题。对于高速数字系统的互连设备,时钟信号的电磁辐射问题较为严重。随着通信速率越来越高,时钟信号的频率也随之越来越高,时钟频率升高,意味着时钟信号的上升沿与下降沿越来越陡,上升沿时间和下降沿时间越来越短,对应于频域分量,频率就会越来越高,频率越高所对应的波长越短,可以利用的天线或等效天线的尺寸就会越短,电磁波更容易向空间辐射,带来严重的电磁干扰问题。

3.作为一种信息技术类设备的服务器,通常要和交换机协同使用,服务器中的基板管理控制器(bmc,baseboard management controller)通过专用网口与交换机物理层芯片互联,实现rgmii(reduced gigabit media independent interface)协议传输。通常,交换机物理层芯片的时钟i/o引脚对外输出时钟信号,供给基板管理控制器中的mac(media access control,媒体访问控制)模块使用;另一种普遍存在的情况是:未将交换机物理层芯片的时钟i/o引脚接入基板管理控制器的mac模块,相应地,时钟信号与基板管理控制器之间不进行连线。但在pcb设计时,无论是否将时钟信号接入基板管理控制器,都需要在pcb上保留一个时钟信号的测点,以供示波器探头抓取信号。在时钟信号不接入基板管理控制器的情况下,服务器pcb上的时钟信号走线呈现出“断头线”的形式,这会导致pcb上“断头线”部分的走线等效为天线,对外辐射电磁波,电磁波进一步通过空间耦合的方式,耦合到网口线缆上,网口线缆将机箱内部的电磁辐射噪声向空间辐射,造成电磁辐射超标。图1示出了现有设计中,125mhz时钟“断头线”造成的电磁辐射指标。从图1中可以看出,125mhz的4倍频(500mhz)的测试结果已超出了标准限定,造成服务器电磁辐射指标不达标。对于上述两种时钟信号的连接情况,若采用工程师人工判断,并设置芯片关闭未连接时钟的方式,将带来巨大的工作量,耗费大量人力成本。因此,亟需一种时钟信号电磁辐射抑制电路及方法,通过电路直接判断交换机物理层芯片发出的时钟信号是否接入基板管理控制器,并根据时钟信号是否接入基板管理控制器的实际情况,自动设置相关时钟信号的开启或关闭。

技术实现要素:

4.为了解决现有技术中,因印刷电路板兼容性设计,导致未接入基板管理控制器的时钟信号产生电磁辐射超标的问题,本发明实施例提供一种时钟信号电磁辐射抑制电路、电路板及方法,代替人工,自动关闭未接入基板管理控制器的时钟信号,以降低电磁辐射水平,使产品电磁辐射达到相应标准。

5.为了解决上述的一个或多个技术问题,本发明采用的技术方案如下:

6.第一方面,提供一种时钟信号电磁辐射抑制电路,该电路用于连接物理层芯片和基板管理控制器,抑制由物理层芯片发出的,但未接入基板管理控制器的时钟信号所产生的电磁辐射,电路包括:时钟判断模块,时钟关闭模块;

7.其中,时钟判断模块包括:运算放大子模块,滤波子模块,开关子模块,采样子模块,逻辑判断子模块;

8.运算放大子模块包括:运放第一端口、运放第二端口、运放第三端口、运放第四端口和运放第五端口,滤波子模块包括:滤波第一端口、滤波第二端口和滤波第三端口,开关子模块包括:开关第一端口、开关第二端口和开关第三端口,采样子模块包括:采样第一端口和采样第二端口,逻辑判断子模块包括:判断第一端口、判断第二端口和判断第三端口;

9.运放第一端口与基板管理控制器第一管脚电性连接,运放第四端口与电源电压连接,运放第五端口接地,运放第三端口与开关第一端口电性连接;

10.滤波第一端口与物理层芯片第一管脚电性连接,滤波第二端口接地,滤波第三端口与开关第二端口电性连接,滤波第三端口还与判断第一端口电性连接;

11.采样第一端口与基板管理控制器第二管脚电性连接,采样第二端口与判断第二端口电性连接;

12.判断第三端口与基板管理控制器第三管脚电性连接;

13.时钟关闭模块包括相互连接的基板管理控制器第四管脚和物理层芯片第二管脚。

14.进一步地,在时钟信号接入基板管理控制器的情况下,开关第三端口与采样第一端口电性连接。

15.进一步地,运算放大子模块包括运算放大器;

16.运算放大器的正输入端作为运放第一端口,运算放大器的负输入端作为运放第二端口,运算放大器的输出端作为运放第三端口,运算放大器的正电源端作为运放第四端口,运算放大器的负电源端作为运放第五端口。

17.进一步地,滤波子模块包括第一电阻r1和电容c;

18.第一电阻r1的一端作为滤波第二端口,第一电阻r1的另一端作为滤波第一端口,与电容c的一端电性连接,电容c的另一端作为滤波第三端口,接地。

19.进一步地,开关子模块包括金属-氧化物-半导体晶体管;

20.金属-氧化物-半导体晶体管的栅极g作为开关第一端口,金属-氧化物-半导体晶体管的漏极d作为开关第二端口,金属-氧化物-半导体晶体管的源极s作为开关第三端口。

21.进一步地,金属-氧化物-半导体晶体管为n型掺杂金属-氧化物-半导体晶体管。

22.进一步地,采样子模块包括第二电阻r2;

23.第二电阻r2的一端作为采样第一端口,第二电阻r2的另一端作为采样第二端口。

24.进一步地,逻辑判断子模块包括与门;

25.与门的第一输入端作为判断第一端口,与门的第二输入端作为判断第二端口,与门的输出端作为判断第三端口。

26.第二方面,提供一种时钟信号电磁辐射抑制电路板,电路板至少包括上述第一方面记载的一种时钟信号电磁辐射抑制电路;

27.其中,运算放大子模块,滤波子模块和开关子模块设置于距物理层芯片边缘第一预设距离的第一范围内;

28.采样子模块和逻辑判断子模块设置于距基板管理控制器边缘第二预设距离的第二范围内。

29.第三方面,提供一种时钟信号电磁辐射抑制方法,应用于上述第一方面记载的一种时钟信号电磁辐射抑制电路,方法包括:

30.从物理层芯片第一管脚获取时钟信号,并对时钟信号进行滤波;

31.对滤波后的时钟信号进行采样,获取采样信号,并将采样信号和滤波后的时钟信号分别送入判断第二端口和判断第一端口;

32.获取判断第三端口的信号有效值,并判断信号有效值是否小于预设阈值;

33.若是,则由基板管理控制器向物理层芯片发送时钟关闭指令。

34.进一步地,上述方法之前还包括:

35.对基板管理控制器及物理层芯片进行上电,使基板管理控制器和物理层芯片正常运行。

36.本发明实施例提供的技术方案带来的有益效果是:

37.1.通过实时本发明实施例公开的一种时钟信号电磁辐射抑制电路,能够通过检测基板管理控制器一侧的时钟信号,自动判断相应的时钟信号是否被基板管理控制器使用;

38.2.当采样子模块监测到基板管理控制器未接收物理层芯片发出的时钟信号,则自动切断相应的时钟链路,降低因时钟信号导致的电磁辐射效能;

39.3.若采样子模块监测到基板管理控制器接收物理层芯片发出的时钟信号,则维持当前电路的运行工作状态,不加以干预;

40.4.通过实时本发明实施例公开的一种时钟信号电磁辐射抑制电路,自动判断基板管理控制器的是否使用了物理层芯片发出的时钟信号,在保障将第电磁辐射的同时,减轻工程技术人员的工作量,节约人力成本。

附图说明

41.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

42.图1是125mhz时钟电磁辐射测试结果示意图;

43.图2是本发明实施例提供的一种时钟信号电磁辐射抑制电路模块示意图;

44.图3是本发明实施例提供的时钟信号未接入基板管理控制器的一种时钟信号电磁辐射抑制电路模块示意图;

45.图4是本发明实施例提供的时钟信号接入基板管理控制器的一种时钟信号电磁辐射抑制电路模块示意图;

46.图5是本发明实施例提供的时钟信号未接入基板管理控制器的一种时钟信号电磁辐射抑制电路示意图;

47.图6是本发明实施例提供的时钟信号接入基板管理控制器的一种时钟信号电磁辐射抑制电路示意图;

48.图7是本发明实施例提供的电路模块在电路板上设置范围示意图;

49.图8是对采用本发明实施例提供的一种时钟信号电磁辐射抑制电路板,基板管理控制器未接入125mhz时钟信号的服务器进行电磁辐射测试获得的测试结果示意图;

50.图9是本发明实施例提供的一种时钟信号电磁辐射抑制方法示意图。

具体实施方式

51.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明实施方式中的附图,对本发明实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

52.除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“一个”、“一”或者“该”等类似词语也不表示数量限制,而是表示存在至少一个。说明书附图中的编号,仅表示对各个功能部件或模块的区分,不表示部件或模块之间的逻辑关系。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

53.对于本技术说明书中涉及的元器件符号,在电路图中指代元器件的类型,并区分各个元器件,例如:r1,r2,c等;在相应的公式中表示元器件相应物理量的大小,以斜体加以区分,例如:电阻r1对应的电阻值为r1。

54.下面,将参照附图详细描述根据本公开的各个实施例。需要注意的是,在附图中,将相同的附图标记赋予基本上具有相同或类似结构和功能的组成部分,并且将省略关于它们的重复描述。

55.针对现有技术中,因印刷电路板兼容性设计,导致未接入基板管理控制器的时钟信号产生电磁辐射超标的问题。本发明实施例提供一种时钟信号电磁辐射抑制电路、电路板及方法,代替人工,自动关闭未接入基板管理控制器的时钟信号,以降低电磁辐射水平,使产品电磁辐射达到相应标准。

56.在一个实施例中,一种时钟信号电磁辐射抑制电路用于连接物理层芯片和基板管理控制器,抑制由物理层芯片发出的,但未接入基板管理控制器的时钟信号所产生的电磁辐射,上述时钟信号电磁辐射抑制电路包括:时钟判断模块1,时钟关闭模块2,如图2所示。

57.其中,时钟判断模块1包括:运算放大子模块11,滤波子模块12,开关子模块13,采样子模块14,逻辑判断子模块15,如图3所示。

58.运算放大子模块11包括:运放第一端口111、运放第二端口112、运放第三端口113、运放第四端口114和运放第五端口115,滤波子模块12包括:滤波第一端口121、滤波第二端口122和滤波第三端口123,开关子模块13包括:开关第一端口131、开关第二端口132和开关第三端口133,采样子模块14包括:采样第一端口141和采样第二端口142,逻辑判断子模块15包括:判断第一端口151、判断第二端口152和判断第三端口153。

59.运放第一端口111与基板管理控制器第一管脚电性连接,运放第四端口114与电源电压连接,运放第五端口115接地,运放第三端口113与开关第一端口131电性连接。其中,基板管理控制器第一管脚用于指示该基板管理控制器是否正常上电,基板管理控制器正常上电时,基板管理控制其第一管脚输出高电平。

60.在一个较优的实施方式中,运放第二端口112接地。在此连接方式下,运算放大子模块11具备高驱动能力,由运放第三端口113输出的电压足以驱动开关子模块13导通或者关闭。

61.在另一个实施方式中,运放第二端口112与运放第三端口113电性连接。在此连接方式下,运算放大子模块11作为电压跟随器,在开关子模块13选用器件的阈值电压小于基板管理控制器第一管脚输出电压的情况下,可以以此连接方式驱动上述开关子模块13。

62.滤波第一端口121与物理层芯片第一管脚电性连接,滤波第二端口122接地,滤波第三端口123与开关第二端口132电性连接,滤波第三端口123还与判断第一端口151电性连接。其中,物理层芯片第一管脚输出时钟信号。滤波子模块12用于有针对性地对电磁辐射频率进行滤波。

63.采样第一端口141还与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接,基板管理控制器第二管脚用于接收时钟信号,若布线未将时钟信号接入基板管理控制器第二管脚,如图3所示,采样第二端口142探测不到采样信号,判断第三端口153输出信号的有效值将小于预设阈值,基板管理控制器第三管脚接收到低电平。

64.在时钟信号接入基板管理控制器的情况下,采样第一端口141与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接。

65.判断第三端口153与基板管理控制器第三管脚电性连接。

66.基板管理控制器第三管脚接收的电平状态指示了基板管理控制器是否接入时钟信号。基板管理控制器第三管脚接收高电平,表示基板管理控制器接入时钟信号;基板管理控制器第三管脚接收低电平,表示基板管理控制器未接入时钟信号。

67.时钟关闭模块2包括相互连接的基板管理控制器第四管脚和物理层芯片第二管脚。当基板管理控制器上电经过预设时间后,若基板管理控制器第三管脚的电平为低电平,则判定信号未接入基板管理控制器。此时,基板管理控制器第一管脚输出低电平,使运放第三端口113的输出无法驱动开关子模块13,开关子模块13关断,切断时钟信号传输路径。与此同时,基板管理控制控制器第四管脚输出控制信号至物理层芯片第二管脚,对物理层芯片的内部寄存器进行设置,关闭物理层芯片的时钟信号从物理层芯片第一管脚输出的通路,物理层芯片第一管脚不再输出时钟信号。上述控制信号的具体形式,可以由用户自行定义,本技术不加以限定。

68.在时钟信号接入基板管理控制器的情况下,开关第三端口133与采样第一端口141电性连接,如图4所示。若基板管理控制器第二管脚接收时钟信号,则会在采样第二端口142输出采样信号,采样信号波形与时钟信号波形一致,判断第三端口153输出信号的有效值将大于预设阈值,基板管理控制器第三管脚接收到高电平。开关子模块13保持开启状态,时钟信号通过开启的开关子模块13,持续向基板管理控制器输入。

69.具体地,运算放大子模块11为运算放大器110;

70.运算放大器110的正输入端作为运放第一端口111,运算放大器110的负输入端作

为运放第二端口112,运算放大器110的输出端作为运放第三端口113,运算放大器110的正电源端作为运放第四端口114,运算放大器110的负电源端作为运放第五端口115。

71.具体地,滤波子模块12包括第一电阻r1和电容c;

72.第一电阻r1的一端作为滤波第二端口122,第一电阻r1的另一端作为滤波第一端口121,与电容c的一端电性连接,电容c的另一端作为滤波第三端口123,接地。

73.该滤波子模块12的截止频率f

res

=1/2πr1c,通过调整第一电阻r1或电容c的具体数值,可以调整滤波子模块12的截止频率,对相应频率时钟信号携带的噪声进行滤波。

74.具体地,开关子模块13包括金属-氧化物-半导体晶体管130;

75.金属-氧化物-半导体晶体管130的栅极g作为开关第一端口131,金属-氧化物-半导体晶体管130的漏极d作为开关第二端口132,金属-氧化物-半导体晶体管130的源极s作为开关第三端口133。

76.进一步地,金属-氧化物-半导体晶体管130为n型掺杂金属-氧化物-半导体晶体管。

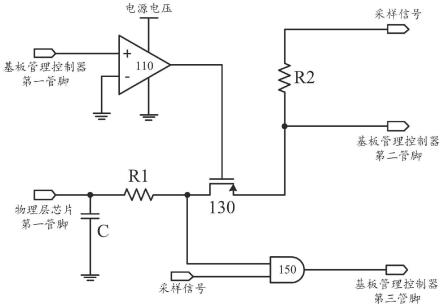

77.当开关第一端口131接收到高电平时,开关子模块13开启,经滤波的时钟信号向开关子模块13后端电路传输。

78.当开关第一端口131接收到低电平时,开关子模块13关闭,经滤波的时钟信号无法经过开关子模块13向后传输。

79.具体地,采样子模块14包括第二电阻r2;

80.第二电阻r2的一端作为采样第一端口141,第二电阻r2的另一端作为采样第二端口142。

81.具体地,逻辑判断子模块15包括与门150;

82.与门150的第一输入端作为判断第一端口151,与门150的第二输入端作为判断第二端口152,与门150的输出端作为判断第三端口153。

83.测量第三端口153可以获得其输出电压有效值,并以此有效值区分相应高低电平。

84.对应上述时钟信号未接入基板管理控制器的情况,一种时钟信号电磁辐射抑制电路的具体形式如图5所示。

85.对应上述时钟信号接入基板管理控制器的情况,一种时钟信号电磁辐射抑制电路的具体形式如图6所示。

86.在另一个实施例中,一种时钟信号电磁辐射抑制电路板,电路板至少包括上述第一方面记载的一种时钟信号电磁辐射抑制电路;

87.其中,运算放大子模块11,滤波子模块12和开关子模块13设置于距物理层芯片边缘第一预设距离的第一范围内;

88.采样子模块14和逻辑判断子模块15设置于距基板管理控制器边缘第二预设距离的第二范围内。

89.上述第一范围为距基板管理控制器边缘120mil的平行线围成的图形,扣除基板管理控制器部分的面积;

90.上述第二范围为距基板管理控制器边缘120mil的平行线围成的图形,扣除基板管理控制器部分的面积。相应模块分布的示意图如图7所示,图7仅用于示意将相应模块设置于第一范围、第二范围内,对于模块具体位置,本技术不加以限定。

91.优选地,该电路板为印刷电路板。

92.在其中一个实施方式中,对于125mhz时钟信号未接入基板管理控制器的情况,对上述时钟信号电磁辐射抑制电路板进行电磁辐射测试,结果如图8所示。电磁辐射结果在标准以内。

93.在另一个实施例中,如图9所示,一种时钟信号电磁辐射抑制方法包括:

94.步骤s1:从物理层芯片第一管脚获取时钟信号,并对时钟信号进行滤波;

95.步骤s2:对滤波后的时钟信号进行采样,获取采样信号,并将采样信号和滤波后的时钟信号分别送入判断第二端口和判断第一端口;

96.若印刷电路板上存在时钟信号与基板管理控制器的连接,则可获取时钟信号的采样波形;

97.若印刷电路板上不存在的时钟信号与基板管理控制器的连接,则无法获取时钟信号的采样波形。

98.步骤s3:获取判断第三端口的信号有效值,并判断信号有效值是否小于预设阈值;

99.若是,则步骤s4:由基板管理控制器向物理层芯片发送时钟关闭指令;

100.若否,则步骤s4

′

:保持时钟信号发送。

101.优选地,一种时钟信号电磁辐射抑制方法之前还包括:

102.步骤s0:对基板管理控制器及物理层芯片进行上电,使基板管理控制器和物理层芯片正常运行。

103.上述所有可选技术方案,可以采用任意结合形成本发明的可选实施例,在此不再一一赘述。

104.实施例一

105.下面结合图2,3,5具体阐述一种时钟信号电磁辐射抑制电路。该电路用于连接物理层芯片和基板管理控制器,抑制由物理层芯片发出的,但未接入基板管理控制器的时钟信号所产生的电磁辐射,上述时钟信号电磁辐射抑制电路包括:时钟判断模块1,时钟关闭模块2,如图2所示。

106.其中,时钟判断模块1包括:运算放大子模块11,滤波子模块12,开关子模块13,采样子模块14,逻辑判断子模块15,如图3所示。

107.运算放大子模块11包括:运放第一端口111、运放第二端口112、运放第三端口113、运放第四端口114和运放第五端口115,滤波子模块12包括:滤波第一端口121、滤波第二端口122和滤波第三端口123,开关子模块13包括:开关第一端口131、开关第二端口132和开关第三端口133,采样子模块14包括:采样第一端口141和采样第二端口142,逻辑判断子模块15包括:判断第一端口151、判断第二端口152和判断第三端口153。

108.本实施例中,基板管理控制器型号为ast2600,时钟信号频率为125mhz,时钟信号未接入基板管理控制器。

109.运放第一端口111与基板管理控制器第一管脚电性连接,运放第四端口114与电源电压连接,运放第五端口115接地,运放第三端口113与开关第一端口131电性连接。其中,基板管理控制器第一管脚用于指示该基板管理控制器是否正常上电,基板管理控制器正常上电时,基板管理控制其第一管脚输出高电平。

110.运放第二端口112接地,由运放第三端口113输出的电压足以驱动开关子模块13导

通或者关闭。

111.滤波第一端口121与物理层芯片第一管脚电性连接,滤波第二端口122接地,滤波第三端口123与开关第二端口132电性连接,滤波第三端口123还与判断第一端口151电性连接。其中,物理层芯片第一管脚输出时钟信号。滤波子模块12用于有针对性地对电磁辐射频率进行滤波。

112.采样第一端口141还与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接,基板管理控制器第二管脚用于接收时钟信号,若布线未将时钟信号接入基板管理控制器第二管脚,如图3所示,采样第二端口142探测不到采样信号,判断第三端口153输出信号的有效值将小于预设阈值,基板管理控制器第三管脚接收到低电平。

113.判断第三端口153与基板管理控制器第三管脚电性连接。

114.基板管理控制器第三管脚接收的电平状态指示了基板管理控制器是否接入时钟信号。基板管理控制器第三管脚接收高电平,表示基板管理控制器接入时钟信号;基板管理控制器第三管脚接收低电平,表示基板管理控制器未接入时钟信号。

115.采样第一端口141与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接。

116.判断第三端口153与基板管理控制器第三管脚电性连接。

117.基板管理控制器第三管脚接收的电平状态指示了基板管理控制器是否接入时钟信号。基板管理控制器第三管脚接收低电平,表示基板管理控制器未接入时钟信号。

118.时钟关闭模块2包括相互连接的基板管理控制器第四管脚和物理层芯片第二管脚。当基板管理控制器上电经过预设时间后,若基板管理控制器第三管脚的电平为低电平,则判定信号未接入基板管理控制器。此时,基板管理控制器第一管脚输出低电平,使运放第三端口113的输出无法驱动开关子模块13,开关子模块13关断,切断时钟信号传输路径。与此同时,基板管理控制控制器第四管脚输出控制信号至物理层芯片第二管脚,对物理层芯片的内部寄存器进行设置,关闭物理层芯片的时钟信号从物理层芯片第一管脚输出的通路,物理层芯片第一管脚不再输出时钟信号。上述控制信号的具体形式,可以由用户自行定义,本技术不加以限定。

119.具体地,运算放大子模块11为运算放大器110;

120.运算放大器110的正输入端作为运放第一端口111,运算放大器110的负输入端作为运放第二端口112,运算放大器110的输出端作为运放第三端口113,运算放大器110的正电源端作为运放第四端口114,运算放大器110的负电源端作为运放第五端口115。

121.具体地,滤波子模块12包括第一电阻r1和电容c;

122.第一电阻r1的一端作为滤波第二端口122,第一电阻r1的另一端作为滤波第一端口121,与电容c的一端电性连接,电容c的另一端作为滤波第三端口123,接地。

123.该滤波子模块12的截止频率f

res

=1/2πr1c,通过调整第一电阻r1或电容c的具体数值,可以调整滤波子模块12的截止频率,对相应频率时钟信号携带的噪声进行滤波。

124.具体地,开关子模块13包括金属-氧化物-半导体晶体管130;

125.金属-氧化物-半导体晶体管130的栅极g作为开关第一端口131,金属-氧化物-半导体晶体管130的漏极d作为开关第二端口132,金属-氧化物-半导体晶体管130的源极s作为开关第三端口133。

126.进一步地,金属-氧化物-半导体晶体管130为n型掺杂金属-氧化物-半导体晶体管。

127.当开关第一端口131接收到高电平时,开关子模块13开启,经滤波的时钟信号向开关子模块13后端电路传输;

128.当开关第一端口131接收到低电平时,开关子模块13关闭,经滤波的时钟信号无法经过开关子模块13向后传输。

129.具体地,采样子模块14包括第二电阻r2;

130.第二电阻r2的一端作为采样第一端口141,第二电阻r2的另一端作为采样第二端口142。

131.具体地,逻辑判断子模块15包括与门150;

132.与门150的第一输入端作为判断第一端口151,与门150的第二输入端作为判断第二端口152,与门150的输出端作为判断第三端口153。

133.对于时钟信号未接入基板管理控制器的情况,一种时钟信号电磁辐射抑制电路的具体形式如图5所示。测量第三端口153可以获得其输出电压有效值,此时电压有效值低于预设阈值,被判定为低电平。

134.实施例二

135.下面结合图2,4,6具体阐述一种时钟信号电磁辐射抑制电路,该电路用于连接物理层芯片和基板管理控制器,抑制由物理层芯片发出的,但未接入基板管理控制器的时钟信号所产生的电磁辐射,上述时钟信号电磁辐射抑制电路包括:时钟判断模块1,时钟关闭模块2,如图2所示。

136.其中,时钟判断模块1包括:运算放大子模块11,滤波子模块12,开关子模块13,采样子模块14,逻辑判断子模块15,如图4所示。

137.运算放大子模块11包括:运放第一端口111、运放第二端口112、运放第三端口113、运放第四端口114和运放第五端口115,滤波子模块12包括:滤波第一端口121、滤波第二端口122和滤波第三端口123,开关子模块13包括:开关第一端口131、开关第二端口132和开关第三端口133,采样子模块14包括:采样第一端口141和采样第二端口142,逻辑判断子模块15包括:判断第一端口151、判断第二端口152和判断第三端口153。

138.本实施例中,基板管理控制器型号为ast2600,时钟信号频率为125mhz,时钟信号接入基板管理控制器。

139.运放第一端口111与基板管理控制器第一管脚电性连接,运放第四端口114与电源电压连接,运放第五端口115接地,运放第三端口113与开关第一端口131电性连接。其中,基板管理控制器第一管脚用于指示该基板管理控制器是否正常上电,基板管理控制器正常上电时,基板管理控制其第一管脚输出高电平。

140.运放第二端口112接地,由运放第三端口113输出的电压足以驱动开关子模块13导通或者关闭。

141.滤波第一端口121与物理层芯片第一管脚电性连接,滤波第二端口122接地,滤波第三端口123与开关第二端口132电性连接,滤波第三端口123还与判断第一端口151电性连接。其中,物理层芯片第一管脚输出时钟信号。滤波子模块12用于有针对性地对电磁辐射频率进行滤波。

142.开关第三端口133与采样第一端口141电性连接,采样第一端口141还与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接。基板管理控制器第二管脚用于接收时钟信号,若基板管理控制器第二管脚接收时钟信号,则会在采样第二端口142输出采样信号,采样信号波形与时钟信号波形一致,判断第三端口153输出信号的有效值将大于预设阈值,基板管理控制器第三管脚接收到高电平。

143.在本实施例中,时钟信号接入基板管理控制器,采样第一端口141与基板管理控制器第二管脚电性连接,采样第二端口142与判断第二端口152电性连接。

144.判断第三端口153与基板管理控制器第三管脚电性连接。

145.基板管理控制器第三管脚接收的电平状态指示了基板管理控制器是否接入时钟信号。基板管理控制器第三管脚接收高电平,表示基板管理控制器接入时钟信号。

146.在时钟信号接入基板管理控制器的情况下,开关第三端口133与采样第一端口141电性连接,如图4所示。若基板管理控制器第二管脚接收时钟信号,则会在采样第二端口142输出采样信号,采样信号波形与时钟信号波形一致,判断第三端口153输出信号的有效值将大于预设阈值,基板管理控制器第三管脚接收到高电平。开关子模块13保持开启状态,时钟信号通过开启的开关子模块13,持续向基板管理控制器输入。

147.时钟关闭模块2包括相互连接的基板管理控制器第四管脚和物理层芯片第二管脚。

148.具体地,运算放大子模块11为运算放大器110;

149.运算放大器110的正输入端作为运放第一端口111,运算放大器110的负输入端作为运放第二端口112,运算放大器110的输出端作为运放第三端口113,运算放大器110的正电源端作为运放第四端口114,运算放大器110的负电源端作为运放第五端口115。

150.具体地,滤波子模块12包括第一电阻r1和电容c;

151.第一电阻r1的一端作为滤波第二端口122,第一电阻r1的另一端作为滤波第一端口121,与电容c的一端电性连接,电容c的另一端作为滤波第三端口123,接地。

152.该滤波子模块12的截止频率f

res

=1/2πr1c,通过调整第一电阻r1或电容c的具体数值,可以调整滤波子模块12的截止频率,对相应频率时钟信号携带的噪声进行滤波。

153.具体地,开关子模块13包括金属-氧化物-半导体晶体管130;

154.金属-氧化物-半导体晶体管130的栅极g作为开关第一端口131,金属-氧化物-半导体晶体管130的漏极d作为开关第二端口132,金属-氧化物-半导体晶体管130的源极s作为开关第三端口133。

155.进一步地,金属-氧化物-半导体晶体管130为n型掺杂金属-氧化物-半导体晶体管。

156.当开关第一端口131接收到高电平时,开关子模块13开启,经滤波的时钟信号向开关子模块13后端电路传输。

157.具体地,采样子模块14包括第二电阻r2;

158.第二电阻r2的一端作为采样第一端口141,第二电阻r2的另一端作为采样第二端口142。

159.具体地,逻辑判断子模块15包括与门150;

160.与门150的第一输入端作为判断第一端口151,与门150的第二输入端作为判断第

二端口152,与门150的输出端作为判断第三端口153。

161.测量第三端口153可以获得其输出电压有效值,并以此有效值区分相应高低电平。

162.对应上述时钟信号接入基板管理控制器的情况,一种时钟信号电磁辐射抑制电路的具体形式如图6所示。

163.实施例三

164.下面结合图7,具体阐述一种时钟信号电磁辐射抑制电路板,电路板至少包括上述第一方面记载的一种时钟信号电磁辐射抑制电路。该电路板为印刷电路板。

165.其中,运算放大子模块11,滤波子模块12和开关子模块13设置于距物理层芯片边缘第一预设距离的第一范围内。

166.上述第一范围为距基板管理控制器边缘120mil的平行线围成的图形,扣除基板管理控制器部分的面积;上述第二范围为距基板管理控制器边缘120mil的平行线围成的图形,扣除基板管理控制器部分的面积,如图7所示。

167.图7示意了,将相应模块设置于第一范围、第二范围内,而不限定模块具体设置的位置。

168.采样子模块14和逻辑判断子模块15设置于距基板管理控制器边缘第二预设距离的第二范围内。

169.实施例四

170.下面结合图8,阐述一种时钟信号电磁辐射抑制方法,包括:

171.步骤s1:从物理层芯片第一管脚获取时钟信号,并对时钟信号进行滤波;

172.步骤s2:对滤波后的时钟信号进行采样,获取采样信号,并将采样信号和滤波后的时钟信号分别送入判断第二端口和判断第一端口;

173.步骤s3:获取判断第三端口的信号有效值,并判断信号有效值是否小于预设阈值;

174.若是,则步骤s4:由基板管理控制器向物理层芯片发送时钟关闭指令;

175.若否,则步骤s4

′

:保持时钟信号发送。

176.在其中的一个较优的实施方式中,在一种时钟信号电磁辐射抑制方法之前还包括:

177.步骤s0:对基板管理控制器及物理层芯片进行上电,使基板管理控制器和物理层芯片正常运行。

178.特别地,根据本技术的实施例,上文参考流程图描述的过程可以被实现为计算机软件程序。例如,本技术的实施例包括一种计算机程序产品,其包括装载在计算机可读介质上的计算机程序,该计算机程序包含用于执行流程图所示的方法的程序代码。在这样的实施例中,该计算机程序可以通过通信装置从网络上被下载和安装,或者从存储器被安装,或者从rom被安装。在该计算机程序被外部处理器执行时,执行本技术的实施例的方法中限定的上述功能。

179.需要说明的是,本技术的实施例的计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质或者是上述两者的任意组合。计算机可读存储介质例如可以是——但不限于——电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子可以包括但不限于:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机访问存储器(ram)、只读存储器(rom)、可擦式可编程只读

存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本技术的实施例中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。而在本技术的实施例中,计算机可读信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读信号介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于:电线、光缆、rf(radio frequency,射频)等等,或者上述的任意合适的组合。

180.上述计算机可读介质可以是上述服务器中所包含的;也可以是单独存在,而未装配入该服务器中。上述计算机可读介质承载有一个或者多个程序,当上述一个或者多个程序被该服务器执行时,使得该服务器:响应于检测到终端的外设模式未激活时,获取终端上应用的帧率;在帧率满足息屏条件时,判断用户是否正在获取终端的屏幕信息;响应于判断结果为用户未获取终端的屏幕信息,控制屏幕进入立即暗淡模式。

181.可以以一种或多种程序设计语言或其组合来编写用于执行本技术的实施例的操作的计算机程序代码,程序设计语言包括面向对象的程序设计语言—诸如java,smalltalk,c++,还包括常规的过程式程序设计语言—诸如“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络——包括局域网(lan)或广域网(wan)—连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

182.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于系统或系统实施例而言,由于其基本相似于方法实施例,所以描述得比较简单,相关之处参见方法实施例的部分说明即可。以上所描述的系统及系统实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。本领域普通技术人员在不付出创造性劳动的情况下,即可以理解并实施。

183.以上对本技术所提供的技术方案进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的一般技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本技术的限制。

184.以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1