功率放大器及平衡数字输出信号的上升和下降时间的方法与流程

功率放大器及平衡数字输出信号的上升和下降时间的方法

1.本技术是申请号为201880001851.4的中国专利申请的分案申请,原申请的申请日为2018年08月10日,名称为“功率放大器及平衡数字输出信号的上升和下降时间的方法”。

技术领域

2.本发明涉及开关模式功率放大器,其在许多方面类似于d类功率放大器的操作和架构。

背景技术:

3.存在多种功率放大器,其可分为两类:经典的、非开关放大器,如a类、b类、ab类、c类,以及开关模式放大器,如d类、e类和f类。非开关放大器具有对于特定的预定导通角在线性区域中工作的有源元件,并产生与输入信号或输入信号的一部分成比例的经放大的输出信号。因为导通角的相对大部分位于晶体管的线性区域中从而导致了功率耗散,因此非开关放大器具有相对低的功率附加效率(pae,power-added efficiency),而开关放大器可以实现100%的理论效率。由于便携式和可穿戴电子设备已经普及,对更小、更轻和更节能的电子设备的需求也增加了。降低开关模式放大器中晶体管功率耗散所需的快速转换(方波)也会导致信号谐波中出现高频内容。谐波可能超过标准监管机构(如美国联邦通信委员会(fcc,federal communications commission)或etsi)设定的带外杂散发射极限。

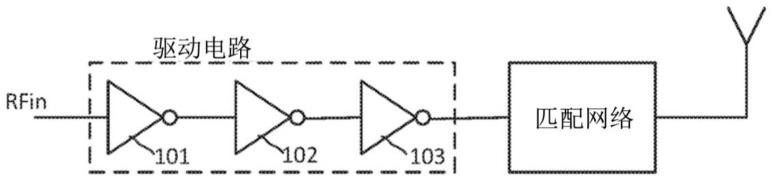

4.图1a是理想的d类放大器100的框图。d类放大器包括级联连接的反相放大级101、102和103。射频(rf)输入信号rfin是具有50%占空比的方波。50%占空比是指在每个周期的一半期间具有高电压(“1”)并且在其余占空比期间具有低电压(“0”)的方波形。图1b是图1a的功能等效电路。每个反相放大级包括串联连接在电源vdd和地之间的p-通道金属氧化物半导体(pmos,p-channel metal oxide semiconductor)设备和n-通道金属氧化物半导体(nmos,n-channel metal oxide semiconductor)设备。理想的d类放大器100通过在完全接通和完全断开之间切换来操作。当处于完全接通模式时,通过功率晶体管的电流处于最大值,但电压处于最小值,因此功耗最小。当处于完全断开模式时,功率晶体管两端的电压处于最大值,但电流处于最小值,因此功耗也最小。

5.图1c是说明反相放大级中的寄生电容的电路图。参考图1c,反相放大级在栅极和地之间具有输入寄生电容c1(包括pfet栅极到漏极电容、pfet栅极到源极电容、nfet栅极到漏极电容、以及nfet栅极到源极电容),在pmos晶体管的源极和漏极之间具有寄生电容c2,在nmos晶体管的漏极和源极之间具有寄生电容c3。在操作中,反相放大级产生输出信号rfout并将rfout信号施加到天线以进行传输。因为寄生电容c1、c2和c3由于输入信号并且由于pmos或nmos之一“导通”而进行充电,寄生电容导致信号的上升和下降时间延迟。由于上升时间的延迟可能不等于下降时间的延迟,因此可能发生脉冲宽度失真,并且可能在任何实际设计中发生,特别是在工艺和温度上。

6.图1d是示出穿过反相放大级的信号的上升和下降时间的图。如图1d所示,由于寄生电容的充电和放电,反相放大级输出端的信号具有缓慢的上升沿和下降沿,当两个晶体

管导通时,在慢转换期间消耗相对大的功率。因为pmos和nmos晶体管之间的电子迁移率不同,所以沿的上升和下降时间可能不匹配。沿的上升和下降时间的不匹配导致占空比的失真,这导致通常不存在的偶次谐波出现。二次谐波是偶次谐波中最成问题的,并且经常被挑选出来用于强调。

7.图2a是示出具有50%占空比的理想方波的图。图2b是示出由具有50%占空比的理想方波产生的谐波的图。如图2b所示,奇次谐波,即三次谐波h3、五次谐波h5和七次谐波h7超过fcc发射极限。解决谐波发射问题的一种方法是在放大器的输出端添加低通滤波器和带阻(陷波)滤波器,以滤除任何不需要的谐波。图2c是示出通过具有在三次谐波h3处的陷波(带通滤波器)的低通滤波器以满足fcc发射极限的谐波的图。

8.图3a是示出具有脉冲宽度失真的方波的图,即非50%占空比。请注意,附图不一定按比例绘制,此处提供的数值仅用于说明目的。参考图3a,输出信号可以是40%(在实践中更接近48%)的时间,并且0v是60%(在实践中更接近52%)的时间。图3b是示出由非50%占空比的方波产生的谐波的图,而基频保持不变。如图3b所示,非50%的占空比将产生超过fcc发射极限的偶次谐波2。如图3c所示,由于其紧密接近基波,所以二次谐波是最成问题的。降低二次谐波的一种方法是在放大器输出端增加额外的带阻(陷波)滤波器,以二次谐波为目标。这种复杂的滤波器通常不可能与同一集成电路中的放大器集成。此外,无论是芯片上还是芯片外,这种滤波器都会将功率损耗引入基频。图3c是示出通过具有调谐到三次谐波h3的陷波滤波器的低通滤波器的谐波的图。如图3c所示,高次谐波(例如,h4、h5、h6等)被低通滤波器很好地衰减,但是二次谐波相对接近基频,因此在h2处增加陷波也可能影响基频的频率响应,即,以二次谐波h2为目标的陷波滤波器可能在基频处表现出一些衰减,并且不利地降低输出功率和效率。

9.对于用于音频应用的d类放大器,通过脉冲宽度调制将音频信号调制到高频方波上。在基本开关频率下有效放大经脉冲宽度调制的方波之后,可以通过低通滤波器容易地消除基本开关频率以及开关频率的所有谐波,从而留下感兴趣的音频信号。由于开关频率和谐波距离音频非常远,因此低通滤波器就足够了。音频应用中不需要针对特定谐波的其他陷波。在所提出的rf d类放大器的情况下,基本开关频率是(待通过天线放大和发送的)感兴趣的频率。所需信息是通过相位或频率调制来调制的,其保持理想的50%占空比(开关频率不是脉冲宽度调制的,而是相位或频率调制的)。因此,滤波要求是完全不同的,因为只需去除基波的谐波,而不是基本开关频率本身。遗憾的是,由于所需的高q因子,在射频(rf)应用中不能以合理的成本实现这种低通滤波器。片外saw或baw滤波器增加了成本,并且显着损失了1db或更多。

10.因此,需要控制(频率或相位调制的)d类放大器的输出信号的上升和下降时间,以防止方波偏离50%占空比,导致二次谐波的出现。

技术实现要素:

11.本公开的实施例提供了可以减少开关模式功率放大器中的谐波的电路、设备和方法。

12.根据本公开的实施例,d类功率放大器包括:驱动电路,具有用于接收射频(rf)信号的输入、用于输出数字输出信号的输出、以及用于接收偏置信号的偏置端口;以及偏置电

路,具有耦合到所述驱动电路的所述输出以用于接收所述数字输出信号的第一输入、具有耦合到所述驱动电路的所述输入以用于接收所述rf信号的第二输入、以及耦合到所述驱动电路的所述偏置端口以用于向所述驱动电路提供所述偏置信号的输出。

13.在一个实施例中,所述rf信号是具有50%占空比的方波。

14.在一个实施例中,所述偏置电路还包括:第一平均电路,被配置为确定所述数字输出信号的第一平均电压值;第二平均电路,被配置为确定所述rf信号的第二平均电压值;以及比较器,被配置为基于所述第一平均电压值和所述第二平均电压值之间的差产生偏置电压信号。

15.在一个实施例中,所述比较器是差分运算放大器,具有用于接收所述数字输出信号的第一输入、用于接收所述rf信号的第二输入、以及用于输出所述偏置电压信号的输出。

16.在一个实施例中,所述第一平均电路包括第一运算放大器,所述第一运算放大器具有耦合到所述数字输出信号的多个输入并且被配置为对与所述数字输出信号的载波信号子集相关联的电压或电流进行求和,并且所述第二平均电路包括第二运算放大器,所述第二运算放大器具有耦合到所述rf信号的多个输入并且被配置为对与所述rf信号的载波信号子集相关联的电压或电流进行求和。

17.在一个实施例中,所述驱动电路还包括:第一晶体管,具有耦合到所述rf信号的栅极;第二晶体管,具有耦合到所述rf信号的栅极;第一串联晶体管,设置在所述第一晶体管和所述驱动电路的所述输出之间,并具有耦合到所述偏置信号的栅极;第二串联晶体管,设置在所述驱动电路的所述输出和所述第二晶体管之间,并具有耦合到所述偏置信号的栅极。所述第一晶体管、所述第二晶体管,所述第一串联晶体管和所述第二串联晶体管串联连接在电源电压和地之间。

18.在一个实施例中,所述第一晶体管是pmos晶体管,所述第一串联晶体管是pmos晶体管,所述第二晶体管是nmos晶体管,并且所述第二串联晶体管是nmos晶体管。

19.在一个实施例中,所述第一串联晶体管和所述第二串联晶体管平衡数字输出信号的上升时间和下降时间,以获得所述数字输出信号的50%占空比。

20.在一个实施例中,d类功率放大器还包括:第一路径,具有设置在所述rf信号和所述第一晶体管的所述栅极之间的第一多个逆变器,以及;第二路径,具有设置在所述rf信号和所述第二晶体管的所述栅极之间的第二多个逆变器。

21.在一个实施例中,所述第一多个逆变器包括串联连接的第一对逆变器,并且所述第二多个逆变器包括串联连接的第二对逆变器。

22.本发明的实施例还提供了一种用于平衡数字输出信号的上升和下降时间的方法。该方法可包括:由驱动电路接收射频(rf)信号;由驱动电路产生数字输出信号;由偏置电路确定与接收的rf信号相关联的第一平均电压值;确定与所述数字输出信号相关联的第二平均电压值;通过比较第一平均电压值和第二平均电压值产生偏置电压信号;以及响应于所述偏置电压信号平衡所述数字输出信号的所述上升和下降时间,以获得所述数字输出信号的50%占空比。

23.以下详细描述连同附图将有助于更好地理解本发明的本质和优点。

附图说明

24.在此提及并构成本文一部分的附图示出了本公开的实施例。附图与说明书一起用于解释本发明的原理。

25.图1a是可用于描述本发明的理想d类放大器的框图。

26.图1b是图1a的功能等效电路。

27.图1c是说明反相放大级中的寄生电容的电路图。

28.图1d是示出穿过反相放大级的信号的上升和下降时间的图。

29.图2a是说明具有50%占空比的理想方波的图,用于解释本发明的实施例。

30.图2b是示出由具有50%占空比的理想方波产生的谐波的图。

31.图2c是示出通过具有调谐到三次谐波频率的陷波滤波器的低通滤波器的谐波的图。

32.图3a是示出具有脉冲宽度失真的方波的图,即非50%占空比。

33.图3b是示出由非50%占空比的方波产生的谐波的图,而基频保持不变。

34.图3c是示出通过具有调谐到三次谐波的陷波滤波器的低通滤波器的谐波的图。

35.图4是可用于解释本发明实施例的相移键控(psk)波形的数据位流和数据编码的图形表示。

36.图5是根据本发明实施例的功率放大器电路500的简化框图。

37.图6是根据本发明实施例的偏置电路的简化电路图。

38.图6a是根据本发明实施例的示例性平均电路。

39.图6b是根据本发明另一实施例的示例性平均电路。

40.图7是根据本发明实施例的具有上升和下降时间调节电路的d类放大器的简化电路图。

41.图8是根据本发明另一实施例的功率放大器电路的简化框图。

42.图8a是根据本发明另一实施例的偏置电路的简化电路图。

43.图9是示出根据本发明示例性实施例的操作d类放大器的方法的简化流程图。

具体实施方式

44.在以下描述中,提供了许多具体细节以便透彻理解本发明。然而,本领域技术人员应该理解,可以在没有这些细节中的一个或多个的情况下实现本发明。在其他示例中,出于简洁的目的,将不描述本领域中已知的特征和技术。

45.应当理解,附图未按比例绘制,并且类似的附图标记用于表示类似的元件。这里参考功能框图描述了本发明的实施例,这些功能框图是本发明的理想化实施例(和中间结构)的示意图。

46.应当理解,当元件或组件被称为“连接到”或“耦合到”另一元件或组件时,它可以连接或耦合到另一元件或组件,或者也可能存在中间元件或组件。相反,当元件或组件被称为“直接连接到”或“直接耦合到”另一元件或组件时,在它们之间不存在中间元件或组件。应当理解,尽管这里可以使用术语“第一”、“第二”、“第三”等来描述各种元件、组件,这些元件、组件、区域不应受这些术语的限制。这些术语仅用于将一个元素、组件与另一个元素、组件区分开来。因此,在不脱离本发明的教导的情况下,下面讨论的第一元件、组件可以被称

为第二元件、组件。如这里所使用的,术语“逻辑低”、“低状态”、“低电平”、“逻辑低电平”、“低”或“0”可互换使用。术语“逻辑高”、“高状态”、“高电平”、“逻辑高电平”、“高”或“1”可互换使用。

47.如本文所用,术语“一”、“一个”和“该”可包括单数和复数引用。将进一步理解,当在本说明书中使用时,术语“包括”、“包含”、“具有”及其变体指定所述特征、步骤、操作、元件和/或组件的存在,但是不排除存在或添加一个或多个其他特征、步骤、操作、元件、组件和/或组。相反,当在本说明书中使用时,术语“由......组成”指定所述特征、步骤、操作、元件和/或组件,并且排除了附加特征、步骤、操作、元件和/或组件。此外,如本文所使用的,词语“和/或”可以指代并涵盖一个或多个相关所列项目的任何可能组合。

48.应当理解,本文提供的每个具体数值应被解释为仅是说明性的而非限制性的。因此,示例性实施例的其他示例可以具有不同的值。

49.图4示出了用于调制载波信号的二进制相移键控(bpsk)波形信号的基本形式。参考图4,输入数据信号包括比特流,例如,在时隙401中发送的第一二进制“1”,在时隙402中发送的第二二进制“1”,在时隙403中发送的二进制“0”等。在psk调制过程中,发送的信息包含在发送信号的相位中。在时隙402和403之间,数据从“1”变为“0”。数据转换在时间411处以180

°

相位反转示出。应当理解,bpsk被示出用于描述本发明的实施例,并且不应该是限制性的。各种psk方案通常用于在通信系统中传输信息,例如,dpsk、qpsk、dqpsk、8dpsk等。也可以使用例如频移键控(fsk)、gfsk等的其他调制方案。数据信号(比特流)的相位信息(psk)或频率信息(fsk)可以被提供给以比特流频率的几倍(例如,本地振荡器频率)频率工作的数字调制器(为简单起见未在此处示出)。在下文中,经调制的载波信号被称为“rf数据”或是方波信号的rf数据(没有引号

“”

)。

50.图5是根据本发明实施例的功率放大器电路500的简化框图。参考图5,功率放大器电路500包括驱动电路501、放大器电路503、匹配网络505和耦合到匹配网络505的输出的天线507。功率放大器电路500还包括偏置电路509。驱动电路501被配置为接收经调制的载波信号“rf数据”(例如,用数据信号的相位或频率信息调制的本地振荡器信号)并提供轨到轨数字输出信号513。放大器电路503接收信号513,并且向匹配网络505输出经放大的输出信号515。在一些实施例中,如果驱动电路产生足够的输出功率以直接驱动天线507,则可以省略放大器电路503。在一个实施例中,匹配网络505可以是低通滤波器,其通过信号515(或如果省略放大器电路503则通过513)的基频到天线507进行传输。在一个实施例中,匹配网络505可以包括电感器和电容器,其被调谐到基频并被配置为匹配天线507的阻抗(例如,50ω)。偏置电路509被配置为确定输出信号513的脉冲宽度失真(即,非50%占空比),并产生偏置信号519以减小或消除输出信号513的脉冲宽度失真。

51.图6是根据本发明实施例的偏置电路600的简化电路图。参考图6,偏置电路600包括:第一平均电路601,被配置为确定接收信号(例如,图5中所示的输出信号513)的平均电压值并输出平均信号savg;第二平均电路602,被配置为确定接收信号rf数据的平均电压值并输出平均信号davg;差分运算放大器603,用作比较器,以将平均信号savg与平均信号davg进行比较,并输出差分信号vbias。平均信号davg可以用作参考信号vref。在一个实施例中,差分运算放大器603具有用于接收信号savg的正输入端,用于接收信号davg(即vref)的负输入端,以及用于输出差分信号vbias的输出端。将信号vbias提供给驱动级电路501,

用于调整(平衡)输出信号513的沿的上升和下降时间。当savg的信号值大于davg的信号值时(savg》davg),差分信号vbias为正,即下降时间》上升时间;当savg的信号值低于davg的信号值时(savg《davg),vbias为负,即下降时间《上升时间。当savg的信号值等于davg的信号值时(savg=davg),vbias为零,即下降时间=上升时间。

52.图6a是根据本发明实施例的示例性平均电路600a。平均电路600a包括具有负输入端、正输入端和输出端的运算放大器61a,其中所述输出端通过反馈电阻器rf连接到正输入端。输出信号513(或“rf数据”)的相应载波信号子集(cycle1,cycle2,...,cyclen)的电流i1,i2,...,in-1和in耦合到运算放大器的负输入端。这里,cycle1,cycle2,...cyclen是从经调制的载波信号“rf数据”中取得的方波信号的子集。众所周知,具有反馈运算放大器的平均电路600a的输出savg(或davg)是通过根据以下关系将基尔霍夫第一定律应用于运算放大器的输入端而获得的:

53.vavg=-rf(i1+i2+...+in),其中i1,i2,...,in是输出信号(或rf数据)的比特流子集的相应比特的电流。如果载波信号子集是输出信号513的,则vavg是savg。如果载波信号子集是rf数据的,则vavg是davd。

54.图6b是根据本发明实施例的示例性平均电路600b。平均电路600b类似于图6a中的平均电路600a,不同之处在于,在从经调制的载波信号取得的方波信号子集的每个电压和运算放大器61b的输入端之间连接有电阻器。类似于电流平均电路600a,具有反馈运算放大器的电压平均电路600b的输出vavg是通过根据以下关系将基尔霍夫第一定律应用于运算放大器的输入端而获得的:

55.vbias=-rf(v1/r1+v2/r2+...+vn/rn)

56.其中v1,v2,...,vn是输出信号(或rf数据)的载波信号子集的相应方波周期的电压,r1,r2,...,rn是设置在载波信号子集的方波周期和运算放大器的负输入端之间的相应电阻器。在一个实施例中,r1,r2,......和rn具有基本相同的值r,使得平均电路600b的输出电压满足以下关系:

57.vavg=-rf/r(v1+v2+...+vn)。如果载波信号子集是输出信号513的,则vavg是savg。如果载波信号子集是rf数据的,则vavg是davd。

58.图7是根据本发明实施例的具有上升和下降时间调节(平衡)电路的d类放大器700的简化电路图。d类放大器700包括串联连接在vdd和地之间的第一晶体管701和第二晶体管702。放大器700还包括:第一路径,其具有串联连接的第一逆变器703和第二逆变器705,以从rf数据产生第一输出信号735;第二路径,具有串联连接的第三逆变器707和第四逆变器709,以从rf数据产生第二输出信号779。第一输出信号735和第二输出信号779具有相同的频率、相同的相位和相同的幅度。换句话说,第一输出信号735和第二输出信号779基本相同。第一晶体管701具有连接到信号735的栅极,第二晶体管702具有连接到信号779的栅极。例如,信号735和779是图5中所示的射频(rf)信号“rf数据”。注意,这种配置更好地节省功率,因为如果将信号rf数据直接施加到第一晶体管701和第二晶体管702,在这种情况下,第一晶体管701和第二晶体管702必须被设计为相对消耗更多功率的大晶体管。通过具有多个反相级(在该示例中使用两个),rf数据可以到达轨到轨,从而可以减小第一晶体管701和第二晶体管702的尺寸以节省功率。第一晶体管701是pmos晶体管,第二晶体管702是nmos晶体管。放大器700还包括设置在第一晶体管701和输出rfout之间的第一串联晶体管711和设置

在输出rfout和第二晶体管702之间的第二串联晶体管712。第一串联晶体管711和第二串联晶体管712被配置为平衡输出上升和下降时间以减少输出上升和下降时间的不匹配,从而减少二次谐波。

59.在操作中,当差分运算放大器603检测到savg》davg(vref)时,偏置电压vbias为正,即rfout下降时间》rfout上升时间。正vbias增加第二晶体管702的下拉电流驱动并减小第一晶体管701的上拉电流驱动以平衡上升和下降时间的不匹配。相反,当差分运算放大器603检测到savg《davg(vref)时,偏置电压vbias为负,即rfout上升时间》rfout下降时间。负vbias增加第一晶体管701的上拉电流驱动并减小第二晶体管702的下拉电流驱动以平衡上升和下降时间的不匹配。

60.图8是根据本发明另一实施例的功率放大器电路800的简化框图。参考图8,功率放大器电路800包括驱动级电路501、放大器电路503、滤波器505和耦合到滤波器505的输出端的天线507。功率放大器电路800还包括偏置电路809。驱动级电路501被配置为接收数据波形,例如图4中所示的数据流400,并且提供输出信号513。放大器电路503接收信号513并将经放大的输出信号515输出到滤波器505。滤波器505可以是低通滤波器,其通过信号515的基频到达天线507以进行传输。在一个实施例中,偏置电路809是调谐到信号517的二次谐波的串联谐振滤波器。偏置电路809可以包括可调谐电容器821和电感器823,其可以被调谐到信号517的二次谐波。因此,偏置电路809可以向驱动级电路501提供偏置信号vbias 819,以对输出信号513的占空比进行整形,直到二次谐波降低到低于目标电平的电平。

61.图8a是根据本发明实施例的偏置电路809的简化电路图。偏置电路809包括串联rlc电路,其包括电容器c、电感器l和电阻器r。在一个实施例中,rlc电路被调谐到二次谐波的谐振频率。在此串联配置中,xc和xl相互抵消。因此,流过串联谐振电路的电流处于最大值。通过差分运算放大器81将电阻器r处的压降与阈值电压vthreshold进行比较,如果电阻器r处的压降超过阈值电压值,则差分运算放大器81产生偏置电压vbias 819。

62.图9是示出根据本发明示例性实施例的操作d类放大器的方法的简化流程图。参考图9,d类放大器在其驱动电路处接收rf输入信号(901)。接下来,在903处,驱动电路产生输出信号,该输出信号可具有可导致谐波失真的非对称上升和下降时间。接下来,在905处,由d类放大器的第一平均电路确定接收的rf输入信号的平均电压值。在907处,由d类放大器的第二平均电路确定所生成的输出信号的平均电压值,以产生偏置电压信号。接下来,在909处,将偏置电压信号提供给驱动电路。在911,驱动电路平衡输出信号的沿的上升和下降时间,以调整输出信号的占空比。应该理解,上述框可以以不同的顺序执行。例如,第一平均电压值和第二平均电压值可以同时或以不同的顺序确定。换句话说,框905和907可以同时执行或以不同顺序执行。

63.因此,本公开的实施例已经描述了d类放大器及其操作方法的细节。为了避免模糊代表性实施例的描述,本文未提供本领域中已知的许多细节。

64.应理解,上述实施例旨在是说明性的而非限制性的。在阅读以上描述后,许多实施例对于本领域技术人员将是显而易见的。因此,本发明的范围不应参考以上描述来确定,而是应参考所附权利要求及其等同物的全部范围来确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1