半导体结构的形成方法以及SRAM存储器的形成方法与流程

本发明涉及半导体,具体涉及一种半导体结构的形成方法以及sram存储器的形成方法。

背景技术:

1、随着半导体技术的发展,半导体器件的尺寸持续减小,半导体器件制造过程中的光刻工艺精度也不断提升。

2、目前行业广泛使用的193nm浸没式光刻技术可以将特征尺寸缩小至76nm。在此基础上,再搭配多重曝光刻蚀技术(litho-etch-litho-etch,简称lele),可以继续将特征尺寸缩小至38纳米。

3、但随着集成电路制造工艺持续微缩,尤其是进入5纳米制程后,基于传统193nm浸没式光刻技术的制备工艺局限性越来越明显。目前,有部分集成电路制造工艺采用了更为先进的技术缩小制程,例如,极紫外(extreme ultra-violet,简称euv)光刻技术,然而,这些先进技术的产业化存在较高的技术障碍,目前仍难以大规模应用到量产实践中。

4、目前,在集成电路器件的后段互连工艺的制备中,仍更多地采用193nm浸没式光刻技术。对于该技术而言,虽然可以通过搭配双重自对准图案定义(sadp)以及四重自对准图案定义(saqp)等工艺,继续缩小半导体结构的特征尺寸,但这些技术更多适用于形成周期性的规整图案。在一些对图案灵活性要求较高的器件制备,例如,sram存储器中,就无法同时兼顾半导体结构的小尺寸以及图案灵活性的需求,从而使工艺适用范围较小,工艺兼容性较差。

技术实现思路

1、本发明解决的技术问题是,提供一种半导体结构的形成方法以及sram存储器的形成方法,在保证了半导体结构的小尺寸的需求的同时,兼顾了结构图案的灵活性,从而扩大了形成工艺的适用范围,提升了工艺兼容性。

2、为解决上述技术问题,本发明的技术方案提供一种半导体结构的形成方法,包括:提供衬底;在所述衬底上形成第一图形材料层;在所述第一图形材料层上形成第一侧墙;在所述第一图形材料层上形成牺牲结构,所述牺牲结构的尺寸大于第一侧墙的尺寸;以所述牺牲结构和第一侧墙为掩膜,对第一图形材料层注入掺杂离子,在所述第一图形材料层内形成第一掺杂区和第二掺杂区,所述第一掺杂区位于所述第一侧墙底部,所述第二掺杂区位于所述牺牲结构底部,且第一掺杂区内的掺杂离子浓度大于第二掺杂区内的掺杂离子浓度;以所述牺牲结构和第一侧墙为掩膜,刻蚀所述第一图形材料层,使所述第一掺杂区形成第一芯轴结构,使所述第二掺杂区形成第二芯轴结构;形成位于所述第一芯轴结构侧壁的第二侧墙、以及位于第二芯轴结构侧壁的第三侧墙;在形成第二侧墙和第三侧墙之后,去除所述第二芯轴结构。

3、可选的,所述第一图形材料层的材料包括无定形硅。

4、可选的,所述第一侧墙的形成方法包括:形成位于所述第一图形材料层上的初始芯轴结构;在所述初始芯轴结构侧壁以及顶部表面沉积初始第一侧墙材料层;回刻蚀所述初始第一侧墙材料层,直至暴露出初始芯轴结构的顶部表面;去除所述初始芯轴结构。

5、可选的,所述第一侧墙的尺寸范围为10纳米~20纳米;所述牺牲结构的尺寸范围为30纳米~50纳米。

6、可选的,对第一图形材料层注入掺杂离子的工艺参数包括:所述掺杂离子包括硼离子;所述掺杂离子注入的能量为8kev~20kev。

7、可选的,所述第一掺杂区的离子浓度为1015cm-3~1020cm-3;所述第二掺杂区的离子浓度为0~105cm-3。

8、可选的,在对第一图形材料层注入掺杂离子后,在刻蚀所述第一图形材料层之前,所述半导体结构的形成方法还包括:对所述牺牲结构的厚度进行减薄处理。

9、可选的,对所述牺牲结构的厚度进行减薄处理后,所述牺牲结构的尺寸与所述第一侧墙的尺寸相同。

10、可选的,所述第二侧墙与第三侧墙同时形成;所述第二侧墙的形成工艺包括原子层沉积工艺;所述第三侧墙的形成工艺包括原子层沉积工艺。

11、可选的,去除所述第二芯轴结构的工艺包括湿法刻蚀工艺。

12、可选的,在形成所述第一图形材料层之前,半导体结构的形成方法还包括:形成位于衬底上的初始第一介质层。

13、可选的,去除所述第二芯轴结构后,所述第一芯轴结构、第二侧墙构成第一图形结构,所述第一图形结构的尺寸大于所述第三侧墙的尺寸。

14、可选的,去除所述第二芯轴结构后,还包括:以所述第一芯轴结构、第二侧墙、以及第三侧墙为掩膜,刻蚀所述初始第一介质层,以形成位于所述第一芯轴结构和第二侧墙底部的第一隔离结构、以及位于第三侧墙底部的第二隔离结构,第一隔离结构以及第二隔离结构之间存在若干隔离间隙。

15、可选的,在形成第一隔离结构以及第二隔离结构后,半导体结构的形成方法还包括:去除所述第一芯轴结构、第二侧墙、以及第三侧墙。

16、可选的,所述半导体结构的形成方法还包括:在各隔离间隙内形成若干电互连结构,各电互连结构的尺寸相同或不同。

17、可选的,所述电互连结构的尺寸范围为10纳米~35纳米。

18、可选的,所述第一芯轴结构、第二侧墙构成第一图形结构;所述第一图形结构的尺寸范围为35纳米~50纳米。

19、可选的,所述牺牲结构的材料包括:光刻胶、无定形硅或无定形碳。

20、可选的,所述第一侧墙的材料包括氮化硅或氧化钛;所述第二侧墙的材料包括氮化硅或氧化钛;所述第三侧墙的材料包括氮化硅或氧化钛。

21、可选的,所述第二侧墙的尺寸范围为10纳米~20纳米;所述第三侧墙的尺寸范围为10纳米~20纳米。

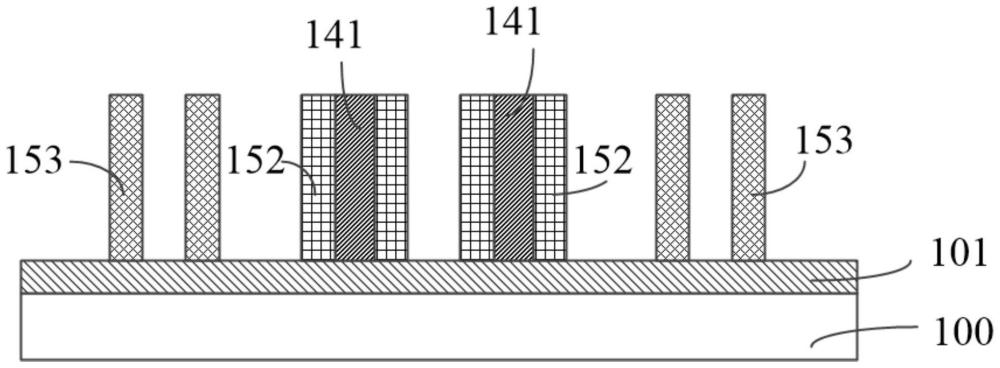

22、相应的,本发明的技术方案还提供一种sram存储器的形成方法,包括:提供衬底;在所述衬底上形成初始第一介质层、以及位于初始第一介质层上的第一图形材料层;在所述第一图形材料层上形成第一侧墙;在所述第一图形材料层上形成牺牲结构,所述牺牲结构的尺寸大于第一侧墙的尺寸;以所述牺牲结构和第一侧墙为掩膜,对第一图形材料层注入掺杂离子,在所述第一图形材料层内形成第一掺杂区和第二掺杂区,所述第一掺杂区位于所述第一侧墙底部,所述第二掺杂区位于所述牺牲结构底部,且第一掺杂区内的掺杂离子浓度大于第二掺杂区内的掺杂离子浓度;以所述牺牲结构和第一侧墙为掩膜,刻蚀所述第一图形材料层,使所述第一掺杂区形成第一芯轴结构,使所述第二掺杂区形成第二芯轴结构;形成位于所述第一芯轴结构侧壁的第二侧墙、以及位于第二芯轴结构侧壁的第三侧墙;在形成第二侧墙和第三侧墙之后,去除所述第二芯轴结构;以所述第一芯轴结构、第二侧墙、以及第三侧墙为掩膜,刻蚀所述初始第一介质层,以形成位于所述第一芯轴结构和第二侧墙底部的第一隔离结构、以及位于第三侧墙底部的第二隔离结构,第一隔离结构以及第二隔离结构之间存在若干隔离间隙;在各隔离间隙内形成若干电互连结构。

23、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

24、本发明的技术方案提供的半导体结构的形成方法中,在第一图形材料层形成第一侧墙后,还在第一图形材料层上形成了尺寸大于所述第一侧墙的牺牲结构,在对第一图形材料层注入掺杂离子的过程中,由于所述牺牲结构的尺寸较大,其作为掩膜,能够减少注入进牺牲结构下的第一图形材料层内的掺杂离子,而第一侧墙由于尺寸较小,对注入第一图形材料层内的掺杂离子的阻挡作用有限,因此,在注入掺杂离子后,位于第一侧墙底部的第一掺杂区内的掺杂离子浓度大于位于牺牲结构底部的第二掺杂区内的掺杂离子浓度,从而使刻蚀所述第一图形材料层后形成的第一芯轴结构内的离子浓度大于第二芯轴结构内的离子浓度,使第一芯轴结构的材料与第二芯轴结构的材料有差异,进而,可以在后续通过选择性的去除第二芯轴结构,保留第一芯轴结构,有利于在衬底上形成不同尺寸的图案,增加了图案的灵活性,提升了工艺的兼容性。

25、进一步,所述半导体结构的形成方法中,形成第一侧墙、第二侧墙的过程实现了两次自对准图案形成工艺,即,所述第二侧墙是通过四重自对准图案形成工艺形成,而所述第三侧墙的形成过程仅实现了一次自对准图案形成工艺,即,所述第三侧墙通过双重自对准图案形成工艺形成,因此,所述半导体结构的形成方法同时结合了双重自对准图案形成工艺和四重自对准图案形成工艺,在保证小尺寸结构的基础上,进一步提升了图案尺寸的灵活性。

26、本发明的技术方案提供的sram存储器的形成方法中,由于所述第一隔离结构是以第一芯轴结构、第二侧墙为掩膜刻蚀形成,所述第二隔离结构是以第三侧墙为掩膜刻蚀形成,因此,使所述第一隔离结构、第二隔离结构、以及形成于各隔离间隙内的电互连结构的尺寸灵活性均较高。

- 还没有人留言评论。精彩留言会获得点赞!