一种集成门极米勒钳位功能的IGBT芯片及其制备方法与流程

一种集成门极米勒钳位功能的igbt芯片及其制备方法

技术领域

1.本发明涉及igbt芯片制备技术领域,具体涉及一种集成门极米勒钳位功能的igbt芯片及其制备方法。

背景技术:

2.igbt是一种大功率半导体分立器件,结合了mos器件高开关频率,易于控制和bjt器件的大电流处理能力能等优点,在工业变频、消费电子、轨道交通、新能源、航天航空等领域有着广泛的应用。igbt芯片本身是一种高速开关,在器件的开关过程中,集电极电压vce的快速变化,会产生很高的dv/dt,从而通过门极与集电极之间的米勒寄生电容cgc产生灌入门极的分布电流,称为米勒效应。

3.igbt的门极驱动回路和集电极功率回路原本是隔离的,但是当米勒效应产生的分布电流过大时,会严重干扰到门极驱动回路的正常工作,例如可能使得门极电压抬高,原本处于关断状态的igbt发生误开通,从而增加了同一桥臂中上下管直通的风险,同时也增大了器件损耗。

4.传统的方法是在栅极驱动回路中增加栅极电压钳位功能的米勒钳位模块,这样会增加栅极驱动设计的复杂性,不利于降低应用成本和器件的推广。

技术实现要素:

5.有鉴于此,有必要提供一种集成门极米勒钳位功能的igbt芯片及其制备方法,有效降低了igbt芯片在工作过程中的门极误开通风险,可以在实现门极米勒钳位功能的同时,简化门极驱动电路。

6.为了实现上述目的,本发明提供了一种集成门极米勒钳位功能的igbt芯片,包括:igbt器件和门极米勒钳位模块,所述igbt器件包括元胞区和终端区,所述门极米勒钳位模块位于igbt芯片的培区内,且所述门极米勒钳位模块包括一个晶体管t、一个二极管d、电阻rb和电阻re,其中:所述二极管d的阴极与晶体管t的源极以及igbt器件的门极相连,所述晶体管t的漏极与igbt器件的源极相连;所述电阻rb的一端与晶体管t的门极相连,另一端与二极管d的阳极和外驱动电路的外电阻相连;电阻re的一端与外驱动电路的参考地相连,另一端与电阻rb相连。

7.优选的,所述igbt器件为半桥模块,包括上管和下管,其中,上管包括igbt管t1和二极管d1,下管包括igbt管t2和二极管d2。

8.为了实现上述目的,本发明还提供了上述集成门极米勒钳位功能的igbt芯片的制备方法,包括如下步骤:s1、场氧化层生长与终端区场限环区域选择性腐蚀场氧化层,元胞区jfet区n型离子注入;s2、栅氧化层生长与多晶硅电极形成;

s3、p阱区掺杂以及杂质推进;s4、n型源区掺杂;s5、隔离介质层淀积与接触孔刻蚀;s6、正面金属化与钝化层形成;s7、晶圆背面减薄与金属化。

9.优选的,所述步骤s1,具体包括:选择n型单晶硅衬底,采用湿氧工艺进行场氧化层生长;终端区场限环区域选择性腐蚀场氧化层,b+离子注入,去胶后杂质推进;元胞区、晶体管区和二极管区选择性腐蚀场氧化层,元胞区jfet区n型离子注入,去胶后杂质推进,形成n型掺杂区。

10.优选的,所述步骤s2,具体包括:对氧化层进行湿法腐蚀,去除晶圆表面的氧化层,晶圆清洗,栅氧生长;基于lpcvd淀积多晶硅,刻蚀多晶硅,形成元胞区栅电极,晶体管区栅电极和终端区busbar走线。

11.优选的,所述步骤s3,具体包括:晶圆翻转,去除背面多晶硅,晶圆翻转,清洗;元胞区p阱区p型离子注入,去胶后杂质推进,形成p型掺杂区。

12.优选的,所述步骤s4,具体包括:元胞区和二极管区分别进行n型离子注入,去胶后杂质推进。

13.优选的,所述步骤s5,具体包括:进行隔离介质层淀积,形成usg+bpsg双层结构,并刻蚀接触孔;接触孔区域注入:第一次注入bf2离子,第二次注入b+离子,去胶后炉管退火。

14.优选的,所述步骤s6,具体包括:正面淀积金属层,干法刻蚀图形化,利用pi胶coating形成钝化层,并进行光刻图形化。

15.优选的,所述步骤s7,具体包括:晶圆背面研磨,去除氧化硅,厚度减薄,背面注入p+离子形成缓冲层;背面阳极注入b+离子,炉管退火激活杂质,背面淀积金属层。

16.采用上述实施例的有益效果是:本发明通过在原有的igbt芯片中增加了门极米勒钳位模块,其包括有一个晶体管t、一个二极管d、电阻rb和电阻re,通过这些器件与原先的igbt器件的门极相连接,并与外驱动电路相连接,当igbt器件需要关闭时,其内部的门极米勒钳位模块能够提供一个到外驱动电路参考地的低阻抗回路,能够抑制其集电极电位抬升产生的米勒电容位移电流对门极电位的干扰作用,从而增强了门极电位的抗干扰能力。

附图说明

17.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附

图。

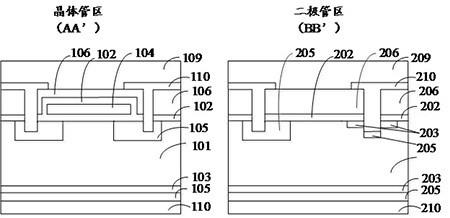

18.图1为本发明提供的集成门极米勒钳位功能的igbt芯片一实施例的电路原理示意图;图2为本发明提供的集成门极米勒钳位功能的igbt芯片一实施例的平面示意图;图3为本发明提供的集成门极米勒钳位功能的igbt芯片中晶体管区和二极管区一个实施例的结构示意图;图4-图10为本发明提供的集成门极米勒钳位功能的igbt芯片的制备方法中执行步骤s1-s7时igbt芯片的结构变化示意图。

具体实施方式

19.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

20.为了便于附图说明中标记的清晰,考虑到晶体管区、二极管区和元胞区中在igbt芯片制备时存在诸多具有相同功能的结构,现对说明书附图中的部分标记进行统一说明,具体见下表1。

21.表1:部分附图标记对应表

本发明提供了一种集成门极米勒钳位功能的igbt芯片及其制备方法,本发明通过在原有的igbt芯片中增加了门极米勒钳位模块,有效降低了igbt芯片在工作过程中的门极误开通风险,可以在实现门极米勒钳位功能的同时,简化门极驱动电路,现就具体实施例说明如下。

22.参阅图1,图1为本发明提供的集成门极米勒钳位功能的igbt芯片一实施例的电路原理示意图。

23.在本发明的实施例中,该集成门极米勒钳位功能的igbt芯片,包括:igbt器件10和门极米勒钳位模块20,igbt器件10包括元胞区和终端区,所述门极米勒钳位模块20位于位于igbt芯片的培区内,所述门极米勒钳位模块20包括一个晶体管t、一个二极管d、电阻rb和电阻re,其中:所述二极管d的阴极与晶体管t的源极以及igbt器件的门极相连,所述晶体管t的漏极与igbt器件的源极相连,且连接方式为开尔文连接,不与功率端子共用回路;所述电阻rb的一端与晶体管t的门极相连,另一端与二极管d的阳极和外驱动电路的外电阻r

gon/off

相连;电阻re的一端与外驱动电路的参考地相连,另一端与电阻rb相连。

24.具体的,当igbt管(如t2)需要关闭时,米勒钳位模块提供了一个到驱动电路参考地的低阻抗回路,从而增强了门极电位的抗干扰能力。

25.在优选的实施例中,所述igbt器件为半桥模块,包括上管和下管,其中,上管包括igbt管t1和二极管d1,下管包括igbt管t2和二极管d2。

26.本发明通过在原有的igbt芯片中增加了门极米勒钳位模块,其包括有一个晶体管t、一个二极管d、电阻rb和电阻re,通过这些器件与原先的igbt器件的门极相连接,并与外驱动电路相连接,当igbt器件的下管需要关闭时,其内部的门极米勒钳位模块能够提供一个到外驱动电路参考地的低阻抗回路,能够抑制其集电极电位抬升产生的米勒电容位移电流对门极电位的干扰作用,从而增强了门极电位的抗干扰能力。

27.为了进一步说明将igbt芯片进行半导体制备的情况,请参阅图2,图2为本发明提供的集成门极米勒钳位功能的igbt芯片一实施例的平面示意图。

28.在本实施例中,门极米勒钳位模块位于igbt芯片的陪区,与igbt芯片元胞区和终端区在电学上是隔离的,不会造成相互之间的串扰,其俯视图如图2所示。晶体管t为一个多晶硅栅的p沟道mosfet,左侧的漏极与igbt芯片的源极相连,右侧的源极与二极管d的阴极相连,多晶硅栅极与电阻rb相连,其沿aa’切线的横截面如米勒钳位区横截面图(虚线)所示。二极管d为一个pn结二极管,下方的阴极与晶体管t的源极相连,上方的阳极与电阻rb以及igbt芯片的门极相连,其沿bb’切线的横截面如米勒钳位区横截面图(虚线)所示。电阻rb和re均为多晶硅电阻,电阻rb分别与晶体管t的栅极和二极管d的阳极相连,电阻re分别与电阻rb和晶体管t的漏极相连。图中深色部分为金属走线(图中已标识),左侧上方的金属条与外驱动电路相连。

29.在本发明的一些实施例中,当本发明的集成门极米勒钳位功能的igbt芯片被制备完成之后,其具体附图如图3所述,图3为本发明提供的集成门极米勒钳位功能的igbt芯片中晶体管区和二极管区一个实施例的结构示意图。

30.在本实施例中,晶体管区为沿aa’切线的横截面,二极管区为沿bb’切线的横截面。

31.为了进一步描述本发明提供的集成门极米勒钳位功能的igbt芯片的制备方法,请具体参阅图4-图10,图4-图10为本发明提供的集成门极米勒钳位功能的igbt芯片的制备方法中执行步骤s1-s7时igbt芯片的结构变化示意图。

32.在本实施例中,该集成门极米勒钳位功能的igbt芯片的制备方法,包括如下步骤:s1、场氧化层生长与终端区场限环区域选择性腐蚀场氧化层,元胞区jfet区n型离子注入;s2、栅氧化层生长与多晶硅电极形成;s3、p阱区掺杂以及杂质推进;s4、n型源区掺杂;s5、隔离介质层淀积与接触孔刻蚀;s6、正面金属化与钝化层形成;s7、晶圆背面减薄与金属化。

33.作为优选的实施例,请请查阅图4,所述步骤s1,具体包括:选择n型单晶硅衬底101/201/301,采用湿氧工艺进行场氧化层102/202/302生长;终端区场限环区域选择性腐蚀场氧化层,b+离子注入(即p型掺杂离子),去胶后杂质推进;元胞区、晶体管区和二极管区选择性腐蚀场氧化层,元胞区jfet区中n型离子注

入,去胶后杂质推进,形成n型掺杂区303。

34.具体的,选择fz单晶硅衬底,晶圆表面为(100)晶面,电阻率为30-90ω

·

cm;湿氧工艺的温度为800-1050℃,氧化层厚度为1-3μm;b+离子注入的剂量为8e13-5e14,注入能量为80-140kev,且去胶后杂质推进的温度为1000-1200℃,时间为300-600min;注入p+离子(即n型离子)的注入剂量为5e11-2e13,注入能量为40-120kev,且去胶后杂质推进的温度为1000-1150℃,时间为150-300min。

35.作为优选的实施例,请请查阅图5,所述步骤s2,具体包括:对氧化层进行湿法腐蚀,去除晶圆表面的氧化层,晶圆清洗,栅氧生长,厚度为1000-1200a;基于lpcvd淀积多晶硅形成多晶硅栅区104/204,厚度为8000-12000a,刻蚀多晶硅,形成元胞区栅电极(即多晶硅栅区304),晶体管区栅电极和终端区busbar走线。

36.作为优选的实施例,请请查阅图6,所述步骤s3,具体包括:晶圆翻转,去除背面多晶硅,晶圆翻转,清洗;元胞区p阱区p型离子注入,去胶后杂质推进,形成p型掺杂区105/205/305。

37.具体的,p型离子注入的注入剂量为1e13-1e14,注入能量为80-140kev,去胶后杂质推进的温度为1000-1150℃,时间为90-150min。

38.作为优选的实施例,请请查阅图7,所述步骤s4,具体包括:元胞区和二极管区分别进行n型离子注入,去胶后杂质推进,得到n型掺杂区203/303。

39.具体的,n型离子为as+离子,且注入剂量为1e15-8e15,注入能量为80-150kev,去胶后杂质推进的温度为850-1000℃,时间为150-250min。

40.作为优选的实施例,请请查阅图8,所述步骤s5,具体包括:进行隔离介质层淀积,形成usg+bpsg双层结构(即隔离介质层106/206/306),总厚度9000-12000a,并刻蚀接触孔107/207/307,下层si过刻蚀深度为0.2-0.5μm;接触孔107/207/307区域注入:第一次注入bf2离子,注入剂量为5e14-8e15,注入能量为20-80kev,第二次注入b+离子,注入剂量为1e14-5e15,注入能量为40-100kev,去胶后炉管退火,温度为700-1000℃,时间为30-60min。

41.作为优选的实施例,请请查阅图9,所述步骤s6,具体包括:正面淀积金属层108/208/308,厚度4-8μm,干法刻蚀图形化,利用pi胶coating形成钝化层109/209/309,并进行光刻图形化,厚度8-12μm。

42.作为优选的实施例,请请查阅图10,所述步骤s7,具体包括:晶圆背面研磨,去除氧化硅,厚度减薄至60-150μm,背面注入p+离子形成缓冲层,注入剂量为2e11-1e13,注入能量为200-900kev;背面阳极注入b+离子,注入剂量为1e12-8e13,注入能量为20-50kev,炉管退火激活杂质,温度为300-500℃,时间为20-80min,背面淀积金属层110/210/310,厚度1-2μm。

43.经过上述步骤s1-s7的制备工艺就能够制备出本发明的集成门极米勒钳位功能的igbt芯片。

44.综上所述,本发明提供的集成门极米勒钳位功能的igbt芯片及其制备方法通过在原有的igbt芯片中增加了门极米勒钳位模块,其包括有一个晶体管t、一个二极管d、电阻rb

和电阻re,通过这些器件与原先的igbt器件的门极相连接,并与外驱动电路相连接,当igbt芯片内igbt器件需要关闭时,门极米勒钳位模块能够提供一个到外驱动电路参考地的低阻抗回路,从而增强了门极电位的抗干扰能力。

45.以上对本发明所提供的集成门极米勒钳位功能的igbt芯片及其制备方法进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1