一种半导体结构的制造方法及半导体结构与流程

本公开涉及半导体,尤其涉及一种半导体结构的制造方法及半导体结构。

背景技术:

1、动态随机存取存储器(dram)是电子设备中常用的半导体结构,其包含多个存储单元,每个存储单元包含晶体管和电容器。随着dram特征尺寸不断微缩,通常通过增加电容柱的高度来增加电容器的电容,以提升存储密度。在特征尺寸减小至一定数值以下时,形成高深宽比的电容柱会面临因薄膜应力增加等导致的电容柱不稳定等问题,因此如何形成稳定可靠的柱状电容结构成为目前亟待解决的技术问题。

技术实现思路

1、有鉴于此,本公开实施例为解决背景技术中存在的技术问题而提供一种半导体结构的制造方法及半导体结构。

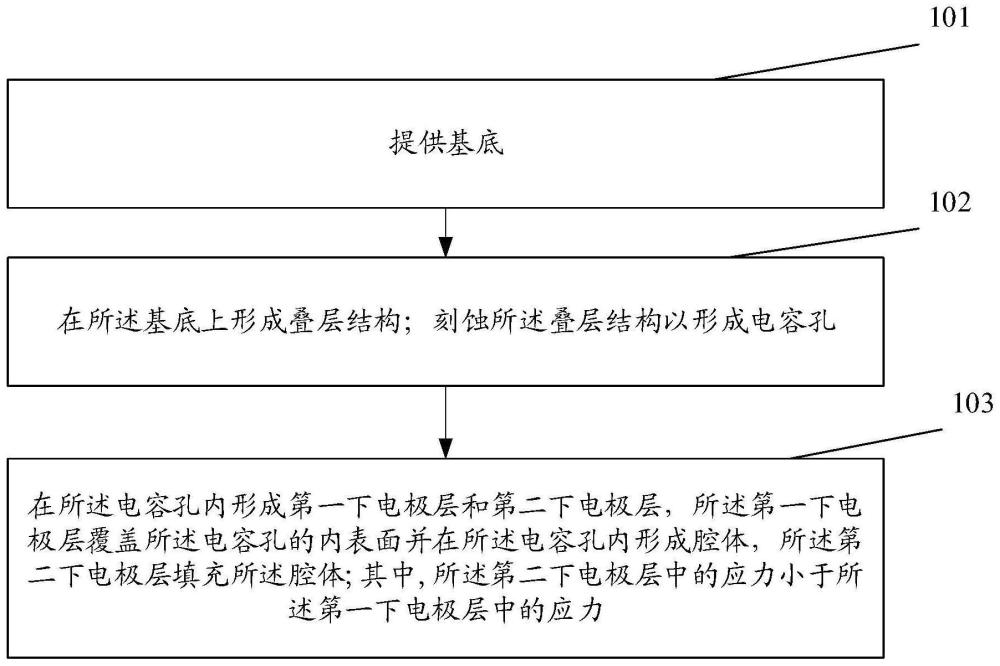

2、根据本公开实施例的第一方面,提供了一种半导体结构的制造方法,包括:

3、提供基底;

4、在所述基底上形成叠层结构;

5、刻蚀所述叠层结构以形成电容孔;

6、在所述电容孔内形成第一下电极层和第二下电极层,所述第一下电极层覆盖所述电容孔的内表面并在所述电容孔内形成腔体,所述第二下电极层填充所述腔体;其中,

7、所述第二下电极层中的应力小于所述第一下电极层中的应力。

8、在一些实施例中,所述第二下电极层的材料包括含硅的结晶材料。

9、在一些实施例中,所述含硅的结晶材料的晶粒尺寸小于1nm。

10、在一些实施例中,所述第一下电极层与所述第二下电极层共同定义为下电极,所述下电极的直径不大于40nm。

11、在一些实施例中,所述第一下电极层沿所述电容孔的径向方向的厚度为10-15nm,所述第二下电极层沿所述电容孔的径向方向的厚度为15-30nm。

12、在一些实施例中,在所述基底上形成叠层结构,以及刻蚀所述叠层结构以形成所述电容孔,包括:

13、形成所述叠层结构于所述基底上,所述叠层结构至少包括第一支撑层、第一牺牲层、第二支撑层、第二牺牲层以及第三支撑层;

14、沿垂直于所述基底的方向刻蚀所述叠层结构,暴露出所述基底,形成所述电容孔。

15、在一些实施例中,在所述电容孔内形成第一下电极层和第二下电极层,所述第一下电极层覆盖所述电容孔的内表面并在所述电容孔内形成腔体,所述第二下电极层填充所述腔体,包括:

16、形成第一下电极材料层,所述第一下电极材料层覆盖所述电容孔的内表面以及所述叠层结构的上表面,所述第一下电极材料层在所述电容孔内形成腔体;

17、形成第二下电极材料层,所述第二下电极材料层填充所述腔体并覆盖所述第一下电极材料层的顶部;

18、刻蚀所述第二下电极材料层及所述第一下电极材料层的顶部,暴露出所述第三支撑层,剩余的所述第一下电极材料层与所述第二下电极材料层分别定义为所述第一下电极层和所述第二下电极层。

19、在一些实施例中:刻蚀所述第二下电极层及所述第一下电极层的顶部,暴露出所述第三支撑层后,所述方法还包括:

20、在所述第一下电极层、所述第二下电极层及所述第三支撑层上方形成掩膜层和位于所述掩膜层上的图形化的光刻胶层;所述掩膜层包括第一掩膜层、第二掩膜层及第三掩膜层,其中,所述第一掩模层的材料与所述第三支撑层的材料相同。

21、在一些实施例中,形成所述掩膜层和位于所述掩膜层上的所述图形化的光刻胶层后,所述方法还包括:

22、基于所述图形化的光刻胶层,刻蚀所述掩膜层,将光刻胶层图案转移至所述第一掩膜层,形成第一开口,所述第一开口暴露至少一个所述第一下电极层的部分区域和部分所述第三支撑层;

23、以所述第一掩模层为掩膜刻蚀所述第三支撑层,形成第二开口,所述第二开口暴露所述第二牺牲层;

24、去除所述第二牺牲层,暴露所述第二支撑层;

25、刻蚀所述第二支撑层,形成第三开口,所述第三开口暴露所述第一牺牲层;

26、去除所述第一牺牲层,暴露所述第一支撑层,剩余的所述第一支撑层、所述第二支撑层及所述第三支撑层定义为支撑结构。

27、在一些实施例中,在所述电容孔内形成第一下电极层和第二下电极层,所述第一下电极层覆盖所述电容孔的内表面并在所述电容孔内形成腔体,所述第二下电极层填充所述腔体,包括:

28、形成第一下电极材料层,所述第一下电极材料层覆盖所述电容孔的内表面以及所述叠层结构的上表面,所述第一下电极材料层在所述电容孔内形成腔体;

29、去除所述第一下电极材料层的顶部,暴露出所述第三支撑层,剩余的所述第一下电极材料层定义为第一下电极层,所述第一下电极层在所述电容孔内形成腔体;

30、形成所述第二下电极材料层,所述第二下电极材料层填充所述腔体并覆盖所述第一下电极层和所述第三支撑层的顶部。

31、在一些实施例中,形成所述第二下电极材料层后,所述方法还包括:

32、在所述第二下电极材料层上方形成掩膜层和位于所述掩膜层上的图形化的光刻胶层;所述掩膜层包括第二掩膜层与第三掩膜层,所述第二下电极材料层的顶部充当部分掩膜层使用。

33、在一些实施例中,形成所述掩膜层和位于所述掩膜层上的所述图形化的光刻胶层后,所述方法还包括:

34、基于所述图形化的光刻胶层,刻蚀所述第三掩膜层、所述第二掩膜层以及所述第二下电极材料层的顶部,将光刻胶层图案转移至所述第二下电极材料层,形成第一开口,所述第一开口暴露至少一个所述第一下电极层的部分区域和部分所述第三支撑层;

35、以图案化之后的所述第二下电极材料层为掩膜刻蚀所述第三支撑层,形成第二开口,所述第二开口暴露所述第二牺牲层;

36、去除所述第二牺牲层,暴露所述第二支撑层;

37、刻蚀所述第二支撑层,形成第三开口,并去除覆盖所述第三支撑层和所述第一下电极层顶部的所述第二下电极材料层,所述第三开口暴露所述第一牺牲层,剩余的所述第二下电极材料层定义为所述第二下电极层;

38、去除所述第一牺牲层,暴露所述第一支撑层,剩余的所述第一支撑层、所述第二支撑层及所述第三支撑层定义为支撑结构。

39、在一些实施例中,形成所述第二下电极材料层,包括:

40、在温度范围为470-530℃的温度下形成所述第二下电极材料层。

41、在一些实施例中,在去除所述第一牺牲层,暴露所述第一支撑层之后,所述方法还包括:

42、在所述第一下电极层与第二下电极层以及第一支撑层与第三支撑层暴露的表面上形成介电层;

43、在所述介电层的表面上形成上电极。根据本公开实施例的第二方面,提供了一种半导体结构,包括:

44、基底;

45、位于所述基底上方的支撑结构,所述支撑结构中包括贯穿所述支撑结构的电容孔;

46、位于所述电容孔内的下电极,其中,所述下电极包括第一下电极层和第二下电极层,所述第一下电极层覆盖所述电容孔的底部和侧壁,并构成腔体,所述第二下电极层填充于所述腔体;其中,所述第二下电极层中的应力小于所述第一下电极层中的应力。

47、在一些实施例中,所述第二下电极层的材料包括含硅的结晶材料。

48、在一些实施例中,所述含硅的结晶材料的晶粒尺寸小于1nm。

49、在一些实施例中,所述下电极的直径不大于40nm。

50、在一些实施例中,所述第一下电极层沿所述电容孔的径向方向的厚度为10-15nm,所述第二下电极层沿所述电容孔的径向方向的厚度为15-30nm。

51、在一些实施例中,所述半导体结构还包括:

52、覆盖所述下电极及所述支撑结构的介电层和覆盖所述介电层的上电极。

53、本公开实施例提供了一种半导体结构的制造方法,包括:提供基底;在所述基底上形成叠层结构;刻蚀所述叠层结构以形成电容孔;在所述电容孔内形成第一下电极层和第二下电极层,所述第一下电极层覆盖所述电容孔的内表面并在所述电容孔内形成腔体,所述第二下电极层填充所述腔体;其中,所述第二下电极层中的应力小于所述第一下电极层中的应力。本公开首先在位于基底上的叠层结构中形成电容孔,然后在电容孔内形成第一下电极层和第二下电极层,第一下电极层覆盖电容孔的内表面并在电容孔内形成腔体,第二下电极层填充腔体,第一下电极层与第二下电极层共同构成下电极。其中,由于第二下电极层填充了第一下电极层的腔体,且第二下电极层中的应力小于第一下电极层中的应力,因此能够改善单一第一下电极的应力过大导致电容柱易倾斜的情况,本公开实施例可以消除薄膜应力,第二下电极层可以对第一下电极层起到稳定、良好的支撑作用,使得工艺过程中电容柱的稳定性得以增强,不易发生倾斜。进而能够改善因电容柱倾斜导致的刻蚀开口偏斜时,所造成的支撑层无法正常打开,以至于无法充分去除底部氧化层,使得无法给上电极预留充分空间,从而导致整个电容失效的问题。

54、本公开附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本公开的实践了解到。

- 还没有人留言评论。精彩留言会获得点赞!