一种PCB过孔结构及优化PCB过孔阻抗波动的方法与流程

一种pcb过孔结构及优化pcb过孔阻抗波动的方法

技术领域

1.本公开涉及通信技术领域,尤其涉及一种pcb过孔结构及优化pcb过孔阻抗波动的方法。

背景技术:

2.印制电路板(printed circuit board,pcb)是通信设备内重要的部件,是电子元器件的支撑体和电气连接的提供者。随着pcb承载通信的电子信号速率越来越高,需要对pcb上的电子线路的阻抗进行优化以保证电子信号质量。多层pcb的高速信号传输通常采用换层设计,pcb上不同层的走线借由过孔连接成为彼此连通的通信网络。过孔作为pcb通信网络的重要组成部分,本身具有和走线一样的分布阻抗特性。随着pcb通信速率进入ghz时代,过孔处的阻抗的稳定性日益成为保证pcb通信信号质量的关键技术。

技术实现要素:

3.有鉴于此,本公开的实施例提供了一种pcb过孔结构及优化pcb过孔阻抗波动的方法、、电子装置、计算设备、计算机程序产品以及计算机可读存储介质,可以减小过孔处阻抗的波动,将过孔的阻抗值降低至目标值附近,改善印制电路板的信号质量。

4.根据本公开的一方面,提供了一种印制电路板过孔结构,所述印制电路板包括多个层和走线,所述印制电路板过孔结构包括:过孔,贯穿印制电路板的多个层并且包括第一类焊盘和第二类焊盘。所述第一类焊盘与所述走线位于同一层并且连接所述走线与所述过孔,并且,所述第二类焊盘与所述走线不连接且位于所述印制电路板的选定层中以减小所述过孔的阻抗波动,所述选定层为所述多个层中的除表层和所述第一类焊盘所在层之外的其余层中的部分层或全部层。

5.在一些实施例中,所述过孔还包括表层焊盘,所述过孔经由所述表层焊盘与器件连接,并且所述过孔包括第一区段,所述第一区段具有长度h并且其始端与所述表层焊盘连接,所述第一区段跨越所述多个层中的若干层,并且所述第二类焊盘未设置在所述若干层中。

6.在一些实施例中,所述器件包括焊球和电容中的至少一种。

7.在一些实施例中,所述长度h约为15mil。

8.在一些实施例中,所述过孔还包括位于所述第一区段的末端与所述第一类焊盘之间且长度为h1的第二区段。

9.在一些实施例中,所述印制电路板还包括围绕所述过孔并与所述过孔绝缘的至少两个反焊盘,所述至少两个反焊盘中的每一个位于所述多个层中的除所述第一类焊盘所在层之外的其它层中的其中一层中,所述至少两个反焊盘中存在相邻两个反焊盘位于所述第二区段范围内,并且所述相邻两个反焊盘之间的距离大于阈值。

10.在一些实施例中,所述阈值约为8mil。

11.在一些实施例中,所述过孔与器件不连接,所述器件包括焊球和电容中的至少一

种。

12.在一些实施例中,所述第二类焊盘位于所述多个层中的除所述表层和所述第一类焊盘所在层之外的其余层中的全部层。

13.在一些实施例中,所述选定层为单个层或者多个层。

14.根据本公开的另一方面,提供了一种电子装置,该电子装置包括在前面任一实施例描述的印制电路板过孔结构。

15.根据本公开的又一方面,提供了一种优化印制电路板的过孔的阻抗波动的方法,所述印制电路板包括多个层和走线,所述过孔贯穿所述多个层,所述方法包括:获取过孔的3d模型,所述过孔包括与走线位于同一层且连接所述走线与所述过孔的第一类焊盘;基于所述过孔的仿真结果,执行如下操作:响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘以减小所述过孔的阻抗波动,所述第二类焊盘与所述走线不连接且位于所述印制电路板的选定层中,所述选定层为所述多个层中的除表层和所述第一类焊盘所在层之外的其余层中的部分层或全部层。

16.在一些实施例中,所述方法还包括:响应于所述过孔的阻抗值小于目标值,无需为所述过孔增加所述第二类焊盘。

17.在一些实施例中,所述过孔还包括表层焊盘,所述过孔经由所述表层焊盘与器件连接。所述响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘的步骤包括:确定所述过孔的第一区段,所述第一区段具有长度h并且其始端与所述表层焊盘连接,所述第一区段跨越所述多个层中的若干层;以及不在所述若干层中设置所述第二类焊盘。

18.在一些实施例中,所述过孔还包括位于所述第一区段的末端与所述第一类焊盘之间且长度为h1的第二区段。

19.在一些实施例中,所述印制电路板还包括围绕所述过孔并与所述过孔绝缘的至少两个反焊盘,所述至少两个反焊盘中的每一个位于所述多个层中的除所述第一类焊盘所在层之外的其它层中的相应一层中。所述响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘的步骤包括:响应于在所述第二区段范围内存在所述至少两个反焊盘中的相邻两个反焊盘之间的距离大于阈值,确定从所述相邻两个反焊盘中的一个所在层至所述相邻两个反焊盘中的另一个所在层所涉及的印制电路板的连续层;以及将所述连续层确定为潜在的选定层。

20.在一些实施例中,所述响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘的步骤包括:基于第二类焊盘在所述潜在的选定层的不同层中对应的过孔阻抗的仿真结果,从所述潜在的选定层中选出目标层以作为所述选定层。

21.在一些实施例中,所述响应于所述过孔的阻抗值小于目标值,无需为所述过孔增加所述第二类焊盘的步骤包括:确定所述过孔的第一区段,所述第一区段具有长度h并且其始端与所述表层焊盘连接,所述第一区段跨越所述多个层中的若干层;以及响应于所述第一类焊盘位于所述第一区段范围内,无需为所述过孔增加所述第二类焊盘。

22.在一些实施例中,所述过孔与器件不连接,所述器件包括焊球和电容中的至少一种,所述响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘的步骤包括:在所述印制电路板的多个层中的除所述表层和所述第一类焊盘所在层之外的其余

层中的全部层中增加所述第二类焊盘。

23.在一些实施例中,所述响应于所述过孔的阻抗值大于目标值,为所述过孔增加至少一个第二类焊盘的步骤包括:在所述印制电路板的选定层中为所述过孔增加所述第二类焊盘,所述选定层为单个层或者多个层。

24.根据本公开的又一方面,提供了一种计算设备,该计算设备包括:存储器,其被配置成存储计算机可执行指令;处理器,其被配置成当所述计算机可执行指令被所述处理器执行时执行如前面任一实施例描述的方法。

25.根据本公开的又一方面,提供了一种计算机程序产品,该计算机程序产品包括计算机可执行指令,该计算机可执行指令在被执行时执行如前面任一实施例描述的方法。

26.根据本公开的又一方面,提供了一种计算机可读存储介质,该计算机可读存储介质存储有计算机可执行指令,当计算机可执行指令被执行时,执行如前面任一实施例描述的方法。

27.通过在pcb过孔结构中设置第二类焊盘,利用第二类焊盘和电源/地平面之间的电容以及各个第二类焊盘之间的电容来增大过孔的电容c,减小过孔的阻抗z,从而把在目标值以上波动的过孔阻抗优化至目标值附近,减小pcb过孔结构的阻抗波动,改善pcb的通信信号质量。另外,第二类焊盘可以设置在pcb的除表层和第一类焊盘所在层以外的其余层中的一部分层中,也可以设置在pcb的除表层和第一类焊盘所在层以外的其余层中的全部层中,这使得pcb可以适用于更广泛的场景。

28.根据在下文中所描述的实施例,本公开的这些和其它方面将是清楚明白的,并且将参考在下文中所描述的实施例而被阐明。

附图说明

29.为了更清楚地描述本公开实施例中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

30.图1示出了相关技术中的pcb的走线和过孔的阻抗曲线图;图2示出了相关技术中的pcb的过孔的示意图;图3示出了pcb的反焊盘的示意图;图4-8示出了相关技术中的pcb的过孔的示意图;图9示出了pcb的过孔与焊球连接的结构示意图;图10示出了pcb的过孔与电容连接的结构示意图;图11示出了根据本公开实施例的增加第二类焊盘后的过孔的结构示意图;图12示出了根据本公开实施例的优化pcb的过孔阻抗波动的方法的流程图;图13示出了根据本公开实施例的pcb的各个层的参数;图14示出了利用本公开实施例提供的方法以及相关技术中的方法得到的过孔的阻抗曲线图;图15示出了根据本公开实施例的优化pcb的过孔阻抗的方法的流程图;图16示出了根据本公开实施例的利用仿真软件建立的过孔的3d仿真图;

图17示出了对图16中的过孔进行仿真得到的一种阻抗曲线图;图18示出了对图16中的过孔进行仿真得到的另一种阻抗曲线图;图19示出了根据本公开实施例的过孔在仿真过程中的示意图;图20示出了根据本公开实施例的过孔在仿真过程中的示意图;图21示出了根据本公开实施例的反焊盘在仿真过程中的示意图;图22示出了利用本公开实施例提供的方法以及相关技术中的方法得到的过孔的阻抗曲线图;图23示出了根据本公开实施例的电子装置的框图;以及图24出了根据本公开实施例的计算设备的框图。

具体实施方式

31.下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。基于本公开中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

32.随着pcb的信号速率越来越高,通常需要控制和优化pcb上的物理链路的阻抗以改善pcb的信号质量。在pcb的过孔处,阻抗通常会出现波动,因此过孔处的阻抗的优化对保证pcb的通信信号质量具有关键的影响作用。

33.图1是通过三维电磁场仿真工具得到的相关技术中的pcb过孔的各个位置的阻抗曲线图。图1中的横坐标是时间单位皮秒(ps),图1中的纵坐标是阻抗单位欧姆(ω)。横坐标的时间t与过孔的位置p按照如下公式映射:其中,v指电磁波沿着过孔的传播速度,c指真空中的光速,dk指电磁波传播t/2时间时,过孔对应位置处的介质的介电常数。

34.图1示出的曲线的左侧部分(对应横坐标40.00~92.00)表示走线的阻抗,图1中示出的曲线的由方框圈出的部分(对应横坐标92.00~140.00)表示过孔的阻抗。从图1可以看出,过孔的阻抗波动幅度大于走线的阻抗波动幅度,这不利于pcb的通信信号质量的稳定性和完整性。

35.传输线的阻抗公式如下:其中,r指单位长度传输线的电阻,g指单位长度传输线的导纳,l指单位长度传输线的电感,c指单位长度传输线的电容,z指传输线的阻抗,j指虚数单位,w指角频率。

36.在大部分情况下,pcb的过孔的阻抗低于设定的目标值。为了增大过孔的阻抗以使其趋近目标值,相关技术通常采用的方案是从过孔10上去除所有非功能焊盘,仅保留表层焊盘11和出线层焊盘12,如图2所示。出线层焊盘12与走线13连接,表层焊盘11与器件15(例如是焊球)连接。非功能焊盘是指过孔10上的那些与走线13没有电连接关系的焊盘。去除所

有非功能焊盘,可以减小电容c,根据上述阻抗公式可知,当电感l不变时,阻抗z随着电容c的增大而减小,随着电容c的减小而增大。因此,通过去除所有非功能焊盘,可以减小过孔10的电容c,从而可以增大过孔10的阻抗z。

37.在另一些情况下,pcb的过孔的阻抗高于设定的目标值。为了减小过孔的阻抗以使其趋近目标值,相关技术通常采用的方案是减小pcb的反焊盘的尺寸以增大电容c,从而减小过孔的阻抗z。在pcb加工时,在过孔周围的其他网络的铺铜,需要距离过孔和焊盘(包括表层焊盘11和出线层焊盘12)一定的距离,这样,铺铜在过孔周围会形成一个空洞,这个空洞称为反焊盘。由于pcb加工精度的限制,反焊盘不能无限缩小,反焊盘的边缘与过孔的边缘必须间隔一定的距离,该距离最小约为8mil。图3示出了反焊盘16的平面示意图。如图3所示,反焊盘16可以是圆形的空洞。在这样的情况下,减小反焊盘16的直径d可以增大过孔的电容c,从而减小过孔的阻抗z,使得高于目标值的过孔阻抗可以趋近目标值。

38.通过减小反焊盘的尺寸来减小过孔阻抗z的方法在大多数情况下是有效的,但是由于加工能力问题,反焊盘的尺寸可减小的幅度有限,不能无限制地减小,因此反焊盘的尺寸的减小对阻抗的优化作用也是有限的。

39.过孔局部(或整体)的电感相对较强或者电容相对较弱的情景的示例包括但不限于如下几种情况:i. 如图4所示,在pcb的多层结构中,某一对或多对相邻层之间的介质厚度t远大于其他相邻层之间的介质厚度,图4作为示例仅示出了一对相邻层之间的介质厚度t远大于其他相邻层之间的介质厚度。这样会造成过孔在具有较厚介质厚度t的区段的平均分布电容远小于过孔的其他区段的平均分布电容,从而造成过孔在具有较厚介质厚度t的区段处的阻抗在目标值以上波动。出现这种具有不均匀介质厚度的层叠结构的原因通常如下:(a)pcb的相邻两层在空间上有重合的布线,为了减少相邻两层布线间的串扰,需要拉大相邻两层之间的介质厚度;(b)pcb通常有厚度要求,有时为了满足pcb的厚度要求,需要加大部分相邻层之间的介质厚度。

40.ii. 如图5所示,虽然pcb的层叠结构上没有出现某相邻两层之间的介质厚度很大的情况,但是在pcb的连续两层或多层中没有在过孔周围铺铜。出于布局设计上的考虑,图5中1、2指示的两层未在过孔周围铺铜,这样就造成了过孔的局部(即由位于图5中的数字1上方的反焊盘和数字2下方的反焊盘所界定的区域)分布电容较小,从而造成过孔在该局部的阻抗在目标值以上波动。

41.iii. 如图6所述,在pcb的某些布线密集区域,经常会使用孔径d2小于常规孔径d1的过孔,过孔的孔径d2例如小于或等于8mil。过孔的孔径越小,过孔的单位长度的分布电感就越大,这样就会导致过孔的阻抗整体偏大,从而使得过孔阻抗在目标值以上波动。

42.上述三种场景中的任一种场景都会导致过孔局部的阻抗在目标值以上波动。为了减小过孔的阻抗,相关技术只能通过减小相应层的反焊盘的尺寸以增大过孔的分布电容c,从而在一定程度上可以减小过孔的阻抗。但是由于pcb的制造能力的限制,反焊盘尺寸并不能无限缩小,所以通过缩小各层反焊盘的尺寸并不能有效的减小高于目标值的过孔阻抗的波动。

43.相关技术有试图不加区分地在表层和出线层以外的所有层增加非功能焊盘来改善过孔的单位长度分布电容的一致性的方案,如图7所示。对于过孔20,除了表层焊盘21所

在层l1以及出线层焊盘22所在层l2和l4之外,pcb的其他层l3、l5及l6均设置有非功能焊盘24。为达到单位长度分布电容的一致性的目的,该方案要求l1~l6中的任意相邻两个叠层之间的间距需要保持一致,应用场景十分有限,如果过孔还连接有其他器件,或者过孔具有图9所示的残桩(残桩是指过孔上未使用的部分),或者pcb具有非均匀的层叠结构,则该方案都难以取得相应的效果。

44.在实际中,过孔通常需要与器件连接,该器件例如是bga(ball grid array)焊球或电容。图9示出了bga焊球15与过孔相连的示意图,图10示出了电容17与过孔相连的示意图。在工程实践中需要将与过孔相连的器件、连接器件与过孔的导线、以及过孔这三者作为一个整体来进行整体的阻抗优化。具有非均匀层叠结构的pcb在工程实践中往往是常见和必要的。

45.本公开的实施例提供了一种pcb过孔结构以及优化pcb过孔阻抗波动的方法,可以将在目标值以上波动的过孔阻抗减小至目标值附近,从而减小过孔处的阻抗的波动,改善pcb的信号质量,适用工程中常见的各种多层pcb。

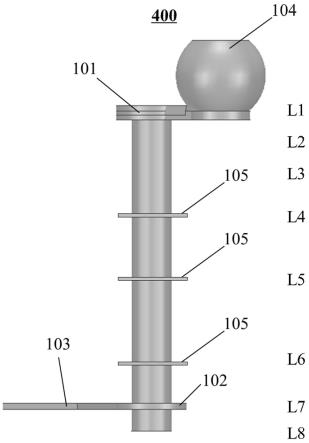

46.图11示出了根据本公开实施例的pcb过孔结构400的结构示意图。如图11所示,pcb包括多个层和走线103,该pcb过孔结构400包括过孔,过孔贯穿多个层并且包括第一类焊盘102和第二类焊盘105,图中示出了三个第二类焊盘105。第一类焊盘102与走线103位于同一层并且连接走线103与过孔。第二类焊盘105与走线103不连接且位于pcb的选定层中以减小过孔的阻抗波动,选定层为pcb的上述多个层中的除表层和第一类焊盘102所在层之外的其余层中的部分层或全部层,或者说选定层的层数小于或等于所述其余层的层数。选定层可以是单个层,也可以是多个层。当选定层为单个层时,意指第二类焊盘105位于pcb的多个层中的除表层和第一类焊盘102所在层之外的其余某一个层中。当选定层为多个层时,意指第二类焊盘105位于pcb的多个层中的除表层和第一类焊盘102所在层之外的其余多个层中的任意组合层中。

47.需要说明的是,术语“第一类焊盘”是指与走线103相连的焊盘,即普通焊盘,第一类焊盘可以增强pcb走线和过孔间的机械连接性能,有利于pcb的机械加工制作,在本文中,术语“第一类焊盘”和“普通焊盘”可以可互换地使用。术语“第二类焊盘”是指非功能焊盘,即与走线103没有电连接关系的那些焊盘,在本文中,术语“第二类焊盘”和“非功能焊盘”可以可互换地使用。

48.过孔还包括表层焊盘101。在一些实施例中,过孔经由表层焊盘101和导线与器件104连接。在替代的实施例中,过孔与器件104不连接,在这样的情况下,第二类焊盘105位于pcb的多个层中的除表层和第一类焊盘102所在层之外的其余层中的全部层中。器件104例如可以是bga焊球和电容中的至少一种。

49.参考图20,在一些实施例中,过孔200包括第一区段q1,第一区段q1具有长度h并且其始端与表层焊盘101连接,第一区段q1跨越多个层中的若干层,例如跨越pcb的第1层至第3层,并且第二类焊盘105未设置在上述若干层中。在一个示例中,长度h约为15mil。

50.如图20所示,第一类焊盘102位于第一区段q1远离表层焊盘101的一侧,过孔200还包括位于第一区段q1的末端与第一类焊盘102之间且长度为h1的第二区段q2。在一些实施例中,pcb还包括围绕过孔200并与过孔200绝缘的至少两个反焊盘,每个反焊盘位于pcb的多个层中的除第一类焊盘102所在层之外的其它层中的其中一层中,至少两个反焊盘中的

相邻两个反焊盘位于第二区段q2的范围内,并且相邻两个反焊盘之间的距离h2大于阈值。在一个示例中,阈值约为8mil。在替代的实施例中,pcb可以不包括反焊盘。

51.通过在pcb过孔结构400中设置第二类焊盘105,利用第二类焊盘105和电源/地平面之间的电容以及各个第二类焊盘105之间的电容来增大过孔的电容c,减小过孔的阻抗z,从而把在目标值以上波动的过孔阻抗优化至目标值附近,减小pcb过孔结构400的阻抗波动,改善pcb的通信信号质量。另外,第二类焊盘105可以设置在pcb的除表层和第一类焊盘102所在层以外的其余层中的一部分层中,也可以设置在pcb的除表层和第一类焊盘102所在层以外的其余层中的全部层中,这使得pcb可以适用于更广泛的场景。

52.在一些实施例中,参照图11,pcb具有8个层,分别是第1层l1至第8层l8,并且第一类焊盘102位于pcb的第7层,第二类焊盘105分别位于pcb的第4层、第5层、以及第6层。当pcb具有8个层且在pcb的第4、5、6层增加第二类焊盘105时,可以将过孔的阻抗波动降至最小,进一步改善pcb的通信信号质量。

53.图12示出了根据本公开实施例的优化pcb的过孔阻抗波动的方法100,本公开实施例提供的pcb包括多个层,过孔贯穿多个层,方法100包括如下步骤:110:获取过孔的3d模型,过孔包括与走线位于同一层且连接走线与过孔的第一类焊盘。

54.需要注意的是,过孔的3d模型是根据实际pcb的层叠结构来建立的,pcb的层叠结构不同,其过孔的3d模型相应也是不同的。

55.120:基于过孔的仿真结果,执行如下步骤的操作。

56.130:判断过孔的阻抗值是否大于目标值,如果是,则转入步骤140;如果否,则转入步骤150。

57.140:为过孔增加至少一个第二类焊盘,第二类焊盘与走线不连接且位于pcb的选定层中,选定层为pcb的多个层中的除表层和第一类焊盘所在层之外的其余层中的部分层或全部层,或者说选定层的层数小于或等于所述其余层的层数,第二类焊盘配置为减小过孔的阻抗波动。

58.150:响应于过孔的阻抗值小于目标值,无需为过孔增加第二类焊盘,增大反焊盘的尺寸。

59.在一些实施例中,过孔与器件不连接,器件可以是焊球和电容中的至少一种。在这种情况下,在印制电路板的多个层中的除表层和第一类焊盘所在层之外的其余层中的全部层中增加第二类焊盘。

60.在一些实施例中,出现过孔的阻抗值小于目标值而无需为过孔增加第二类焊盘的一种情况是,参考图20,过孔具有第一区段q1,第一区段q1具有长度h并且其始端与表层焊盘101连接,第一区段q1跨越pcb的多个层中的若干层。但是与图20不同的是,第一类焊盘位于第一区段q1的范围内,即第一类焊盘位于pcb的离表层焊盘101较近的膜层中,例如第一类焊盘位于pcb的第2层或第3层中。在这种情况下,无需为过孔设置任何第二类焊盘。

61.简而言之,在方法100中,可以在pcb的多个层中的除表层和第一类焊盘所在层之外的其余层中的单个层中添加第二类焊盘,或者可以在pcb的多个层中的除表层和第一类焊盘所在层之外的其余层中的多个层中添加第二类焊盘,或者可以在pcb的多个层中的除表层和第一类焊盘所在层之外的其余层中的全部层中添加第二类焊盘,或者还可以不在

pcb中添加第二类焊盘。

62.在方法100中,第二类焊盘设置在pcb的选定层中,而选定层为pcb的多个层中的除表层和第一类焊盘所在层之外的其余层中的部分层或全部层。简而言之,在方法100中,既可以在pcb的除表层和第一类焊盘所在层以外的其余层中的部分层中设置第二类焊盘,也可以在pcb的除表层和第一类焊盘所在层以外的其余层中的全部层中设置第二类焊盘,即方法100涵盖了图7的非功能焊盘24的布置方式,可以适用于更多的场景。通过利用第二类焊盘和电源/地平面之间的电容以及各个第二类焊盘之间的电容,以此来增大过孔的电容c,减小过孔的阻抗z,从而把在目标值以上波动的过孔阻抗优化至目标值附近,减小过孔的阻抗波动。另外,如前所述,相关技术提供的通过减小反焊盘的尺寸来减小过孔阻抗z的方法不适用于图4~6示出的场景,相关技术提供的图7的方法不适用于图9~10的场景。相比之下,本公开实施例提供的方法100适用于各种场景,包括但不限于图4~6和图9~10示出的场景。

63.为了进一步印证方法100的有益效果,本技术的发明人以具有8层层叠结构的pcb为例,对通过相关技术的方法得到的过孔阻抗以及本公开实施例提供的方法100得到的过孔阻抗进行了对比,图13示出了该示例pcb的各个层的参数,图14示出了阻抗对比曲线图。在该示例pcb中,过孔与bga焊球相连,并且出线层焊盘位于第7层。图13中的介质厚度和铜厚的单位均为mil,通过图13可以看到,相邻层间的介质厚度并不是均匀的,这种不均匀层间距的层叠设计在工程实践中是非常常见的。

64.在图14中,横坐标是时间单位ps,纵坐标是阻抗单位ω。阿拉伯数字“1”指代的曲线表示采用图2的方法(即移除所有非功能焊盘)得到的过孔的阻抗曲线,阿拉伯数字“2”指代的曲线表示采用图7的方法(即保留所有非功能焊盘)得到的过孔的阻抗曲线,阿拉伯数字“3”指代的曲线表示仅在部分层中设置非功能焊盘得到的过孔的阻抗曲线。从图14可以看到,阿拉伯数字“3”指代的曲线,即,在pcb的除表层和第一类焊盘所在层以外的其余层中的部分层中设置非功能焊盘,对过孔的阻抗波动的改善最为显著。

65.通过设置第二类焊盘来改善过孔的阻抗波动,从而将在目标值以上波动的阻抗降低至目标值附近。具体在哪几层设置第二类焊盘,这与pcb的层数、走线从第几层出线、过孔的有效长度、电源/地平面数量等诸多因素有关,不能一概而论。本技术基于方法100进一步提供了一种普适性的方法300,可针对不同的场景确定需要在哪几层设置第二类焊盘,以实现对过孔阻抗波动的最优改善。

66.图15示意性地示出了方法300的流程图,该方法300的步骤如下:210:获取过孔的3d模型,3d模型的示意图如图16所示。如前所述,过孔的3d模型是根据实际pcb的层叠结构来建立的,pcb的层叠结构不同,其过孔的3d模型相应也是不同的。

67.可以在诸如高频结构仿真(hfss)的电磁场仿真工具中建立过孔的3d模型。在一个实施例中,pcb可以是厚度为1.57mm且具有8层层叠结构的电路板,该pcb的换层过孔从表层换层到第7层,bga焊球和过孔相连。

68.220:在模型中去除所有非功能焊盘。需要说明的是,该步骤可以与步骤210合并执行,即在建立过孔的3d模型时就已去除所有非功能焊盘,也可以在步骤210之后单独执行。然后,对过孔的阻抗进行仿真,如果过孔的阻抗在目标值以上波动,则需要增加第二类焊盘,进入步骤230;如果过孔的阻抗在目标值以下波动,则不需要增加第二类焊盘,只需适当

地调大各层反焊盘的尺寸以增大过孔阻抗即可。如图17所示,方框圈出的曲线表示过孔的阻抗波动曲线,可以看出,过孔的阻抗波动最大值超出了目标阻抗值(45ω)约7ω,这种情况就明显需要增加第二类焊盘。相反地,如图18所示,方框圈出的曲线表示过孔的阻抗波动曲线,可以看出,过孔的阻抗基本上均在目标阻抗值(45ω)以下波动,这种情况就无需增加第二类焊盘。需要说明的是,短语“如果过孔的阻抗在目标值以上波动,则需要增加第二类焊盘;如果过孔的阻抗在目标值以下波动,则不需要增加第二类焊盘”并不是一个完全绝对的概念,在实际中,当过孔的阻抗在目标阻抗值+/-2ω范围内波动时,是否增加第二类焊盘对过孔的阻抗影响并不十分明显,因此,当目标阻抗值<过孔的阻抗值<目标阻抗值+2ω时,可以增加第二类焊盘,也可以不增加第二类焊盘;类似地,当目标阻抗值-2ω<过孔的阻抗值<目标阻抗值时,可以不增加第二类焊盘,也可以增加第二类焊盘。但是,当过孔的阻抗在目标阻抗值的上下更大范围内(例如+/-5ω)波动时,则如前所述,过孔的阻抗在目标值以上波动则增加第二类焊盘,过孔的阻抗在目标值以下波动则不增加第二类焊盘。

69.方法100中的步骤140“响应于过孔的阻抗值大于目标值,为过孔增加至少一个第二类焊盘”可以进一步包括如下步骤230~280。

70.如图19所示,本公开实施例提供的过孔200包括表层焊盘101,过孔200经由表层焊盘101和导线与器件104连接。在一个示例中,器件104是bga焊球。

71.230:参照图19,确定过孔200的第一区段q1,该第一区段q1具有长度h并且其始端与表层焊盘101连接,第一区段q1跨越pcb的多个层中的若干层。

72.240:不在上述若干层中设置第二类焊盘。

73.参考图19,与过孔200相连的器件104和过孔200的第一区段q1构成一个整体,该整体的平均分布电感和平均分布电容决定了该区域的阻抗。而与过孔200相连的器件104的尺寸通常大于过孔200的尺寸,因此器件104的分布电感相对更小,这样会造成由器件104和过孔200的第一区段q1构成的整体的阻抗跌落至小于目标值。如果在该第一区段q1增加第二类焊盘,会导致该区域的阻抗进一步减小,这是不希望看到的。由于具有长度h的第一区段q1跨越pcb的多个层中的若干层,因此,不能在上述若干层中设置第二类焊盘。在一些实施例中,上述若干层可以包括pcb的第1~3层。在一些实施例中,长度h约为15mil,即从图19中的过孔200的表层焊盘101往下15mil范围内,不设置第二类焊盘。当然,如果过孔200不与其他器件相连,则不存在该约束。

74.图20示出了过孔200更为详细的结构,如图所示,过孔200包括前面提到的第一类焊盘102,该第一类焊盘102与走线103连接。第一类焊盘102位于第一区段q1远离表层焊盘101的一侧。过孔200还包括位于第一区段q1的末端与第一类焊盘102之间且长度为h1的第二区段q2,pcb还包括围绕过孔200并与过孔200绝缘的至少两个反焊盘,图21示出了反焊盘的平面示意图,每个反焊盘位于pcb的多个层中的除第一类焊盘102所在层之外的其它层中的相应一层中。当然,在替代的实施例中,pcb可以不包括反焊盘。

75.250:参考图20,判断在过孔200的第二区段q2范围内是否存在相邻两个反焊盘之间的距离大于阈值,如果是,则转到步骤260;如果否,则转到步骤290。在一些实施例中,阈值例如可以是8mil。

76.260:确定从相邻两个反焊盘中的一个所在层至相邻两个反焊盘中的另一个所在层所涉及的pcb的连续层。

77.需要说明的是,步骤260中的术语“pcb的连续层”是指,假设相邻两个反焊盘中的一个所在层为pcb的第m层,相邻两个反焊盘中的另一个所在层为pcb的第n层,n>m,则pcb的连续层包括第m层、第(m+1)层、第(m+2)层

……

第(n-2)层、第(n-1)层、第n层。例如,相邻两个反焊盘中的一个所在层为pcb的第4层,相邻两个反焊盘中的另一个所在层为pcb的第6层,则pcb的连续层是指pcb的第4~6层。

78.270:将上述连续层确定为潜在的选定层。

79.由前文得知,在pcb的选定层中设置第二类焊盘。“潜在的选定层”是指步骤260确定的这些连续层有可能成为选定层,即有可能在这些连续层中都设置第二类焊盘,也有可能仅在这些连续层中的部分层中设置第二类焊盘,截止到此步骤,实现了选定层的初选和确定。连续层中的具体哪些(个)层是最终的选定层,还需依赖下面的步骤来进一步确定。

80.图20示出的过孔200从第1层l1贯穿至第8层l8,即pcb包括8个层,第一类焊盘102位于第7层l7。如图20所示,第4层的反焊盘和第6层的反焊盘之间的距离为h2,第5层没有反焊盘,因此,第4层的反焊盘和第6层的反焊盘即为前文所述的“相邻的两个反焊盘”。在一个实施例中,h2等于29.92mil,远大于阈值8mil。在该情况下,pcb的第4层至第6层为潜在的选定层,因此,第4层、第5层、第6层都有可能增加第二类焊盘。

81.280:基于第二类焊盘在潜在的选定层的不同层中对应的过孔阻抗的仿真结果,从潜在的选定层中选出目标层以作为选定层。

82.假设第一类焊盘位于pcb的第x层,那么从第(x-1)层逐层往上增加第二类焊盘,并针对添加的第二类焊盘的每种情况分别进行过孔的阻抗仿真,根据仿真结果确定第二类焊盘添加位置的最优组合。

83.在一个示例中,依然以8层pcb为例,针对步骤270确认的潜在的选定层,由于第一类焊盘位于第7层,因此从第6层开始,直到第4层,逐层增加第二类焊盘进行过孔阻抗仿真,根据仿真结果确定第二类焊盘的最优组合。图22示出了三种情况对应的过孔阻抗的仿真图。在图22中,字母a指代的曲线表示只在第6层增加第二类焊盘后的过孔的阻抗曲线图,字母b指代的曲线表示只在第5层和第6层增加第二类焊盘后的过孔的阻抗曲线图,字母c指代的曲线表示在第4、5、6层均增加第二类焊盘后的过孔的阻抗曲线图。从图22的仿真结果可以看到,在第4、5、6层均增加第二类焊盘,过孔的阻抗波动是最小的。

84.290:结束。

85.通过方法300,不仅可以把在目标值以上波动的过孔阻抗降低至目标值附近,减小过孔的阻抗波动,改善pcb的通信信号质量,还可以确定出具体在pcb的哪层或哪几层增加第二类焊盘可以得到最优的阻抗优化效果,使得过孔的阻抗波动最小。

86.需要说明的是,虽然本文仅列举了具有8层叠层结构的pcb,但是本公开实施例提供的pcb过孔结构400以及方法100和300可以适用于各种叠层的pcb过孔结构。另外,虽然本文提到了第一类焊盘可以位于8层pcb的第7层,但这仅是一个示例,第一类焊盘可以位于pcb的任意层中。另外,本公开实施例提供的方法100和300对于差分线的换层过孔同样适用。

87.图23示意性示出了根据本公开的一些实施例的电子装置500的示例框图,电子装置500包括在前面任一实施例描述的pcb过孔结构400。

88.电子装置500可以具有与前面实施例描述的pcb过孔结构400基本相同的技术效

果,出于简洁的目的,此处不再重复描述电子装置500的技术效果。

89.图24示意性示出了根据本公开的一些实施例的计算设备700的示例框图。

90.如图24所示,计算设备700包括彼此通信耦合的处理系统701、一个或多个计算机可读介质702以及一个或多个输入/输出(i/o)接口703。尽管未示出,但是计算设备700还可以包括将各种组件彼此耦合的系统总线或其他数据和命令传送系统。系统总线可以包括不同总线结构的任何一个或组合,所述总线结构可以是诸如存储器总线或存储器控制器、外围总线、通用串行总线和/或利用各种总线架构中的任何一种的处理器或局部总线,或者还可以包括诸如控制和数据线。

91.处理系统701代表使用硬件执行一个或多个操作的功能。因此,处理系统701被图示为包括可被配置为处理器、功能块等的硬件元件704。这可以包括在硬件中实现专用集成电路或使用一个或多个半导体形成的其它逻辑器件。硬件元件704不受其形成材料或其中采用的处理机构的限制。例如,处理器可以由(多个)半导体和/或晶体管(例如,电子集成电路(ic))组成。在这样的上下文中,处理器可执行指令可以是电子可执行指令。

92.计算机可读介质702被图示为包括存储器/存储装置705。存储器/存储装置705表示与一个或多个计算机可读介质相关联的存储器/存储装置。存储器/存储装置705可以包括易失性存储介质(诸如随机存取存储器(ram))和/或非易失性存储介质(诸如只读存储器(rom)、闪存、光盘、磁盘等)。存储器/存储装置705可以包括固定介质(例如,ram、rom、固定硬盘驱动器等)以及可移动介质(例如,闪存、可移动硬盘驱动器、光盘等)。示例性地,存储器/存储装置705可以用于存储存储计算机可执行指令,当该计算机可执行指令被处理器执行时执行前面实施例描述的优化印制电路板的过孔阻抗的方法。计算机可读介质702可以以下面进一步描述的各种其他方式进行配置。

93.一个或多个输入/输出接口703代表允许用户向计算设备700键入命令和信息并且还允许使用各种输入/输出设备将信息呈现给用户和/或发送给其他组件或设备的功能。输入设备的示例包括键盘、光标控制设备(例如,鼠标)、麦克风(例如,用于语音输入)、扫描仪、触摸功能(例如,被配置为检测物理触摸的容性或其他传感器)、相机(例如,可以采用可见或不可见的波长(诸如红外频率)将不涉及触摸的运动检测为手势)、网卡、接收机等等。输出设备的示例包括显示设备(例如,显示器或投影仪)、扬声器、打印机、触觉响应设备、网卡、发射机等。

94.本文可以在软件、硬件、元件或程序模块的一般上下文中描述各种技术。一般地,这些模块包括执行特定任务或实现特定抽象数据类型的例程、程序、对象、元素、组件、数据结构等。本文所使用的术语“模块”、“功能”等一般表示软件、固件、硬件或其组合。本文描述的技术的特征是与平台无关的,意味着这些技术可以在具有各种处理器的各种计算平台上实现。

95.所描述的模块和技术的实现可以存储在某种形式的计算机可读介质上或者跨某种形式的计算机可读介质传输。计算机可读介质可以包括可由计算设备700访问的各种介质。作为示例而非限制,计算机可读介质可以包括“计算机可读存储介质”和“计算机可读信号介质”。

96.与单纯的信号传输、载波或信号本身相反,“计算机可读存储介质”是指能够持久存储信息的介质和/或设备,和/或有形的存储装置。因此,计算机可读存储介质是指非信号

承载介质。计算机可读存储介质包括诸如易失性和非易失性、可移动和不可移动介质和/或以适用于存储信息(诸如计算机可执行指令、数据结构、程序模块、逻辑元件/电路或其他数据)的方法或技术实现的存储设备之类的硬件。计算机可读存储介质的示例可以包括但不限于ram、rom、eeprom、闪存或其它存储器技术、cd-rom、数字通用盘(dvd)或其他光学存储装置、硬盘、盒式磁带、磁带,磁盘存储装置或其他磁存储设备,或其他存储设备、有形介质或适于存储期望信息并可以由计算机访问的制品。

[0097]“计算机可读信号介质”是指被配置为诸如经由网络将指令发送到计算设备700的硬件的信号承载介质。信号介质典型地可以将计算机可执行指令、数据结构、程序模块或其他数据体现在诸如载波、数据信号或其它传输机制的调制数据信号中。信号介质还包括任何信息传递介质。作为示例而非限制,信号介质包括诸如有线网络或直接连线的有线介质以及诸如声、rf、红外和其它无线介质的无线介质。

[0098]

如前所述,硬件元件704和计算机可读介质702代表以硬件形式实现的指令、模块、可编程器件逻辑和/或固定器件逻辑,其在一些实施例中可以用于实现本文描述的技术的至少一些方面。硬件元件可以包括集成电路或片上系统、专用集成电路(asic)、现场可编程门阵列(fpga)、复杂可编程逻辑器件(cpld)以及硅中的其它实现或其他硬件设备的组件。在这种上下文中,硬件元件可以作为执行由硬件元件所体现的指令、模块和/或逻辑所定义的程序任务的处理设备,以及用于存储用于执行的指令的硬件设备,例如,先前描述的计算机可读存储介质。

[0099]

前述的组合也可以用于实现本文所述的各种技术和模块。因此,可以将软件、硬件或程序模块和其它程序模块实现为在某种形式的计算机可读存储介质上和/或由一个或多个硬件元件704体现的一个或多个指令和/或逻辑。计算设备700可以被配置为实现与软件和/或硬件模块相对应的特定指令和/或功能。因此,例如通过使用处理系统的计算机可读存储介质和/或硬件元件704,可以至少部分地以硬件来实现将模块实现为可由计算设备700作为软件执行的模块。指令和/或功能可以由例如一个或多个计算设备700和/或处理系统701执行/可操作以实现本文所述的技术、模块和示例。

[0100]

本文描述的技术可以由计算设备700的这些各种配置来支持,并且不限于本文所描述的技术的具体示例。

[0101]

应当理解,为清楚起见,参考不同的功能单元对本公开的实施例进行了描述。然而,将明显的是,在不偏离本公开的情况下,每个功能单元的功能性可以被实施在单个单元中、实施在多个单元中或作为其它功能单元的一部分被实施。例如,被说明成由单个单元执行的功能性可以由多个不同的单元来执行。因此,对特定功能单元的参考仅被视为对用于提供所描述的功能性的适当单元的参考,而不是表明严格的逻辑或物理结构或组织。因此,本公开可以被实施在单个单元中,或者可以在物理上和功能上被分布在不同的单元和电路之间。

[0102]

本公开的实施例提供了一种计算机可读存储介质,其上存储有计算机可执行指令,计算机可执行指令在被执行时实现上述优化印制电路板的过孔阻抗波动的方法。

[0103]

本公开的实施例提供了一种计算机程序产品或计算机程序,该计算机程序产品或计算机程序包括计算机可执行指令,该计算机可执行指令存储在计算机可读存储介质中。计算设备的处理器从计算机可读存储介质读取该计算机可执行指令,处理器执行该计算机

可执行指令,使得该计算设备执行上述各种实施例中提供的优化印制电路板的过孔阻抗波动的方法。

[0104]

将理解的是,尽管术语第一、第二、第三等在本文中可以用来描述各种元件、部件、区、层和/或部分,但是这些元件、部件、区、层和/或部分不应当由这些术语限制。这些术语仅用来将一个元件、部件、区、层或部分与另一个区、层或部分相区分。因此,上面讨论的第一元件、部件、区、层或部分可以被称为第二元件、部件、区、层或部分而不偏离本公开的教导。

[0105]

本文中使用的术语仅出于描述特定实施例的目的并且不意图限制本公开。如本文中使用的,单数形式“一个”、“一”和“该”意图也包括复数形式,除非上下文清楚地另有指示。将进一步理解的是,术语“包括”和/或“包含”当在本说明书中使用时指定所述特征、整体、步骤、操作、元件和/或部件的存在,但不排除一个或多个其他特征、整体、步骤、操作、元件、部件和/或其群组的存在或增加一个或多个其他特征、整体、步骤、操作、元件、部件和/或其群组。如本文中使用的,术语“和/或”包括相关联的列出项目中的一个或多个的任意和全部组合。在本说明书的描述中,参考术语“一个实施例”、“另一个实施例”等的描述意指结合该实施例描述的具体特征、结构、材料或者特点包含于本公开的至少一个实施例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

[0106]

除非另有定义,本文中使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域的普通技术人员所通常理解的相同含义。将进一步理解的是,诸如那些在通常使用的字典中定义的之类的术语应当被解释为具有与其在相关领域和/或本说明书上下文中的含义相一致的含义,并且将不在理想化或过于正式的意义上进行解释,除非本文中明确地如此定义。

[0107]

以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此。任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1