比较器及数据转换器的制作方法

1.本发明涉及集成电路技术领域,尤其涉及一种比较器及数据转换器。

背景技术:

2.逐次逼近型模数转换器(successive approximation analog-digital converter,sar adc)是一种逐次比较型的数据转换器,在每一次进行数据转换的过程中,电路内部会使用2分法进行逐次比对,最后将输入模拟量转换成若干比特的输出数字量。在逐次比较的过程中,会使用到高精度的电压比较器。

3.现有技术中会通过误差消除电路消除电压比较器中的输入误差,但误差消除电路中采用了传输门作为开关,而传输门的源极和漏极到衬底的漏电不一致,也会造成额外的误差。

4.因此,有必要提供一种新型的比较器及数据转换器以解决现有技术中存在的上述问题。

技术实现要素:

5.本发明的目的在于提供一种比较器及数据转换器,以减少输入误差。

6.为实现上述目的,本发明的所述比较器,包括若干级前置放大电路、动态锁存比较电路以及误差消除电路,第一级所述前置放大电路的第一输入端和第二输入端分别用于接收待比较数据,后一级所述前置放大电路的第一输入端与前一级所述前置放大电路的第一输出端连接,后一级所述前置放大电路的第二输入端与前一级所述前置放大电路的第二输出端连接,所述动态锁存比较电路第一输入端与最后一级所述前置放大电路的第一输出端连接,所述动态锁存比较电路第二输入端与最后一级所述前置放大电路的第二输出端连接,所述误差消除电路与部分所述前置放大电路和所述动态锁存比较电路连接,以消除所述前置放大电路的输入误差和所述动态锁存比较电路的输入误差。

7.所述比较器的有益效果在于:所述误差消除电路与部分所述前置放大电路和所述动态锁存比较电路连接,以消除所述前置放大电路的输入误差和所述动态锁存比较电路的输入误差,进而减少了所述比较器的误差。

8.可选地,若干级所述前置放大电路包括第一级前置放大电路、第二级前置放大电路、第三级前置放大电路、第四级前置放大电路,所述第一级前置放大电路的第一输入端和第二输入端分别用于接收待比较数据,所述第二级前置放大电路的第一输入端与所述第一级前置放大电路的第一输出端连接,所述第二级前置放大电路的第二输入端与所述第一级前置放大电路的第二输出端连接,所述第三级前置放大电路的第一输入端与所述第二级前置放大电路的第一输出端连接,所述第三级前置放大电路的第二输入端与所述第二级前置放大电路的第二输出端连接,所述第四级前置放大电路的第一输入端与所述第三级前置放大电路的第一输出端连接,所述第四级前置放大电路的第二输入端与所述第三级前置放大电路的第二输出端连接。

9.可选地,所述误差消除电路与所述第三级前置放大电路、所述第四级前置放大电路和所述动态锁存比较电路连接。

10.可选地,所述第一级前置放大电路、所述第二级前置放大电路、所述第三级前置放大电路和所述第四级前置放大电路均包括第一电阻、第二电阻、第一nmos管、第二nmos管和第一电流源,所述第一电阻的一端和所述第二电阻的一端均接电源电压,所述第一电阻的另一端与所述第一nmos管的漏极连接,所述第二电阻的另一端与所述第二nmos管的漏极连接,所述第一nmos管的源极和所述第二nmos管的源极与所述第一电流源的正极连接,所述第一电流源的负极接地,所述第一nmos管的栅极为第一输入端,所述第二nmos管的栅极为第二输入端。

11.可选地,所述第一级前置放大电路和所述第二级前置放大电路中第一nmos管的尺寸和第二nmos管的尺寸大于所述第三级前置放大电路和所述第四级前置放大电路中第一nmos管的尺寸和第二nmos管的尺寸。

12.可选地,所述误差消除电路包括若干误差消除子电路,所述误差消除子电路包括电容和开关,所述电容的一端与所述开关的一端连接,所述开关的另一端接阈值电压。

13.可选地,所述动态锁存比较电路包括第一pmos管、第二pmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管和第二电流源,所述第一pmos管的源极和所述第二pmos管的源极均接电源电压,所述第一pmos管的漏极与所述第三nmos管的漏极、所述第二pmos管的栅极和所述第四nmos管的栅极连接,所述第二pmos管的漏极与所述第四nmos管的漏极、所述第一pmos管的栅极和所述第三nmos管的栅极连接,所述第三nmos管的源极与所述第五nmos管的漏极连接,作为所述动态锁存比较电路的第一输出端,所述第四nmos管的源极与所述第六nmos管的漏极连接,作为所述动态锁存比较电路的第二输出端,所述第五nmos管的源极和所述第六nmos管的源极均与所述第二电流源的正极连接,所述第二电流源的负极接地,所述第五nmos管的栅极为所述动态锁存比较电路的第一输入端,所述第六nmos管的栅极为所述动态锁存比较电路的第二输入端。

14.本发明还提供了一种数据转换器,包括所述比较器。

附图说明

15.图1为现有技术中传统比较器的电路示意图;

16.图2为现有技术中开关的示意图;

17.图3为本发明一些实施例中比较器的电路示意图。

具体实施方式

18.为使本发明的目的、技术方案和优点更加清楚,下面将结合本发明的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。除非另外定义,此处使用的技术术语或者科学术语应当为本发明所属领域内具有一般技能的人士所理解的通常意义。本文中使用的“包括”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。

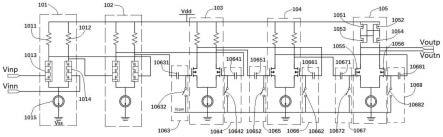

19.图1为现有技术中传统比较器的电路示意图。参照图1,传统比较器包括第一级前置放大电路101、第二级前置放大电路102、第三级前置放大电路103、第四级前置放大电路104、动态锁存比较电路105和误差消除电路。

20.参照图1,所述第一级前置放大电路101、所述第二级前置放大电路102、所述第三级前置放大电路103和所述第四级前置放大电路104均包括第一电阻1011、第二电阻1012、第一nmos管1013、第二nmos管1014和第一电流源1015,所述第一电阻1011的一端和所述第二电阻1012的一端均接电源电压,所述第一电阻1011的另一端与所述第一nmos管1013的漏极连接,作为第二输出端,所述第二电阻1012的另一端与所述第二nmos管1014的漏极连接,作为第一输出端,所述第一nmos管1013的源极和所述第二nmos管1014的源极与所述第一电流源1015的正极连接,所述第一电流源1015的负极接地,所述第一nmos管1013的栅极为第一输入端,所述第二nmos管1014的栅极为第二输入端。

21.参照图1,所述动态锁存比较电路105包括第一pmos管1051、第二pmos管1052、第三nmos管1053、第四nmos管1054、第五nmos管1055、第六nmos管1056和第二电流源1057,所述第一pmos管1051的源极和所述第二pmos管1052的源极均接电源电压,所述第一pmos管1051的漏极与所述第三nmos管1053的漏极、所述第二pmos管1052的栅极和所述第四nmos管1054的栅极连接,所述第二pmos管1052的漏极与所述第四nmos管1054的漏极、所述第一pmos管1051的栅极和所述第三nmos管1053的栅极连接,所述第三nmos管1053的源极与所述第五nmos管1055的漏极连接,作为所述动态锁存比较电路105的第一输出端,所述第四nmos管1054的源极与所述第六nmos管1056的漏极连接,作为所述动态锁存比较电路105的第二输出端,所述第五nmos管1055的源极和所述第六nmos管1056的源极均与所述第二电流源1057的正极连接,所述第二电流源1057的负极接地,所述第五nmos管1055的栅极为所述动态锁存比较电路105的第一输入端,所述第六nmos管1056的栅极为所述动态锁存比较电路105的第二输入端。

22.参照图1,所述误差消除电路包括八个误差消除子电路,八个所述误差消除子电路分别为第一误差消除子电路1061、第二误差消除子电路1062、第三误差消除子电路1063、第四误差消除子电路1064、第五误差消除子电路1065、第六误差消除子电路1066、第七误差消除子电路1067和第八误差消除子电路1068,所述第一误差消除子电路1061包括第一电容10611和第一开关10612,所述第二误差消除子电路1062包括第二电容10621和第二开关10622,所述第三误差消除子电路1063包括第三电容10631和第三开关10632,所述第四误差消除子电路1064包括第四电容10641和第四开关10642,所述第五误差消除子电路1065包括第五电容10651和第五开关10652,所述第六误差消除子电路1066包括第六电容10661和第六开关10662,所述第七误差消除子电路1067包括第七电容10671和第七开关10672,所述第八误差消除子电路1068包括第八电容10681和第八开关10682。

23.参照图1,所述第一电容10611的一端与所述第一开关10612的一端和所述第二级前置放大电路102的第一nmos管1013的栅极连接,所述第一电容10611的另一端与所述第一级前置放大电路101的第二nmos管1014的漏极连接,所述第一开关10612的另一端接阈值电压vcom;所述第二电容10621的一端与所述第二开关10622的一端和所述第二级前置放大电路102的第二nmos管1014的栅极连接,所述第二电容10621的另一端与所述第一级前置放大电路101的第一nmos管1013的漏极连接,所述第二开关10622的另一端接阈值电压vcom。

24.参照图1,所述第三电容10631的一端与所述第三开关10632的一端和所述第三级前置放大电路103的第一nmos管1013的栅极连接,所述第三电容10631的另一端与所述第二级前置放大电路102的第二nmos管1014的漏极连接,所述第三开关10632的另一端接阈值电压vcom;所述第四电容10641的一端与所述第四开关10642的一端和所述第三级前置放大电路103的第二nmos管1014的栅极连接,所述第四电容10641的另一端与所述第二级前置放大电路102的第一nmos管1013的漏极连接,所述第四开关10642的另一端接阈值电压vcom。

25.参照图1,所述第五电容10651的一端与所述第五开关10652的一端和所述第四级前置放大电路104的第一nmos管1013的栅极连接,所述第五电容10651的另一端与所述第三级前置放大电路103的第二nmos管1014的漏极连接,所述第五开关10652的另一端接阈值电压vcom;所述第六电容10661的一端与所述第六开关10662的一端和所述第四级前置放大电路104的第二nmos管1014的栅极连接,所述第六电容10661的另一端与所述第三级前置放大电路103的第一nmos管1013的漏极连接,所述第六开关10662的另一端接阈值电压vcom。

26.参照图1,所述第七电容10671的一端与所述第七开关10672的一端和所述第五nmos管1055的栅极连接,所述第七电容10671的另一端与所述第四前置放大电路的第二nmos管1014的漏极连接,所述第七开关10672的另一端接阈值电压vcom;所述第八电容10681的一端与所述第八开关10682的一端和所述第六nmos管1056的栅极连接,所述第八电容10681的另一端与所述第四级前置放大电路104的第一nmos管1013的漏极连接,所述第八开关10682的另一端接阈值电压vcom。

27.参照图1,所述第一级前置放大电路101的第一输入端用于接收第一待比较数据vinp,所述第一级前置放大电路101的第二输入端用于接收第二待比较数据vinn,所述第一级前置放大电路101的第一输入端的输入误差为vos1,所述第一级前置放大电路101的增益为a1,所述第二级前置放大电路102的第一输入端的输入误差为vos2,所述第一级前置放大电路101的增益为a2,所述第三级前置放大电路103的第一输入端的输入误差为vos3,所述第一级前置放大电路101的增益为a3,所述第四级前置放大电路104的第一输入端的输入误差为vos4,所述第一级前置放大电路101的增益为a4,则总的误差vos=vos1+vos2/a1+vos3/a2/a1+vos4/a3/a2/a1。

28.图2为现有技术中开关的示意图。参照图1和图2,所述第一开关10612、所述第二开关10622、所述第三开关10632、所述第四开关10642、所述第五开关10652、所述第六开关10662、所述第七开关10672和所述第八开关10682的电路均与图2所示开关相同,所述开关为由pmos管和nmos管构成的传输门。当所述开关关断时,所述开关的pmos管的栅极接电源电压vdd,所述开关的nmos管的栅极接地vss;当所述开关导通时,所述开关的pmos管的栅极接地vss,所述开关的nmos管的栅极接电源电压vdd。

29.参照图1,所述第一级前置放大电路101、所述第二级前置放大电路102、所述第三级前置放大电路103和所述第四级前置放大电路104中均存在漏电效应,且前一级前置放大电路的漏电效应相较于后一级前置放大电路的漏电效应更明显。以所述第一级前置放大电路101为例,在比较阶段,所述第二级前置放大电路102的第一nmos管1013的栅极处为a点,所述第二级前置放大电路102的第二nmos管1014的栅极处为b点,a点的电压和b点的电压不同,这就导致a点对所述第一开关10612的衬底的漏电和b点的电压对所述第二开关10622的衬底的漏电不同,导致流经所述第一开关10612的电流i

leaka

与流经所述第二开关10622的电

流i

leakb

不同,进而导致所述第一电容10611一端的电极板的电荷流失速度与所述第二电容10621的一端的电极板的电荷流失速度不同,导致a点的电压变化速度δva与b点的电压变化速度δvb不同,这个现象相当于在a点和b点之间制造了一个误差电压v

offset

,并且温度越高,误差电压v

offset

,越大。

30.参照图1,以vinp=1.2v、vinn=1.199v、a1=a2=10为例,vinp-vinn=1mv,a点电压va=1.2v,b点电压vb=1.19v,va-vb=10mv,所述第一级前置放大电路101将1mv放大到10mv,此时正确的关系是va》vb。但由于存在漏电效应,δva=0.05v,δvb=0.02v,则实际的va=1.2-0.05=1.15v,实际的vb=1.19-0.02=1.17v,则此时会错误的判断为va《vb。

31.针对现有技术存在的问题,本发明的实施例提供了一种比较器,包括若干级前置放大电路、动态锁存比较电路以及误差消除电路,第一级所述前置放大电路的第一输入端和第二输入端分别用于接收待比较数据,后一级所述前置放大电路的第一输入端与前一级所述前置放大电路的第一输出端连接,后一级所述前置放大电路的第二输入端与前一级所述前置放大电路的第二输出端连接,所述动态锁存比较电路第一输入端与最后一级所述前置放大电路的第一输出端连接,所述动态锁存比较电路第二输入端与最后一级所述前置放大电路的第二输出端连接,所述误差消除电路与部分所述前置放大电路和所述动态锁存比较电路连接,以消除所述前置放大电路的输入误差和所述动态锁存比较电路的输入误差。

32.一些实施例中,若干级所述前置放大电路包括第一级前置放大电路、第二级前置放大电路、第三级前置放大电路、第四级前置放大电路,所述第一级前置放大电路的第一输入端和第二输入端分别用于接收待比较数据,所述第二级前置放大电路的第一输入端与所述第一级前置放大电路的第一输出端连接,所述第二级前置放大电路的第二输入端与所述第一级前置放大电路的第二输出端连接,所述第三级前置放大电路的第一输入端与所述第二级前置放大电路的第一输出端连接,所述第三级前置放大电路的第二输入端与所述第二级前置放大电路的第二输出端连接,所述第四级前置放大电路的第一输入端与所述第三级前置放大电路的第一输出端连接,所述第四级前置放大电路的第二输入端与所述第三级前置放大电路的第二输出端连接。

33.一些实施例中,所述误差消除电路与所述第三级前置放大电路、所述第四级前置放大电路和所述动态锁存比较电路连接。

34.一些实施例中,所述误差消除电路包括若干误差消除子电路,所述误差消除子电路包括电容和开关,所述电容的一端与所述开关的一端连接,所述开关的另一端接阈值电压。

35.图3为本发明一些实施例中比较器的电路示意图。参照图3,所述比较器包括第一级前置放大电路101、第二级前置放大电路102、第三级前置放大电路103、第四级前置放大电路104、动态锁存比较电路105和误差消除电路。

36.参照图3,所述第一级前置放大电路101、所述第二级前置放大电路102、所述第三级前置放大电路103和所述第四级前置放大电路104均包括第一电阻1011、第二电阻1012、第一nmos管1013、第二nmos管1014和第一电流源1015,所述第一电阻1011的一端和所述第二电阻1012的一端均接电源电压,所述第一电阻1011的另一端与所述第一nmos管1013的漏极连接,所述第二电阻1012的另一端与所述第二nmos管1014的漏极连接,所述第一nmos管1013的源极和所述第二nmos管1014的源极与所述第一电流源1015的正极连接,所述第一电

流源1015的负极接地,所述第一nmos管1013的栅极为第一输入端,所述第二nmos管1014的栅极为第二输入端。其中,所述待比较数据包括第一待比较数据和第二待比较数据,所述第一级前置放大电路101的第一nmos管1013的栅极接第一待比较数据,所述第一级前置放大电路101的第二nmos管1014的栅极接第二待比较数据。

37.参照图3,所述第一级前置放大电路101和所述第二级前置放大电路102中第一nmos管1013的尺寸和第二nmos管1014的尺寸大于所述第三级前置放大电路103和所述第四级前置放大电路104中第一nmos管1013的尺寸和第二nmos管1014的尺寸。

38.参照图3,所述动态锁存比较电路105包括第一pmos管1051、第二pmos管1052、第三nmos管1053、第四nmos管1054、第五nmos管1055、第六nmos管1056和第二电流源1057,所述第一pmos管1051的源极和所述第二pmos管1052的源极均接电源电压,所述第一pmos管1051的漏极与所述第三nmos管1053的漏极、所述第二pmos管1052的栅极和所述第四nmos管1054的栅极连接,所述第二pmos管1052的漏极与所述第四nmos管1054的漏极、所述第一pmos管1051的栅极和所述第三nmos管1053的栅极连接,所述第三nmos管1053的源极与所述第五nmos管1055的漏极连接,作为所述动态锁存比较电路105的第一输出端,所述第四nmos管1054的源极与所述第六nmos管1056的漏极连接,作为所述动态锁存比较电路105的第二输出端,所述第五nmos管1055的源极和所述第六nmos管1056的源极均与所述第二电流源1057的正极连接,所述第二电流源1057的负极接地,所述第五nmos管1055的栅极为所述动态锁存比较电路105的第一输入端,所述第六nmos管1056的栅极为所述动态锁存比较电路105的第二输入端。

39.参照图3,所述误差消除电路包括六个误差消除子电路,六个所述误差消除子电路分别为第三误差消除子电路1063、第四误差消除子电路1064、第五误差消除子电路1065、第六误差消除子电路1066、第七误差消除子电路1067和第八误差消除子电路1068,所述第三误差消除子电路1063包括第三电容10631和第三开关10632,所述第四误差消除子电路1064包括第四电容10641和第四开关10642,所述第五误差消除子电路1065包括第五电容10651和第五开关10652,所述第六误差消除子电路1066包括第六电容10661和第六开关10662,所述第七误差消除子电路1067包括第七电容10671和第七开关10672,所述第八误差消除子电路1068包括第八电容10681和第八开关10682。

40.参照图3,所述第三电容10631的一端与所述第三开关10632的一端和所述第三级前置放大电路103的第一nmos管1013的栅极连接,所述第三电容10631的另一端与所述第二级前置放大电路102的第二nmos管1014的漏极连接,所述第三开关10632的另一端接阈值电压vcom;所述第四电容10641的一端与所述第四开关10642的一端和所述第三级前置放大电路103的第二nmos管1014的栅极连接,所述第四电容10641的另一端与所述第二级前置放大电路102的第一nmos管1013的漏极连接,所述第四开关10642的另一端接阈值电压vcom。

41.参照图3,所述第五电容10651的一端与所述第五开关10652的一端和所述第四级前置放大电路104的第一nmos管1013的栅极连接,所述第五电容10651的另一端与所述第三级前置放大电路103的第二nmos管1014的漏极连接,所述第五开关10652的另一端接阈值电压vcom;所述第六电容10661的一端与所述第六开关10662的一端和所述第四级前置放大电路104的第二nmos管1014的栅极连接,所述第六电容10661的另一端与所述第三级前置放大电路103的第一nmos管1013的漏极连接,所述第六开关10662的另一端接阈值电压vcom。

42.参照图3,所述第七电容10671的一端与所述第七开关10672的一端和所述第五nmos管1055的栅极连接,所述第七电容10671的另一端与所述第四前置放大电路的第二nmos管1014的漏极连接,所述第七开关10672的另一端接阈值电压vcom;所述第八电容10681的一端与所述第八开关10682的一端和所述第六nmos管1056的栅极连接,所述第八电容10681的另一端与所述第四级前置放大电路104的第一nmos管1013的漏极连接,所述第八开关10682的另一端接阈值电压vcom。

43.参照图3,所述第二级前置放大电路102的第一nmos管1013的栅极处为a点,所述第二级前置放大电路102的第二nmos管1014的栅极处为b点,所述第三级前置放大电路103的第一nmos管1013的栅极处为c点,所述第三级前置放大电路103的第二nmos管1014的栅极处为d点。

44.参照图3,以vinp=1.2v、vinn=1.199v、a1=a2=10为例,vinp-vinn=1mv,a点电压va=1.2v,b点电压vb=1.19v,va-vb=10mv,c点电压vc=1.2v,d点电压vd=1.1v,vc-vd=100mv,c点的电压变化速度δvc=0.05v,d点的电压变化速度δvd=0.02v,则实际的vc=1.2-0.05=1.15v,实际的vd=1.1-0.02=1.08v,则最终的判断结果为vc》vd,判断能正确。而后续的漏电效应影响更小,则判断结果必然正确,因此,成功消除了误差。

45.本发明还提供了一种数据转换器,包括比较器。具体地,所述数据转换器为逐次逼近型模数转换器。

46.虽然在上文中详细说明了本发明的实施方式,但是对于本领域的技术人员来说显而易见的是,能够对这些实施方式进行各种修改和变化。但是,应理解,这种修改和变化都属于权利要求书中所述的本发明的范围和精神之内。而且,在此说明的本发明可有其它的实施方式,并且可通过多种方式实施或实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1