存储单元、存储块以及存储器的制作方法

本技术涉及半导体器件的,尤其涉及一种存储单元、存储块以及存储器。

背景技术:

1、二维(twodimensional,2d)存储块在电子装置中普遍存在,并且可包括例如或非(nor)闪速存储阵列、与非(nand)闪速存储阵列、动态随机存取存储器(dynamic random-access memory,dram)阵列等。然而,2d存储阵列已经接近缩放极限,存储密度无法进一步提高。

技术实现思路

1、本技术提供的一种存储单元及存储块,旨在解决现有2d存储阵列已经接近缩放极限,存储密度无法进一步提高的问题。

2、本技术一方面提供一种存储块。该存储块包括存储阵列,存储阵列包括多个堆叠条状结构和多个半导体结构对,多个堆叠条状结构沿列方向间隔分布,每个堆叠条状结构沿行方向延伸,且包括沿高度方向交替层叠的绝缘条和导电条;其中,每两个相邻的堆叠条状结构之间设置若干半导体结构对,两个相邻的堆叠条状结构及设置于其之间的若干半导体结构对参与形成一行存储子阵列,两个相邻的堆叠条状结构中的导电条作为该行存储子阵列的控制栅;每行存储子阵列包括沿行方向分布的多个存储单元组,每个存储单元组包括一对应的半导体结构对以及一基底电极结构,半导体结构对包括在列方向上并排间隔设置的两个半导体结构,基底电极结构设置在两个半导体结构之间,半导体结构和基底电极结构分别沿高度方向延伸。

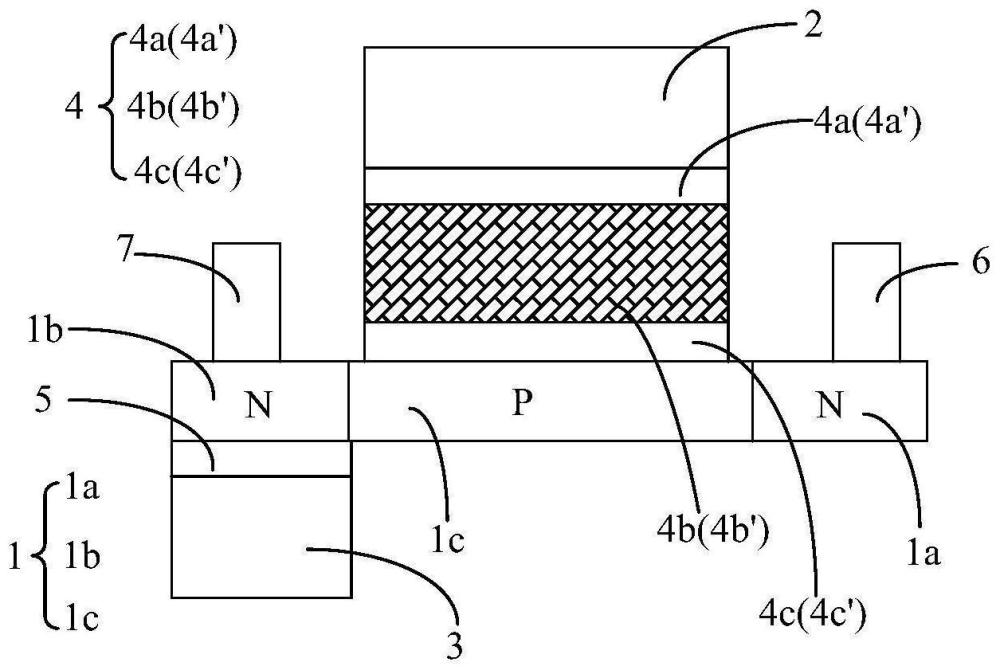

3、进一步地,每个半导体结构包括源区半导体结构、漏区半导体结构以及设置在源区半导体结构与漏区半导体结构之间的沟道半导体结构,源区半导体结构、漏区半导体结构以及沟道半导体结构分别沿高度方向延伸。

4、进一步地,每个存储单元组中,两个半导体结构的源区半导体结构在列方向上并排间隔设置,两个半导体结构的漏区半导体结构在列方向上并排间隔设置,每个半导体结构的漏区半导体结构与基底电极结构在垂直于列方向的平面上的投影重合。

5、进一步地,每个存储单元组中,在垂直于高度方向的平面上,两个半导体结构的沟道半导体结构的横截面分别呈弧状设置,且朝向远离彼此的方向弯曲。

6、进一步地,每个存储单元组对应的两个堆叠条状结构中,每个导电条作为该存储单元组的控制栅,用于构成一个存储单元,每个存储单元匹配对应的导电条的至少部分、基底电极结构的至少部分、以及对应的半导体结构中的沟道半导体结构、源区半导体结构以及漏区半导体结构的至少部分;在列方向上,每个存储单元组第一侧的堆叠条状结构作为与该存储单元组对应的第一堆叠条状结构,每个存储单元组第二侧的堆叠条状结构作为与该存储单元组对应的第二堆叠条状结构,第一侧和第二侧相对;第一堆叠条状结构中的每个导电条作为该存储单元组的第一控制栅,用于构成一个第一存储单元;第二堆叠条状结构中的每个导电条作为该存储单元组的第二控制栅,用于构成一个第二存储单元。

7、进一步地,非边缘处的每个堆叠条状结构对应两行存储子阵列,非边缘处的每个堆叠条状结构中的每个导电条作为对应的一行存储子阵列中的每个存储单元组的控制栅,用于构成一个第一存储单元,并作为对应的另一行存储子阵列中的每个存储单元组的第二控制栅,用于构成一个第二存储单元;每个堆叠条状结构中的每个导电条作为一条字线。

8、进一步地,每个存储单元组对应两个堆叠条状结构;每个存储单元组还包括两个存储结构,每个存储结构设置在对应的一个半导体结构与对应的一个堆叠条状结构之间。

9、进一步地,存储结构为电荷能陷存储结构,且沿高度方向延伸;存储结构包括第一介质结构、电荷存储结构和第二介质结构,第一介质结构设置在电荷存储结构与对应的一个堆叠条状结构之间,电荷存储结构设置在第一介质结构与第二介质结构之间,第二介质结构设置在电荷存储结构与对应的一个半导体结构之间。

10、进一步地,存储结构包括沿高度方向分布的多个浮栅存储结构,每个浮栅存储结构参与形成一个存储单元;浮栅存储结构包括浮栅结构和包裹浮栅结构的介质层,每个存储单元中,浮栅存储结构设置在对应的一个导电条与对应的一个半导体结构之间,且浮栅结构的任意表面均被介质层覆盖。

11、进一步地,每个存储单元组进一步包括沿高度方向延伸的源极结构和漏极结构;其中,源极结构分别与两个半导体结构的源区半导体结构连接,漏极结构分别与两个半导体结构的漏区半导体结构连接。

12、进一步地,每个存储单元组对应两个堆叠条状结构;对于每个存储单元组,源极结构与对应的两个堆叠条状结构之间通过绝缘介质间隔,漏极结构与对应的两个堆叠条状结构之间通过绝缘介质间隔。

13、进一步地,每个存储单元组中,源极结构、漏极结构以及两个半导体结构所围设形成的区域内设置有第一绝缘结构;基底电极结构设置于源极结构、漏极结构以及半导体结构所围设形成的区域内,基底电极结构与源极结构、漏极结构以及半导体结构之间通过第一绝缘结构间隔设置。

14、进一步地,在行方向上,每个存储单元组中的源极结构/漏极结构与相邻的另一存储单元组中的源极结构/漏极结构之间,设置有第二绝缘结构;或者在行方向上,两个相邻的存储单元组包括漏极结构、两个半导体结构、源极结构、两个半导体结构以及漏极结构,以共享同一源极结构,且相邻两个存储单元组中的漏极结构与相邻的另一相邻两个存储单元组中的漏极结构之间,设置有第二绝缘结构。

15、进一步地,相邻两行存储子阵列中的存储单元组彼此对齐或者彼此错位。

16、本技术通过设置存储阵列包括多个堆叠条状结构和多个半导体结构对,多个堆叠条状结构沿列方向间隔分布,每个堆叠条状结构沿行方向延伸,且包括沿高度方向交替层叠的绝缘条和导电条,其中,每两个相邻的堆叠条状结构之间设置若干半导体结构对,两个相邻的堆叠条状结构及设置于其之间的若干半导体结构对参与形成一行存储子阵列,两个相邻的堆叠条状结构中的导电条作为该行存储子阵列的控制栅,每行存储子阵列包括沿行方向分布的多个存储单元组,每个存储单元组包括一对应的半导体结构对以及一基底电极结构,半导体结构对包括在列方向上并排间隔设置的两个半导体结构,基底电极结构设置在两个半导体结构之间,半导体结构和基底电极结构分别沿高度方向延伸,提供了一种三维堆叠的结构,有利于提高存储块的存储密度。

17、本技术另一方面提供一种存储单元。该存储单元包括半导体组件、控制栅以及至少一个基底电极。其中,半导体组件包括源区半导体、漏区半导体以及沟道半导体,沟道半导体设置在源区半导体和漏区半导体之间,并与源区半导体和漏区半导体并排设置。控制栅对应于沟道半导体设置于半导体组件的一侧。至少一个基底电极对应于源区半导体和漏区半导体中的至少一个且电连接对应的源区半导体和/或漏区半导体的另一侧,用于被施加基底电压。

18、进一步地,控制栅与半导体组件之间设置有存储组件;基底电极与源区半导体和/或漏区半导体之间设置有中间介质层。

19、进一步地,存储组件为电荷能陷存储组件,电荷能陷存储组件包括第一介质层、电荷存储层和第二介质层,第一介质层设置在电荷存储层与控制栅之间,电荷存储层设置于第一介质层和第二介质层之间,第二介质层设置于电荷存储层与半导体组件之间;或存储组件为浮栅存储组件,浮栅存储组件包括第一介质层、浮栅和第二介质层,第一介质层设置在浮栅与控制栅之间,浮栅设置于第一介质层和第二介质层之间,第二介质层设置于浮栅与半导体组件之间。

20、进一步地,源区半导体、漏区半导体以及沟道半导体分别为单晶硅半导体或者多晶硅半导体。

21、进一步地,基底电极与漏区半导体的另一侧电连接,存储单元进一步包括与漏区半导体的一侧电连接的漏极;存储单元经由控制栅接收字线电压,经由漏极接收位线电压,经由基底电极接收基底电压,以执行擦除操作,其中,基底电压低于位线电压,且高于字线电压。

22、进一步地,在执行擦除操作时,基于基底电压,漏区半导体的靠近基底电极的至少一部分被反型,以与漏区半导体的远离基底电极的至少另一部分之间形成pn结。

23、相关技术中,通常是在衬底/阱区上掺杂形成源区和漏区,难以实现三维堆叠,而本技术通过源区半导体、漏区半导体以及沟道半导体并排设置,控制栅对应于沟道半导体设置于半导体组件的一侧,至少一个基底电极对应于源区半导体和漏区半导体中的至少一个且电连接对应的源区半导体和/或漏区半导体的另一侧,用于被施加基底电压,提供了一种四端/五端的存储单元,相比于相关技术有利于降低三维堆叠的难度,进而提高存储密度。

24、本技术又一方面提供一种存储器。该存储器,包括存储单元组和绝缘介质层。其中,存储单元组包括源极端、漏极端、在高度方向上与源极端连接的源极连接柱、以及在高度方向上与漏极端连接的漏极连接柱;以及绝缘介质层设置于存储单元组在高度方向上的一侧,绝缘介质层中设置有漏极控制条,漏极连接柱和源极连接柱穿设于绝缘介质层和漏极控制条,漏极连接柱与漏极控制条之间以及源极连接柱与漏极控制条之间设置有绝缘介质层中的绝缘介质;其中,在垂直于高度方向的方向上,漏极连接柱与漏极控制条之间的绝缘介质的厚度小于源极连接柱与漏极控制条之间的绝缘介质的厚度。

25、进一步地,漏极连接柱为空心柱状结构,其内部设置有绝缘介质。

26、本技术通过设置存储单元组的源极连接柱和漏极连接柱穿设于绝缘介质层和漏极控制条,漏极连接柱与对应的漏极控制条之间以及源极连接柱与对应的漏极控制条之间设置有绝缘介质层中的绝缘介质,漏极连接柱与对应的漏极控制条之间的绝缘介质的厚度小于源极连接柱与对应的漏极控制条之间的绝缘介质的厚度,使得能够根据实际需要控制存储单元组中的漏极连接柱的导通状态。

- 还没有人留言评论。精彩留言会获得点赞!