有源匹配结合无源匹配的6-18GHz功率放大器及实现方法与流程

有源匹配结合无源匹配的6-18ghz功率放大器及实现方法

技术领域

1.本发明涉及微波功率放大器,尤其涉及一种有源匹配结合无源匹配的6-18ghz功率放大器及实现方法。

背景技术:

2.功率放大器是收发链路的主要耗能元件,提高功率放大器的效率可以有效降低收发链路功耗。根据集成化和小型化的需求,一般要求功率放大器不是工作在某一频率点而是工作在宽带范围。如何在宽带,尤其是超宽带范围内,实现更大的输出功率和更高的增益,同时保证尽可能高的效率,一直是学术界和工业界研究的热点问题。

3.传统的超宽带功率放大器,无论是分布式电路拓扑还是电抗匹配式电路拓扑,均为固定的无源匹配电路结构。根据foster电抗定理可知,在史密斯圆图中,常规的无源匹配电路匹配位置随频率顺时针旋转。但是根据load-pull测试结果可知,晶体管的最佳阻抗点随频率逆时针旋转。因此现有的超宽带功率放大器晶体管阻抗无法在所有频率点均被理想匹配,进而限制了超宽带功率放大器的效率。

技术实现要素:

4.发明目的:本发明公开了一种能使晶体管阻抗在所有频率点均被理想匹配,提高功率放大器的效率的有源匹配结合无源匹配的6-18ghz功率放大器及实现方法。

5.技术方案:本发明的功率放大器,包括无源输入匹配网络、有源输入匹配网络、无源级间匹配网络、有源级间匹配网络、无源输出匹配网络、有源输出匹配网络、第一晶体管、第二晶体管;

6.所述无源输入匹配网络的输入端与射频输入端连接,所述有源输入匹配网络的输入端与无源输入匹配网络的输出端连接;所述第一晶体管的栅极与有源输入匹配网络的输出端连接;所述第一晶体管的源极接地;

7.所述无源级间匹配网络的输入端与第一晶体管的漏极连接;所述有源级间匹配网络的输入端与无源级间匹配网络的输出端连接;所述第二晶体管的栅极与有源级间匹配网络的输出端连接;所述第二晶体管的源极接地;

8.所述无源输出匹配网络的输入端与第二晶体管的漏极连接;所述有源输出匹配网络的输入端与无源输出匹配网络的输出端连接;射频输出端与有源输出匹配网络的输出端连接;

9.所述有源输入匹配网络的控制信号为第一控制信号;所述有源级间匹配网络的控制信号为第二控制信号;所述有源输出匹配网络的控制信号为第三控制信号;

10.射频输入端的输入信号为输入信号源;所述第一控制信号、第二控制信号、第三控制信号均为第一信号源、第二信号源、

……

、第n信号源输出信号的组合;所述n为正整数且n≥3;

11.输入信号源的输出信号频率为f0;第一信号源输出信号频率为f0;第二信号源输出

信号频率为2f0;

……

;第n信号源输出信号频率为nf0。

12.进一步,所述无源输入匹配网络包括第一电阻、第二电阻、第三电阻、第四电阻、第一微带线、第二微带线、第三微带线、第四微带线、第一电容、第二电容、第三电容;第一电阻的一端与射频输入端连接;第一电阻的另一端分别与第二电阻和第三电阻的一端连接;第三电阻的另一端与第一微带线的一端连接;第一微带线的另一端接地;第二电阻的另一端与第一电容的一端连接;第一电容的另一端分别与第二电容和第二微带线的一端连接;第二电容的另一端接地;第二微带线的另一端分别与第三微带线和第四电阻的一端连接;第三微带线的另一端与有源输入匹配网络中第五微带线的一端连接;第四电阻的另一端与第四微带线的一端连接;第四微带线的另一端分别与栅极偏置电压和第三电容的一端连接;第三电容的另一端接地;

13.所述有源输入匹配网络包括第五微带线、第六微带线和第七微带线,第五微带线的一端与无源输入匹配网络中第三微带线的一端连接;第五微带线的另一端分别与第六微带线和第七微带线的一端连接;第六微带线的另一端与第一晶体管的栅极连接;第七微带线的另一端与第一控制信号连接。

14.进一步,所述无源级间匹配网络包括第八微带线、第九微带线、第十微带线、第十一微带线、第十二微带线、第十三微带线、第四电容、第五电容、第六电容、第七电容、第八电容、第九电容、第五电阻和第六电阻;第八微带线的一端与第一晶体管的漏极连接;第八微带线的另一端分别与第九微带线和第十微带线的一端连接;第九微带线的另一端分别与漏极偏置电压和第四电容的一端连接;第四电容的另一端接地;第十微带线的另一端与第五电容的一端连接;第五电容的另一端分别与第六电容、第七电容、第五电阻的一端连接;第六电容的另一端接地;第七电容的另一端和第五电阻的另一端连接并分别与第八电容和第十一微带线的一端连接;第八电容的另一端接地;第十一微带线的另一端分别与第十二微带线和第六电阻的一端连接;第十二微带线的另一端与有源级间匹配网络中第十四微带线的一端连接;第六电阻的另一端与第十三微带线的一端连接;第十三微带线的另一端分别与栅极偏置电压和第九电容的一端连接;第九电容的另一端接地;

15.所述有源级间匹配网络包括第十四微带线、第十五微带线和第十六微带线,第十四微带线的一端与无源输入匹配网络中的第十二微带线的一端连接;第十四微带线的另一端分别与第十五微带线和第十六微带线的一端连接;第十五微带线的另一端与第二晶体管的栅极连接;第十六微带线的另一端与第二控制信号连接。

16.进一步,所述无源输出匹配网络包括第十七微带线、第十八微带线、第十九微带线、第二十微带线、第二十一微带线、第十电容、第十一电容、第十二电容、第十三电容和第十四电容;第十七微带线的一端与第二晶体管的漏极连接;第十七微带线的另一端分别与第十八微带线和第十九微带线的一端连接;第十八微带线的另一端分别与漏极偏置电压和第十电容的一端连接;第十电容的另一端接地;第十九微带线的另一端分别与第十一电容和第十二电容的一端连接;第十一电容的另一端接地;第十二电容的另一端分别与第二十微带线和第二十一微带线的一端连接;第二十微带线的另一端接地;第二十一微带线的另一端分别与第十三电容和第十四电容的一端连接;第十三电容的另一端接地;第十四电容的另一端与有源输出匹配网络中的第二十二微带线的一端连接;

17.所述有源输出匹配网络包括第二十二微带线、第二十三微带线和第二十四微带

线,第二十二微带线的一端与无源输出匹配网络中第十四电容的一端连接;第二十二微带线的另一端分别与第二十三微带线和第二十四微带线的一端连接;第二十三微带线的另一端与射频输出端连接;第二十四微带线的另一端与第三控制信号连接。

18.一种有源匹配结合无源匹配的6-18ghz功率放大器的实现方法,采用有源匹配和无源匹配相结合的方式对第一晶体管和第二晶体管的阻抗位置进行精确控制:首先通过无源匹配电路对两晶体管阻抗位置初步匹配,降低匹配难度;再通过有源匹配对阻抗位置进一步修正,包括基波阻抗位置修正和谐波阻抗位置修正。包括以下步骤:

19.a1:根据要求的工作频率范围,选择工艺途径;根据要求的输出功率,结合所选工艺途径的功率密度,选择功率放大器的末级总栅宽;根据要求的增益,确定功率放大器的级数;根据所选工艺途径器件的增益压缩特性,确定级间驱动比;

20.a2:通过load pull和source pull测试或仿真,确定第一晶体管(phemt1)的第一基波负载阻抗、第一二次谐波负载阻抗、第一三次谐波负载阻抗、第一基波源阻抗、第一二次谐波源阻抗和第一三次谐波源阻抗,确定第二晶体管的第二基波负载阻抗、第二二次谐波负载阻抗、第二三次谐波负载阻抗、第二基波源阻抗、第二二次谐波源阻抗和第二三次谐波源阻抗;

21.a3:在保证无源输出匹配网络插入损耗较小的前提下,将第二晶体管(phemt2)的基波负载阻抗匹配至输出负载阻抗附近圆形区域;

22.a4:在保证无源级间匹配网络插入损耗较小的前提下,将第一晶体管的第一基波负载阻抗匹配至第二晶体管的第二基波源阻抗附近圆形区域;

23.a5:在保证无源输入匹配网络插入损耗较小的前提下,将第一晶体管的第一基波源阻抗z1_s1匹配至输入负载阻抗附近圆形区域;

24.a6:在步骤a3基础上,通过第三控制信号注入有源输出匹配网络,将第二晶体管的第二基波负载阻抗从输出负载阻抗附近圆形区域严格匹配至的输出负载阻抗点;

25.a7:在步骤a4基础上,通过第二控制信号注入有源级间匹配网络,将第一晶体管的第一基波负载阻抗从第二晶体管的第二基波源阻抗附近圆形区域严格匹配至第二晶体管的第二基波源阻抗;

26.a8:在步骤a5基础上,通过第一控制信号注入有源输入匹配网络,将第一晶体管的第一基波源阻抗从输入负载阻抗附近圆形区域严格匹配至输入负载阻抗点;

27.a9:根据步骤a

3-步骤a8所设计的匹配网络,完成原理图和版图的整合优化。

28.进一步,步骤a6中,通过第三控制信号注入有源输出匹配网络,使第二晶体管的第二二次谐波负载阻抗、第二三次谐波负载阻抗分别处于短路点或者开路点。

29.进一步,步骤a7中,通过第二控制信号注入有源级间匹配网络,使第一晶体管的第一二次谐波负载阻抗、第一三次谐波负载阻抗和第二晶体管的第二二次谐波源阻抗、第二三次谐波源阻抗分别处于短路点或者开路点。

30.进一步,步骤a8中,通过第一控制信号注入有源输入匹配网络,使第一晶体管的第一二次谐波源阻抗、第一三次谐波源阻抗分别处于短路点或者开路点。

31.本发明与现有技术相比,其显著效果如下:

32.1、本发明采用有源匹配结合无源匹配的方式对第一晶体管和第二晶体管的阻抗位置精确控制,首先通过无源匹配对晶体管阻抗位置初步匹配,降低匹配难度,在此基础上

通过有源匹配对阻抗位置进一步修正,包括基波阻抗位置修正和谐波阻抗位置修正,实现阻抗位置精确控制,最终提高功率放大器整体效率。本发明打破了foster电抗定理对电路设计的约束,解决了传统的超宽带功率放大器中晶体管阻抗无法在所有频率点均被理想匹配的难题,避免了功率放大器中带宽、输出功率和效率之间折中的选择,提高了功率放大器的效率;

33.2、本发明具有有源输入匹配网络、有源级间匹配网络、有源输出匹配网络多个有源匹配网络,同时各级有源匹配网络分别具有独立的第一控制信号、第二控制信号、第三控制信号,可以根据无源输入匹配网络、无源级间匹配网络、无源输出匹配网络对第一晶体管phemt1和第二晶体管phemt2初步阻抗匹配情况,灵活调整控制信号,丰富了设计的灵活性;

34.3、本发明的第一控制信号、第二控制信号、第三控制信号均为第一信号源、第二信号源、

……

、第三信号源输出信号的组合,不仅可以实现对第一晶体管和第二晶体管的基波负载阻抗和基波源阻抗匹配,同时还可以实现谐波负载阻抗和谐波源阻抗匹配,使得二次谐波负载阻抗、三次谐波负载阻抗、二次谐波源阻抗、三次谐波源阻抗处于开路点或者短路点。

附图说明

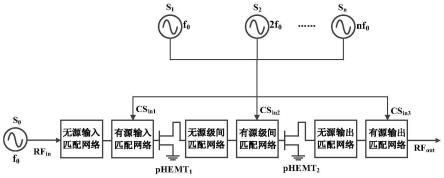

35.图1为本发明整体结构框图;

36.图2为本发明实施例中输入匹配网络原理图;

37.图3为本发明实施例中级间匹配网络原理图;

38.图4为本发明实施例中输出匹配网络原理图;

39.图5为本发明的实现方法流程图;

40.图6为本发明无源匹配和有源匹配效果图;

41.图7为无源匹配网络初步阻抗匹配时效率与有源匹配网络进一步阻抗修正后效率的对比图。

具体实施方式

42.下面结合说明书附图和具体实施方式对本发明做进一步详细描述。

43.本发明整体结构如图1所示,包括无源输入匹配网络、有源输入匹配网络、无源级间匹配网络、有源级间匹配网络、无源输出匹配网络、有源输出匹配网络、第一晶体管phemt1、第二晶体管phemt2。

44.无源输入匹配网络的输入端与射频输入rf

in

连接;有源输入匹配网络的输入端与无源输入匹配网络的输出端连接;第一晶体管phemt1的栅极与有源输入匹配网络的输出端连接;第一晶体管phemt1的源极接地;用于提供良好的输入驻波和功率增益平坦度。

45.无源级间匹配网络的输入端与第一晶体管phemt1的漏极连接;有源级间匹配网络的输入端与无源级间匹配网络的输出端连接;第二晶体管phemt2的栅极与有源级间匹配网络的输出端连接;第二晶体管phemt2的源极接地;第一晶体管phemt1、第二晶体管phemt2对射频输入端rf

in

多级放大,用于提供足够的功率增益。

46.无源输出匹配网络的输入端与第二晶体管phemt2的漏极连接;有源输出匹配网络的输入端与无源输出匹配网络的输出端连接;射频输出端rf

out

与有源输出匹配网络的输出

端连接;用以提供良好的输出功率和效率。

47.有源输入匹配网络的控制信号为第一控制信号cs

in1

;所述有源级间匹配网络的控制信号为第二控制信号cs

in2

;所述有源输出匹配网络的控制信号为第三控制信号cs

in3

。

48.射频输入端rf

in

的输入信号为输入信号源s0;所述第一控制信号cs

in1

、第二控制信号cs

in2

、第三控制信号cs

in3

均为第一信号源s1、第二信号源s2、

……

、第n信号源sn输出信号的组合;所述n为正整数且n≥3。

49.输入信号源s0输出信号频率为f0;第一信号源s1输出信号频率为f0;第二信号源s2输出信号频率为2f0;

……

;第n信号源sn输出信号频率为nf0。

50.本发明各级匹配网络具体涉及如下:

51.本实施例中,输入匹配网络原理图如图2所示。无源输入匹配网络包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一微带线tl1、第二微带线tl2、第三微带线tl3、第四微带线tl4、第一电容c1、第二电容c2、第三电容c3。第一电阻r1的一端与射频输入rf

in

连接;第一电阻r1的另一端分别与第二电阻r2和第三电阻r3的一端连接;第三电阻r3的另一端与第一微带线tl1的一端连接;第一微带线tl1的另一端接地;第二电阻r2的另一端与第一电容c1的一端连接;第一电容c1的另一端分别与第二电容c2和第二微带线tl2的一端连接;第二电容c2的另一端接地;第二微带线tl2的另一端分别与第三微带线tl3和第四电阻r4的一端连接;第三微带线tl3的另一端与有源输入匹配网络中第五微带线tl5的一端连接;第四电阻r4的另一端与第四微带线tl4的一端连接;第四微带线tl4的另一端分别与栅极偏置电压v

g1

和第三电容c3的一端连接;第三电容c3的另一端接地。有源输入匹配网络包括第五微带线tl5、第六微带线tl6和第七微带线tl7。第五微带线tl5的一端与无源输入匹配网络中第三微带线tl3的一端连接;第五微带线tl5的另一端分别与第六微带线tl6和第七微带线tl7的一端连接;第六微带线tl6的另一端与第一晶体管phemt1的栅极连接;第七微带线tl7的另一端与第一控制信号cs

in1

连接。

52.本发明实施例中的级间匹配网络原理图如图3所示。无源级间匹配网络包括第八微带线tl8、第九微带线tl9、第十微带线tl

10

、第十一微带线tl

11

、第十二微带线tl

12

、第十三微带线tl

13

、第四电容c4、第五电容c5、第六电容c6、第七电容c7、第八电容c8、第九电容c9、第五电阻r5和第六电阻r6。第八微带线tl8的一端与第一晶体管phemt1的漏极连接;第八微带线tl8的另一端分别与第九微带线tl9和第十微带线tl

10

的一端连接;第九微带线tl9的另一端分别与漏极偏置电压v

d1

和第四电容c4的一端连接;第四电容c4的另一端接地;第十微带线tl

10

的另一端与第五电容c5的一端连接;第五电容c5的另一端分别与第六电容c6、第七电容c7、第五电阻r5的一端连接;第六电容c6的另一端接地;第七电容c7的另一端和第五电阻r5的另一端连接并分别与第八电容c8和第十一微带线tl

11

的一端连接;第八电容c8的另一端接地;第十一微带线tl

11

的另一端分别与第十二微带线tl

12

和第六电阻r6的一端连接;第十二微带线tl

12

的另一端与有源级间匹配网络中第十四微带线tl

14

的一端连接;第六电阻r6的另一端与第十三微带线tl

13

的一端连接;第十三微带线tl

13

的另一端分别与栅极偏置电压v

g2

和第九电容c9的一端连接;第九电容c9的另一端接地。有源级间匹配网络包括第十四微带线tl

14

、第十五微带线tl

15

、第十六微带线tl

16

。第十四微带线tl

14

的一端与无源输入匹配网络中的第十二微带线tl

12

的一端连接;第十四微带线tl

14

的另一端分别与第十五微带线tl

15

和第十六微带线tl

16

的一端连接;第十五微带线tl

15

的另一端与第二晶体管phemt2的栅

极连接;第十六微带线tl

16

的另一端与第二控制信号cs

in2

连接。

53.本发明实施例中的输出匹配网络原理图如图4所示。无源输出匹配网络包括第十七微带线tl

17

、第十八微带线tl

18

、第十九微带线tl

19

、第二十微带线tl

20

、第二十一微带线tl

21

、第十电容c

10

、第十一电容c

11

、第十二电容c

12

、第十三电容c

13

、第十四电容c

14

。第十七微带线tl

17

的一端与第二晶体管phemt2的漏极连接;第十七微带线tl

17

的另一端分别与第十八微带线tl

18

和第十九微带线tl

19

的一端连接;第十八微带线tl

18

的另一端分别与漏极偏置电压v

d2

和第十电容c

10

的一端连接;第十电容c

10

的另一端接地;第十九微带线tl

19

的另一端分别与第十一电容c

11

和第十二电容c

12

的一端连接;第十一电容c

11

的另一端接地;第十二电容c

12

的另一端分别与第二十微带线tl

20

和第二十一微带线tl

21

的一端连接;第二十微带线tl

20

的另一端接地;第二十一微带线tl

21

的另一端分别与第十三电容c

13

和第十四电容c

14

的一端连接;第十三电容c

13

的另一端接地;第十四电容c

14

的另一端与有源输出匹配网络中的第二十二微带线tl

22

的一端连接。有源输出匹配网络包括第二十二微带线tl

22

、第二十三微带线tl

23

和第二十四微带线tl

24

。第二十二微带线tl

22

的一端与无源输出匹配网络中第十四电容c

14

的一端连接;第二十二微带线tl

22

的另一端分别与第二十三微带线tl

23

和第二十四微带线tl

24

的一端连接;第二十三微带线tl

23

的另一端与射频输出rf

out

连接;第二十四微带线tl

24

的另一端与第三控制信号cs

in3

连接。

54.本发明的实现方法流程图如图5所示,包括以下步骤:

55.步骤a1,根据要求的工作频率范围,选择工艺途径;根据要求的输出功率,结合所选工艺途径的功率密度,选择功率放大器的末级总栅宽;根据要求的增益,确定功率放大器的级数;根据所选工艺途径器件的增益压缩特性,确定级间驱动比。

56.步骤a2,为了更方便的描述后续步骤,以具有第一晶体管phemt1和第二晶体管phemt2的两级放大形式为例进行说明,需要注意的是所描述的实现方法对于多级放大形式仍适用。通过load pull和source pull测试或仿真确定第一晶体管phemt1的第一基波负载阻抗,第一二次谐波负载阻抗,第一三次谐波负载阻抗,第一基波源阻抗,第一二次谐波源阻抗,第一三次谐波源阻抗;确定第二晶体管phemt2的第二基波负载阻抗,第二二次谐波负载阻抗,第二三次谐波负载阻抗,第二基波源阻抗,第二二次谐波源阻抗,第二三次谐波源阻抗。

57.步骤a3,在保证无源输出匹配网络插入损耗较小的前提下,将第二晶体管phemt2的第二基波负载阻抗匹配至输出负载阻抗(一般为50ω)附近圆形区域,即第二对晶体管phemt2的第二基波负载阻抗进行初步阻抗匹配。

58.步骤a4,在保证无源级间匹配网络插入损耗较小的前提下,将第一晶体管phemt1的第一基波负载阻抗匹配至第二晶体管phemt2的第二基波源阻抗附近圆形区域,即对第一晶体管phemt1的第一基波负载阻抗和第二晶体管phemt2的第二基波源阻抗进行初步阻抗匹配。

59.步骤a5,在保证无源输入匹配网络插入损耗较小的前提下,将晶体管phemt1的第一基波源阻抗匹配至输入负载阻抗(一般为50ω)附近圆形区域,即对晶体管phemt1的第一基波源阻抗进行初步阻抗匹配。

60.步骤a6,在步骤a3基础上,通过第三控制信号cs

in3

注入有源输出匹配网络,将第二晶体管phemt2的第二基波负载阻抗从输出负载阻抗附近圆形区域严格匹配至的输出负载

阻抗点,即对第二晶体管phemt2的第二基波负载阻抗进一步修正,实现精确控制。另一方面,通过第三控制信号cs

in3

注入有源输出匹配网络,使得第二晶体管phemt2的第二二次谐波负载阻抗和第二三次谐波负载阻抗处于短路点或者开路点。

61.步骤a7,在步骤a4基础上,通过第二控制信号cs

in2

注入有源级间匹配网络,将第一晶体管phemt1的第一基波负载阻抗从第二晶体管phemt2的基波源阻抗附近圆形区域严格匹配至第二晶体管phemt2的第二基波源阻抗,即对第一晶体管phemt1的第一基波负载阻抗和第二晶体管phemt2的第二基波源阻抗进一步修正,实现精确控制。另一方面,通过第二控制信号cs

in2

注入有源级间匹配网络,使得第一晶体管phemt1的第一二次谐波负载阻抗、第一三次谐波负载阻抗,第二晶体管phemt2的第二二次谐波源阻抗、第二三次谐波源阻抗处于短路点或者开路点。

62.步骤a8,在步骤a5基础上,通过第一控制信号cs

in1

注入有源输入匹配网络,将第一晶体管phemt1的第一基波源阻抗从输入负载阻抗附近圆形区域严格匹配至输入负载阻抗点,即对第一晶体管phemt1的第一基波负载阻抗进一步修正,实现精确控制。另一方面,通过第一控制信号cs

in1

注入有源输入匹配网络,使得第二晶体管phemt1的第二二次谐波源阻抗和第二三次谐波源阻抗处于短路点或者开路点。

63.步骤a9,根据步骤a

3-步骤a8所设计的匹配网络完成原理图和版图的整合优化。

64.本发明无源匹配和有源匹配效果图如图6所示。为了更方便的描述,以第二晶体管phemt2的基波负载阻抗匹配至输出负载阻抗(一般为50ω)为例进行说明,需要注意的是所描述的匹配效果对于第一晶体管phemt1的第一基波负载阻抗、第二晶体管phemt2的第二基波源阻抗、第一晶体管phemt1的第一基波源阻抗同样适用。后续描述中以初始阻抗点指代第二晶体管phemt2的第二基波负载阻抗,以最佳阻抗点指代输出负载阻抗(一般为50ω)。初始阻抗点靠近smith圆图的边缘位置,距离最佳阻抗点较远,在超宽带情况下无法直接将初始阻抗点匹配至最佳阻抗点。因此首先通过无源输出匹配网络将初始阻抗点进行初步阻抗匹配,即匹配至最佳阻抗点附近圆形区域,然后通过有源输出匹配网络对阻抗位置进一步修正,即从最佳阻抗点附近圆形区域严格匹配至最佳阻抗点。

65.如图7所示为本发明实施例中无源匹配网络初步阻抗匹配时效率与有源匹配网络进一步阻抗修正后效率的对比图,无源匹配网络初步阻抗匹配时功率附加效率pae典型值为26%,有源匹配网络进一步阻抗修正后功率附加效率pae典型值为32%。根据效率对比图可知,本发明的6-18ghz功率放大器,能解决超宽带功率放大器晶体管阻抗匹配问题,提高了超宽带功率放大器效率。

66.最后应说明的是:以上实施例仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1