一种基于Baseband阻抗匹配的高线性功率放大器的制作方法

一种基于baseband阻抗匹配的高线性功率放大器

技术领域

1.本发明涉及功率放大器,尤其涉及一种基于baseband阻抗匹配的高线性功率放大器。

背景技术:

2.随着新一代通信技术的发展,通讯系统对射频前端设备提出了更高的要求,特别是在满足输出功率的前提下,输出高峰均比、高效率和高线性的无线信号。而功率放大器作为射频前端设备的核心元器件,其性能对射频前端设备有直接的影响。

3.而对于功率放大器,常规提升线性度的方法有包络跟踪技术、异相技术和多偏置技术,基本都是在工作频带内进行线性度的设计与优化。然而功率放大器的线性度特别是三阶交调指标不仅与工作频带内的非线性特性相关,频带外比如baseband和谐波阻抗位置都对三阶交调有着不可忽略的影响,本发明开发了一种基于baseband阻抗匹配的高线性功率放大器,可有效精确的控制功率放大器baseband的阻抗位置,以优化功率放大器三阶交调特性。

技术实现要素:

4.发明目的:本发明的目的是提供一种能满足线性度指标要求的同时提升回退效率的基于baseband阻抗匹配的高线性功率放大器。

5.技术方案:本发明的高线性功率放大器,包括功率放大单元、漏偏置电路结构和栅偏置电路结构;

6.所述功率放大器单元采用单级或者多级晶体管组成;每一级晶体管的漏极加电网络采用漏偏置电路结构,每一级晶体管的栅极加电网络采用栅偏置电路结构。

7.进一步,所述漏偏置电路结构中,第一漏极电感和第二漏极电感依次串联连接于晶体管的漏极,第一漏极电容与第一漏极电感、第二漏极电感并联,构成晶体管漏偏置第一级去耦电路,同时兼顾基波负载阻抗匹配;第三漏极电感、第四漏极电感和第五漏极电感依次串联连接,第二漏极电容、第三漏极电容分别与第三漏极电感和第四漏极电感并联连接,第四漏极电容、第一漏极电阻串联连接后与第五漏极电感并联,共同构成晶体管漏偏置第二级去耦电路,同时兼顾输出负载端baseband阻抗匹配。

8.进一步,所述晶体管漏偏置第一级去耦电路,放在功率放大器单元内;所述晶体管漏偏置第二级去耦电路,放在功率放大器单元外。

9.进一步,所述栅偏置电路结构中,第一栅极电感、第二栅极电感和第一栅极电阻依次串联连接于晶体管的栅极,第一栅极电容与第二栅极电感并联,构成晶体管栅偏置第一级去耦电路,同时兼顾基波输入负载端阻抗匹配;第三栅极电感、第四栅极电感和第五栅极电感依次串联连接于第一栅极电阻,第二栅极电容、第三栅极电容分别与第三栅极电感和第四栅极电感并联,第四栅极电容、第二栅极电阻串联连接后与第五栅极电感并联,构成晶体管栅偏置第二级去耦电路,同时兼顾输入负载端baseband阻抗匹配。

10.进一步,所述晶体管栅偏置第一级去耦电路,同时兼顾基波负载阻抗匹配,放在功率放大器单元内;所述晶体管栅偏置第二级去耦电路,同时兼顾输入负载端baseband阻抗匹配,放在功率放大器单元外。

11.进一步,所述功率放大器单元中,每一级栅偏置电路单独或统一采用栅偏置电路结构,每一级漏偏置电路单独或统一采用漏偏置电路结构。

12.进一步,所述功率放大器单元还采用双边对称的加电网络结构,所述栅偏置电路结构与漏偏置电路结构分别对称分布在功率放大器单元两侧;栅电通过所述栅偏置电路结构提供给晶体管,漏电通过所述漏偏置电路结构提供给晶体管。

13.进一步,所述功率放大器单元选用gaas或gan材料作为基片。

14.本发明与现有技术相比,其显著效果如下:

15.1、本发明是通过栅偏置电路将输入端基波阻抗位置与基带阻抗位置进行协同设计优化,通过漏偏置电路将输出端基波阻抗位置与基带阻抗位置进行协同设计优化,对功率放大器的baseband阻抗进行精确的设计,提升了功率放大器在回退时的线性度(三阶交调),从而在回退更少功率时即可满足线性度指标要求,提升了回退的效率;同时也将外围去耦电路融入到基带阻抗设计中,可简化放大器内部匹配电路,减小芯片尺寸;

16.2、本发明通过baseband阻抗对线性度影响的理论研究,提出了一种可精确控制baseband阻抗的电路拓扑结构,可精确控制1mhz-400mhz之内的低频信号,使得baseband阻抗匹配到最优位置,从而提高了电路的线性度;

17.3、本发明中的栅/漏偏置电路具有可扩展性,可融合芯片外围去耦电路,不占用额外的面积,为通信系统小型化提供了支撑。

附图说明

18.图1为双音信号的频谱图;

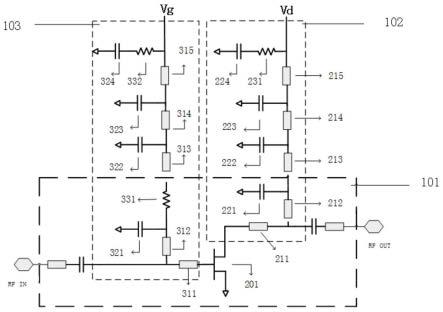

19.图2为基于baseband阻抗匹配的栅偏置电路与漏偏置电路的结构图;

20.图3为偏置电路中不同电阻值对baseband阻抗位置的影响示意图;

21.图4为一种基于baseband阻抗匹配的高线性功率放大器结构框图;

22.图5为有无baseband阻抗匹配的功率放大器三阶交调性能对比图。

具体实施方式

23.下面结合说明书附图和具体实施方式对本发明做进一步详细描述。

24.如图1所示,在功率放大器中,当注入两个不同频率的交流信号时,由于晶体管的非线性特性,在晶体管的输出端不仅会产生两个经过放大的主音信号外,即基波分量(ω1和ω2),还存在三阶交调分量(2ω

1-ω2和2ω

2-ω1),基波与三阶交调信号的幅值之差即为三阶交调(imd3)。其中:

25.imd3_lower=a(ω1)-a(2ω

1-ω2)

26.=a(ω1)

‑ꢀ

a(ω

1-(ω

2-ω1))

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(1)

27.imd3_higher=a(ω2)-a(2ω

2-ω1)

28.=a(ω1)

‑ꢀ

a(ω

1-(ω

2-ω1))

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(2)

29.式中:a为该频率点下的幅度值;ω

2-ω1=ωb,称为晶体管baseband信号。

30.而在功率放大器中,三阶交调分量(2ω

1-ω2和2ω

2-ω1)与基波分量(ω1和ω2)离的很近,无法通过滤波器将其去除,故三阶交调很大程度上表征器件的线性度特性。

31.在功率放大器设计中,基波分量(ω1和ω2)阻抗通常为最佳功率或最佳效率匹配,以获得更好的性能,如果基波按照最佳三阶交调性能进行匹配,其输出功率和效率将大大牺牲。为了提高器件的线性度值,即提高三阶交调值,将研究重点转移到三阶交调分量上。

32.从式(1)和(2)可以发现晶体管三阶交调分量还与baseband信号相关,可以通过改变其baseband阻抗位置,调制晶体管三阶交调分量,从而获得一个最佳的三阶交调特性,即是本发明的基本原理。

33.如图2所示为本发明的高线性功率放大器,包括功率放大单元101、漏偏置电路结构102和栅偏置电路结构103。

34.在功率放大器单元101中,采用单级或者多级晶体管201电路组成。每一级晶体管的漏极加电网络采用漏偏置电路结构102,每一级晶体管的栅极加电网络采用栅偏置电路结构103,从而可以有效的将晶体管的输入和输出端baseband阻抗位置都控制在一个较好的区域,提升功率放大器的线性度特性,特别是三阶交调指标。

35.在漏偏置电路结构102中,第一漏极电感211、第二漏极电感212依次串联连接后,与第一漏极电容221并联,构成了晶体管漏偏置第一级去耦电路,同时也兼顾基波负载阻抗匹配作用,通常放在功率放大器单元101(单片微波集成电路mmic)内。第三漏极电感213、第四漏极电感214和第五漏极电感215依次串联连接于第二漏极电感212,第二漏极电容222、第三漏极电容223分别与第三漏极电感213和第四漏极电感214并联,第四漏极电容224、第一漏极电阻231串联后与第五漏极电感215并联,共同构成了晶体管漏偏置第二级去耦电路,同时兼顾输出负载端baseband阻抗匹配作用。由于baseband频率较低,通常为1mhz-400mhz范围内,要想对其阻抗进行精确匹配控制,需采用较大容值的芯片电容或者贴片电容,故通常放在功率放大器单元101外。

36.在栅偏置电路结构103中,第一栅极电感311、第二栅极电感312、第一栅极串联电阻331依次串联连接于晶体管的栅极,第一栅极电容321与第二栅极电感312并联,共同构成了晶体管栅偏置第一级去耦电路,同时也兼顾基波源阻抗匹配,通常放在功率放大器单元101内。第三栅极电感313、第四栅极电感314和第五栅极电感315依次串联连接于第一栅极电阻331,第二栅极电容322、第三栅极电容323分别与第三栅极电感313和第四栅极电感314并联,第四栅极电容324、第二栅极电阻332串联后与第五栅极电感315并联,共同构成了晶体管栅偏置第二级去耦电路,同时兼顾输入源端baseband阻抗匹配。由于baseband频率较低,通常为1mhz-400mhz范围内,要想对其阻抗进行精确匹配控制,需采用较大容值的芯片电容或者贴片电容,故通常放在功率放大器单元101外。

37.如图3所示,根据两个主音信号的频率与间隔的大小,在晶体管的输出负载端,采用漏偏置电路结构,通过调节电感值、电容值与电阻值的大小,可以精确控制晶体管的baseband阻抗位置,使其匹配到晶体管输出负载端最理想位置,从而调制输出端的三阶交调特性。在晶体管的输入负载端,采用栅偏置电路结构,通过调节电感值、电容值与电阻值的大小,可以精确控制晶体管的baseband阻抗位置,使其匹配到晶体管输入负载端最理想位置,从而调制输入端的三阶交调特性。

38.如图4所示,给出了一个具体的基于baseband阻抗匹配的高线性功率放大器电路

结构:在功率放大器单元101中,采用三级晶体管201构成的放大电路,每一级栅偏置电路和漏偏置电路都可单独或者统一采用栅偏置电路结构103与漏偏置电路结构102。同时功率放大器单元可采用双边对称加电的方式,栅偏置电路结构103与漏偏置电路结构102则对称分布在功率放大器单元两侧,栅电与漏电分别通过栅偏置电路结构103与漏偏置电路结构102提供给晶体管,使得整个功率放大器单元加电平衡。

39.如图4所示,漏偏置电路结构102中的第二漏极电容222、第三漏极电容223所需容值不大,通常采用外置芯片电容,其容值可选150pf和1000pf,构成漏偏置第二级极去耦电路。第四漏极电容224所需容值较大,通常采用外置贴片电容,根据漏端baseband频率大小,其选择容值在0.1uf~10uf范围内。同理,根据不同漏端baseband最佳阻抗位置,选取第一漏极电阻231的阻值。第四漏极电容224和第一漏极电阻231共同构成了漏偏置第三级去耦电路。

40.如图4所示,栅偏置电路结构103中的第二栅极电容322、第三栅极电容323所需容值不大,通常采用外置芯片电容,其容值可选150pf和1000pf,构成栅偏置第二级去耦电路。第四栅极电容324所需容值较大,通常采用外置贴片电容,根据源端baseband频率大小,其选择容值在0.1uf~10uf范围内。同理,根据不同源端baseband最佳阻抗位置选取第二栅极电阻332的阻值。第四栅极电容324和第二栅极电阻332共同构成了栅偏置第三级去耦电路。

41.同时基波阻抗匹配电路结构、baseband阻抗匹配电路结构与直流加电去耦电路三者相融合,共同构成了栅偏置电路结构103与漏偏置电路结构102,简化了功率放大器单元的设计,同时提升了功率放大器单元的整体性能。

42.如图5所示,有无baseband阻抗控制的功率放大器其三阶交调性能对比可以看出,在相同回退3db,输出功率回退到38dbm时,采用baseband阻抗控制,其im3可提升5dbc,且在一定功率回退范围内,其im3最大可优化10dbc。再继续回退到较为线性区时,其baseband阻抗控制对电路im3的影响逐渐减小,因电路im3分量逐渐减小。

43.综合考虑工作频率、带宽、功率、效率、三阶交调、一致性、成品率、成本,以适当的半导体技术制造,功率放大器单元101选用gaas或gan材料作为基片,但不限于此。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1