一种串转并多通道输出电路及控制系统的制作方法

1.本实用新型涉及串转并多通道输出电路技术领域,尤其涉及一种串转并多通道输出电路及控制系统。

背景技术:

2.继电器、电磁阀等开关设备作为开关器件在物联网场景下的应用越来越广泛,目前市面上控制多通道的继电器或者电磁阀的常用方法是通过一个八路串转并控制芯片(如 74hc595),外加一个八路的低边输出驱动芯片(如八通道的达林顿驱动芯片)来实现。

3.但是在应用中许多问题也随之出现,首先八路串转并控制芯片有较多的输入数据信号,因此需要占用较多的mcu io口资源;其次八路串转并控制芯片输出八路并行数据信号,需要对应连接到八路低边输出驱动芯片的输入端口,pcb布线数量较多,布板难度较大;最后当需要控制大于八通道的继电器或电磁阀输出时,需要更多的串转并控制芯片和更多的低边输出驱动芯片,这无疑进一步增加了pcb板的布板难度和成本。

4.可见,现有技术中存在串转并电路需要占用较多的io口资源、多通道的串转并电路 pcb布板困难等问题。

技术实现要素:

5.针对现有技术中所存在的不足,本实用新型提供的一种串转并多通道控制电路及控制系统,解决了传统串转并控制电路中串转并控制芯片io口资源占用较多、pcb布线较多且布板难度大等问题。

6.第一个方面,根据本实用新型的实施例,提出来一种串转并多通道输出电路,所述输出电路包括:

7.信号串转并模块、信号锁存模块、复位信号生成模块、使能信号生成模块和信号输出模块;

8.所述信号串转并模块包含若干个d触发器,其中每个d触发器都有d端、q端和clk 端,每个所述d触发器的clk端与时钟信号输出端相连,最后一个d触发器的d端与数据信号输出端相连,其余d触发器的d端均与上一个d触发器的q端相连接;

9.所述信号锁存模块包含和d触发器数量相同的d锁存器,其中每个d锁存器都有d' 端、q'端、clk端和r端,每个所述d锁存器的clk端均与锁存时钟信号相连接,每个所述d锁存器的d'端与对应的d触发器的q端相连接,每个所述d锁存器的r端均与复位信号生成模块的输出端相连接;

10.所述信号输出模块包含和输出通道数量相同的与门电路,每个所述与门电路的第一输入端与对应的d锁存器的q'端相连接,每个所述与门电路的第二输入端均与使能信号生成模块的输出端相连接,每个所述与门电路的输出端连接控制电路;

11.所述复位信号生成模块的输入端和使能信号生成模块的输入端均与信号串转并模块相连接。

12.在一个实施例中,d触发器、d锁存器的数量均为18,与门电路的数量为12。

13.在一个实施例中,所述数据信号包括五位的复位识别信号、十八位的开关信号和五位的使能识别信号。

14.在一个实施例中,所述复位信号生成模块为3-8译码器,用于在识别到复位识别信号时,向每一个d锁存器的r端发送一次复位信号。

15.在一个实施例中,所述使能信号生成模块为3-8译码器,用于在识别到使能识别信号时,向每一个与门电路的第二输入端持续发送使能信号。

16.在一个实施例中,所述输出电路还包括一个与信号串转并模块相连接的线性稳压单元 ldo,用于为电路提供工作电压。

17.第二个方面,在一个实施例中,提出来一种串转并多通道控制系统,包括上述实施例中任意一项所述的串转并多通道输出电路、若干个低边驱动电路、电源模块和若干个开关装置;

18.所述电源模块分别与所述串转并多通道输出电路的vm端和若干个开关装置的第二端相连接;

19.所述若干个低边驱动电路分别与所述串转并多通道输出电路的每一个输出端和开关装置的第一端相连接,用于在接收到数据信号时驱动开关装置动作。

20.在一个实施例中,所述低边驱动电路包括:

21.驱动电路、nmos管和续流二极管,所述驱动电路的输入端与所述串转并多通道输出电路的输出端相连接,所述驱动电路的输出端与nmos管的栅极相连接,所述nmos管的漏极分别与续流二极管的第一端和开关装置的第一端相连,所述nmos管的源极接地,所述续流二极管的第二端与电源模块相连接。

22.在一个实施例中,所述电源模块包括两个相互串联的蓄电池组成的蓄电池组,以及与蓄电池组并联的电容,所述电容的大小为100uf。

23.在一个实施例中,所述开关装置包括电磁阀和/或继电器。

24.相比于现有技术,本实用新型具有如下有益效果:

25.1、通过采用若干个相互连接的d触发器、d锁存器、复位信号发射器和使能信号发射器,实现了两通道输入转多通道(大于八通道)输出的功能,减少了io口资源的占用。

26.2、通过对输出电路连接一个低边驱动电路,实现了低输出电压对高电压需求的开关装置的控制。

附图说明

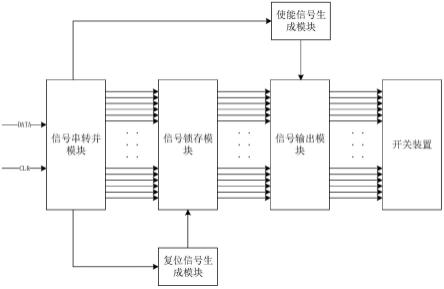

27.图1为本实用新型实施例的串转并多通道输出电路整体结构图。

28.图2为本实用新型另一实施例的串转并多通道输出电路的数字电路图。

29.图3为本实用新型另一实施例的串转并多通道控制系统的整体电路图。

30.图4为本实用新型另一实施例的低边驱动电路的电路图。

具体实施方式

31.下面结合附图及实施例对本实用新型中的技术方案进一步说明。

32.第一个方面,根据本实用新型的实施例,如图1所示,提出来一种串转并多通道输

出电路,所述输出电路包括:

33.信号串转并模块、信号锁存模块、复位信号生成模块、使能信号生成模块和信号输出模块;

34.所述信号串转并模块包含若干个d触发器,其中每个d触发器都有d端、q端和clk 端,每个所述d触发器的clk端与时钟信号输出端相连,最后一个d触发器的d端与数据信号输出端相连,其余d触发器的d端均与上一个d触发器的q端相连接;

35.所述信号锁存模块包含和d触发器数量相同的d锁存器,其中每个d锁存器都有d' 端、q'端、clk端和r端,每个所述d锁存器的clk端均与锁存时钟信号相连接,每个所述d锁存器的d'端与对应的d触发器的q端相连接,每个所述d锁存器的r端均与复位信号生成模块的输出端相连接;

36.所述信号输出模块包含和输出通道数量相同的与门电路,每个所述与门电路的第一输入端与对应的d锁存器的q'端相连接,每个所述与门电路的第二输入端均与使能信号生成模块的输出端相连接,每个所述与门电路的输出端连接控制电路;

37.所述复位信号生成模块的输入端和使能信号生成模块的输入端均与信号串转并模块相连接。

38.在上述实施例中,信号串转并模块包含若干个d触发器,每个所述d触发器的clk端与时钟信号输出端相连,最后一个d触发器的d端与数据信号输出端相连,其余d触发器的d端均与上一个d触发器的q端相连接,在d触发器接收到的时钟信号的上升沿到来时,当前d触发器将d输入端的数据信号传送到q输出端,和下一d触发器的d输入端,以此类推,直到若干个时钟信号的上升沿到来后,将数据信号的每一位传送到对应的d触发器的d输入端;

39.信号锁存模块包含若干个d锁存器,每个d锁存器的d’输入端和对应的d触发器的 q输出端相连接,每个d锁存器的q’输出端和与门电路的第一输入端相连接,每个d锁存器的r输入端与复位信号生成模块的输出端相连接,每个d锁存器的clk端均与锁存时钟信号相连接,当复位信号生成模块没有向r端发送复位信号时,每一个d锁存器的q’输出端在第一次接收到d’输入端传送的数据信号后,不随d’接收到的数据信号的改变而改变,起到信号锁存的功能,当复位信号生成模块向r端发送一次复位信号后,每一个 d锁存器的q’输出端清零复位,在下一个锁存时钟信号的上升沿到来后,接收对应的d 触发器的输出端q输出的数据信号,并将该数据信号锁存;

40.当使能信号生成模块向与门电路的第二输出端发送使能信号时,与门电路将q’输出端当前的数据信号发送至低边驱动电路,以控制对应的开关装置的动作。

41.在本实施例中,数据信号和时钟信号两通道的输入通过由若干个d触发器组成的信号串转并模块,和若干个d锁存器组成的信号锁存模块,并在复位信号生成模块和使能信号生成模块的控制下,将特定位置的数据信号分配到对应的输出通道中,实现了将2通道的输入数据转为多通道的数据输出,减少了对io口资源的占用。

42.在一个优选的实施例中,如图2所示,d触发器、d锁存器的数量均为18,与门电路的数量为12,所述数据信号包括五位的复位识别信号“10000”、十八位的开关信号“b1b2b2

’ꢀ

b3b4b4’b5b6b6’b7b8b8’b9b10b10’b11b12b12

’”

和五位的使能识别信号“01111”;所述复位信号生成模块为3-8译码器,用于在识别到复位识别信号时,向每一个d锁存器的r端发送一次复位信号;所述使能信号生成模块为3-8译码器,用于在识别到使能识别信号时,向每一

个与门电路的第二输入端持续发送使能信号;

43.在上述实施例中,bn为对应outn通道的开关信号,bn=1,则开启outn通道,bn=0,则关闭outn通道(n=1—12);每隔一个数据信号,对当前数据信号进行一次取反,起到了防止数据信号和复位识别信号、使能识别信号相冲突的作用;

44.复位信号生成模块的输入端与信号串转并模块中第一个d触发器的q1端相连接,在连续接收到四个0后向信号锁存模块中每一个d锁存器的r端发送一次复位信号,信号锁存模块中每一个d锁存器的q’输出端清零,在下一个时钟上升沿到来时,接收信号串转并模块对应的d触发器q输出端的数据信号,并锁存;

45.使能信号生成模块的输入端与信号串转并模块中最后一个d触发器的q18端相连接,在连续接收到四个1后向每个与门电路中的第二输入端持续发送使能信号,与门电路将第一输入端从对应d锁存器的q’接收到的数据信号,发送到输出端。

46.在一个实施例中,所述输出电路还包括一个与信号串转并模块相连接的线性稳压单元 ldo,用于为电路提供工作电压。

47.在上述实施例中,线性稳压单元ldo将输入的数据信号的电压控制在3.0v-3.3v之间,起到稳压、保护电路的作用。

48.第二个方面,在一个实施例中,提出来一种串转并多通道控制系统,如图3所示,包括上述实施例中任意一项所述的串转并多通道输出电路、若干个低边驱动电路、电源模块和若干个开关装置;

49.所述电源模块分别与所述串转并多通道输出电路的vm端和若干个开关装置的第二端相连接;

50.所述若干个低边驱动电路分别与所述串转并多通道输出电路的每一个输出端和开关装置的第一端相连接,用于在接收到数据信号时驱动开关装置动作。

51.在上述实施例中,串转并多通道输出电路将该路数据信号发送到低边驱动电路中,若数据信号为高电平1时,则驱动开关装置动作;若数据信号为低电平0时,则停止驱动开关装置动作,实现了低输出电压对高电压需求的开关装置的控制。

52.在一个实施例中,如图4所示,所述低边驱动电路包括:

53.驱动电路、nmos管和续流二极管,所述驱动电路的输入端与所述串转并多通道输出电路的输出端相连接,所述驱动电路的输出端与nmos管的栅极相连接,所述nmos管的漏极分别与续流二极管的第一端和开关装置的第一端相连,所述nmos管的源极接地,所述续流二极管的第二端与电源模块相连接。

54.在上述实施例中,当串转并多通道输出电路的输出端输出高电平时,电平信号通过一个驱动电路传送到nmos管的栅极,驱动电平信号的电压大于栅极启动电压,nmos管驱动源极和漏极导通,vm端电流通过开关装置流入大地,开关装置动作;

55.当串转并多通道输出电路的输出端输出低电平时,电平信号通过一个驱动电路传送到 nmos管的栅极,驱动电平信号的电压低于栅极启动电压,nmos管的栅极驱动源极和漏极不导通,开关装置不动作。

56.在一个实施例中,所述电源模块包括两个相互串联的蓄电池组成的蓄电池组,以及与蓄电池组并联的电容,所述电容的大小为100uf。

57.在一个实施例中,所述开关装置包括电磁阀和/或继电器。

58.最后说明的是,以上实施例仅用以说明本实用新型的技术方案而非限制,尽管参照较佳实施例对本实用新型进行了详细说明,本领域的普通技术人员应当理解,可以对本实用新型的技术方案进行修改或者等同替换,而不脱离本实用新型技术方案的宗旨和范围,其均应涵盖在本实用新型的权利要求范围当中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1