一种高集成度核心电路板的制作方法

1.本实用新型涉及核心电路板技术领域,具体为一种高集成度核心电路板。

背景技术:

2.随着工业与电子技术的快速发展,设备对核心电路板要求越来越高,越来越细,特别是对核心电路的集成度、成本、性能、接口资源等方面要求尤为突出,但大多数传统的核心电路板是很难平衡这些方面要求,如要求低成本就难以做到高性能;要求接口资源丰富就难以做到高集成度,因此需寻找一款可以平衡多方面的核心电路板,即一种高集成度核心电路板来解决存在的问题。

技术实现要素:

3.本实用新型的目的在于提供一种高集成度核心电路板,以解决上述背景技术中提出的问题。

4.为实现上述目的,本实用新型提供如下技术方案:

5.一种高集成度核心电路板,包括主控芯片模块cpu、存储芯片模块emmc、电源管理模块pmic、内存芯片模块lpddr4、邮票孔焊盘和lga焊盘,所述主控芯片模块cpu、存储芯片模块emmc、电源管理模块pmic、内存芯片模块lpddr4、邮票孔焊盘和lga焊盘集成在核心电路板本体pcb上,所述核心电路板本体pcb通过邮票孔焊盘和lga焊盘引出信号和电源地共计222个脚,其中邮票孔焊盘对应核心电路板本体pcb的第1引脚~第164引脚,lga焊盘对应核心电路板本体pcb的第l1引脚~第l58引脚。

6.作为本实用新型优选的方案,所述核心电路板本体pcb为高集成度矩形设计,体积尺寸为43mm*45mm,工艺采用10层板设计,沉金工艺制造而成,并且沉金厚度在0.025~0.1um间,所述主控芯片模块cpu为处理器t507-h,其主要负责内容包括处理指令、执行操作、控制时间和处理数据。

7.作为本实用新型优选的方案,所述核心电路板本体pcb的第1引脚~第164引脚,其中第1引脚~第11引脚为power和ctrl,第12引脚~第42引脚为lvds接口,第43引脚~第66引脚为parallel camera接口,第67引脚~第89引脚为gphy接口,第90引脚~第102引脚为sdio接口,第103引脚~第121引脚为mipi-csi接口,第122引脚~第124引脚为tv接口,第125引脚~第140引脚为hdmi接口,第141引脚~第152引脚为usb接口,第153引脚~第164引脚为ephy接口。

8.作为本实用新型优选的方案,所述电路板本体pcb的第l1引脚~第l58引脚,其中第l1引脚~第l10引脚为uart接口,第l11引脚~第l16引脚为boot接口,第l17引脚~第l29引脚为audio接口,第l30引脚~第l45引脚为普通gpio接口,第l46引脚~第l51引脚为adc接口,第l52引脚~第l55引脚为twi接口,第l56引脚~第l58引脚为其他接口。

9.作为本实用新型优选的方案,所述存储芯片模块emmc为h26m41208hpri,包括信号引脚、clk引脚、cmd引脚、ds引脚和rst引脚,分别与主控芯片模块cpu对应的功能引脚连接,

用于存储核心电路板本体pcb运行所必须的系统软件以及设备运行的应用软件。

10.作为本实用新型优选的方案,所述电源管理模块pmic为axp853t,包括sda引脚、sck引脚、irq引脚、wakeup引脚、多组dc/dc引脚、多组aldo引脚、多组bldo引脚、多组cldo用于输出不同电压,其中dc/dc引脚与主控芯片模块cpu连接,使得电源管理模块pmic能够提供多种不同需求的稳定电压。

11.作为本实用新型优选的方案,所述内存芯片模块lpddr4为atl4x08324m082,采用单颗内存芯片,包括多组数据sdq引脚、时钟引脚sck、多组地址引脚sa和rst引脚,用于暂时存放主控芯片模块cpu中的运算数据,以及与电源管理模块pmic外部储存器交换的数据。

12.与现有技术相比,本实用新型的有益效果是:

13.1、本实用新型中,通过一种高集成度核心电路板,其中核心电路板本体pcb的引脚位置和定义的特殊设计,使得各个模块集成在体积非常小的pcb电路板上,从而解决核心电路板尺寸受限的问题;

14.2、本实用新型中,通过一种高集成度核心电路板,其中核心电路板本体pcb资源接口采用邮票孔+lga背面焊盘的连接方式,最大限度将所有资源全部引出,在保证核心电路板具有丰富的资源和高性能的同时,能够节省4个以上连接器成本。

附图说明

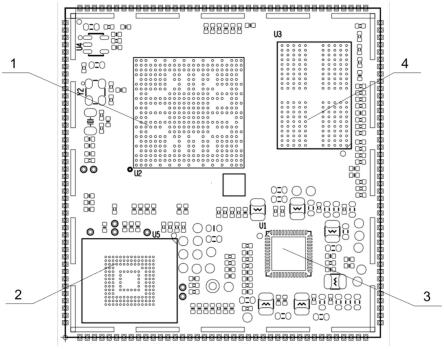

15.图1为本实用新型正面结构示意图;

16.图2为本实用新型背面结构示意图;

17.图3为本实用新型机械尺寸示意图;

18.图4为本实用新型接口资源示意图;

19.图5为本实用新型资源分配原理图;

20.图6为本实用新型实物正面示意图;

21.图7为本实用新型实物背面示意图。

22.图中:1-主控芯片模块cpu;2、存储芯片模块emmc;3、电源管理模块pmic;4、内存芯片模块lpddr4;5、邮票孔焊盘;6、lga焊盘、7-核心电路板本体pcb。

具体实施方式

23.下面将结合本实用新型实施例,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例,基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

24.为了便于理解本实用新型,下面将参照相关附图对本实用新型进行更全面的描述,给出了本实用新型的若干实施例,但是,本实用新型可以以许多不同的形式来实现,并不限于本文所描述的实施例,相反地,提供这些实施例的目的是使对本实用新型的公开内容更加透彻全面。

25.需要说明的是,当元件被称为“固设于”另一个元件,它可以直接在另一个元件上或者也可以存在居中的元件,当一个元件被认为是“连接”另一个元件,它可以是直接连接到另一个元件或者可能同时存在居中元件,本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

26.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领域的技术人员通常理解的含义相同,本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型,本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

27.实施例,请参阅图1-7,本实用新型提供一种技术方案:

28.高集成度核心电路板,其包括核心电路板本体pcb 7,该核心电路板本体pcb4将主控芯片模块cpu 1、存储芯片模块emmc 2、电源管理模块pmic 3、内存芯片模块lpddr4 4等集成在体积非常小的核心电路板本体pcb 7上,核心电路板本体pcb 7为高集成度矩形设计,尺寸大小仅为43mm*45mm,满足设备对核心电路板本体pcb 7高集成度的要求;核心电路板本体pcb 7工艺采用10层板设计,沉金工艺,沉金工艺采用的是化学沉积的方法,通过化学氧化还原反应的方法生成一层镀层,并且沉金厚度在0.025~0.1um间,具有最佳的电气性能和抗干扰性能;资源接口采用邮票孔+lga背面焊盘的连接方式,保障222pin的同时,能够节省4个以上连接器成本;在提供高可靠连接及高集成度的同时,最大限度将gpio资源全部引出,保证核心电路板本体pcb 7具有丰富的资源可以使用;

29.具体实施方式:如图1、图2所示,高集成度核心电路板,其包括主控芯片模块cpu 1、存储芯片模块emmc 2、电源管理模块pmic 3、内存芯片模块lpddr4 4、邮票孔焊盘5、lga焊盘6;

30.其中主控芯片模块cpu1为高性能的处理器t507-h,是核心电路板的最重要部分,主要负责处理指令、执行操作、控制时间、处理数据;

31.存储芯片模块emmc 2为h26m41208hpri,包括信号引脚、clk引脚、cmd引脚、ds引脚和rst引脚,分别与主控芯片模块对应的功能引脚连接,用于存储核心电路板运行所必须的系统软件以及设备运行的应用软件;

32.内存芯片模块lpddr4 4为atl4x08324m082,采用单颗内存芯片,包括多组数据sdq引脚、时钟引脚sck、多组地址引脚sa和rst引脚;用于暂时存放主控芯片中的运算数据,以及与存储芯片模块emmc 2等外部储存器交换的数据,内存芯片模块lpddr4 4是外设与主控芯片模块cpu 1进行沟通的桥梁;

33.电源管理模块pmic 3为axp853t,包括sda引脚、sck引脚、irq引脚、wakeup引脚、多组dc/dc引脚、多组aldo引脚、多组bldo引脚、多组cldo用于输出不同电压,其中dc/dc引脚与主控芯片模块cpu 1连接,使得电源管理模块pmic 3能够提供多种不同需求的稳定电压,保障核心电路板的稳定运行;

34.核心电路板本体pcb 7通过邮票孔焊盘5和lga焊盘6引出信号和电源地共计222个脚,邮票孔焊盘5对应核心电路板的第1引脚~第164引脚,lga焊盘6对应核心电路板本体pcb 7的第l1引脚~第l58引脚。

35.其中第1引脚~第11引脚为power和ctrl,第12引脚~第42引脚为lvds接口,第43引脚~第66引脚为parallel camera接口,第67引脚~第89引脚为gphy接口,第90引脚~第102引脚为sdio接口,第103引脚~第121引脚为mipi-csi接口,第122引脚~第124引脚为tv接口,第125引脚~第140引脚为hdmi接口,第141引脚~第152引脚为usb接口,第153引脚~第164引脚为ephy接口。

36.其中第l1引脚~第l10引脚为uart接口,第l11引脚~第l16引脚为boot接口,第l17引脚~第l29引脚为audio接口,第l30引脚~第l45引脚为普通gpio接口,第l46引脚~第l51引脚为adc接口,第l52引脚~第l55引脚为twi接口,第l56引脚~第l58引脚为其他接口。

37.核心电路板过邮票孔焊盘和lga焊盘最大限度将所有资源全部引出,保证核心电路板具有丰富的资源可以使用。

38.尽管已经示出和描述了本实用新型的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本实用新型的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本实用新型的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1