封装体的制作方法

本技术涉及封装体,尤其是一种具有晶体管开关的封装体。

背景技术:

1、按照安装在pcb板上的方式来划分,mos管封装主要有两大类:插入式(throughhole)和表面贴装式(surface mount)。

2、插入式就是mosfet的管脚穿过pcb板的安装孔并焊接在pcb板上。常见的插入式封装有:双列直插式封装(dip)、晶体管外形封装(to)、插针网格阵列封装(pga)三种样式。

3、表面贴装则是mosfet的管脚及散热法兰焊接在pcb板表面的焊盘上。典型表面贴装式封装有:晶体管外形(d-pak)、小外形晶体管(sot)、小外形封装(sop)、方形扁平式封装(qfp)、塑封有引线芯片载体(plcc)等。

4、pcb(printed circuit board),中文名称为印制封装体,又称印刷线路板,是重要的电子部件,是电子元器件的支撑体,是电子元器件电气连接的载体。由于它是采用电子印刷术制作的,故被称为“印刷”封装体。

5、pcb散热.对于电子设备来说,工作时都会产生一定的热量,从而使设备内部温度迅速上升,尤其是mosfet这种高发热的元件,如果不及时将该热量散发出去,设备就会持续的升温,器件就会因过热而失效,电子设备的可靠性能就会下降。因此,对封装体进行很好的散热处理是非常重要的。pcb封装体的散热是一个非常重要的环节。

技术实现思路

1、本实用新型要解决的技术问题是:提供一种封装体,其包含一多层基板及位于多层基板内的一晶体基板,以便解决先前技术中的晶体管开关的散热的问题。

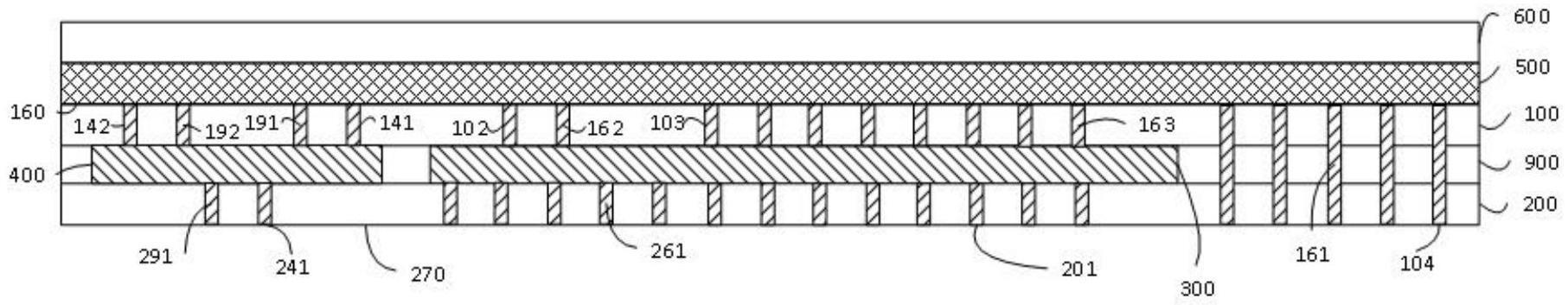

2、为达到上述目的,本实用新型提供了一种封装体,包含一多层基板、至少一导电层以及一晶体基板。多层基板具有一第一层及一第二层。第一层及第二层至少其中之一包含复数个导通孔。晶体基板具有一第一晶体管开关及一第二晶体管开关,且位于第一层及第二层之间。第一晶体管开关具有一第一导电极、一第二导电极以及一第一受控极。第二晶体管开关具有一第三导电极、一第四导电极以及一第二受控极。至少一导电层具有复数个彼此电性隔离的导电区。复数个导通孔中的每一导通孔具有一导电直柱,分别电性连接至少一导电层的至少部分导电区至第一晶体管开关的第一导电极、第二导电极及第一受控极以及第二晶体管开关的第三导电极、第四导电极及第二受控极中的对应者。

3、本实用新型的封装体更可以包含一控制器,具有一第一控制极及一第二控制极。第一受控极对应的导电区电性连结第一控制极。第二受控极对应的导电区电性连结第二控制极。第一控制极输出一第一控制讯号至第一受控极以控制第一晶体管开关于一导通状态及一截止状态之间切换。第二控制极输出一第二控制讯号至第二受控极以控制第二晶体管开关于一导通状态及一截止状态之间切换,其中第一晶体管开关之导通状态与第二晶体管开关之导通状态之时序不重叠。

4、本实用新型的一更佳实施例中,第二导电极与第三导电极对应至同一导电区,透过对应的些导电直柱而彼此电性连接。

5、本实用新型也提供了另一种封装体,具有一多层基板、至少一导电层以及一晶体基板。多层基板,具有一第一层及一第二层,第一层及第二层至少其中之一包含复数个导通孔。晶体基板具有一第一晶体管开关、一第二晶体管开关、一第三晶体管开关、一第四晶体管开关。晶体基板位于第一层及第二层之间。第一晶体管开关具有一第一导电极、一第二导电极以及一第一受控极。第二晶体管开关具有一第三导电极、一第四导电极以及一第二受控极。第三晶体管开关具有一第五导电极、一第六导电极以及一第三受控极。第四晶体管开关,具有一第七导电极、一第八导电极以及一第四受控极。至少一导电层具有复数个彼此电性隔离的导电区。复数个导通孔中的每一导通孔具有一导电直柱,分别电性连接至少一导电层的至少部分导电区至第一晶体管开关的第一导电极、第二导电极及第一受控极、第二晶体管开关的第三导电极、第四导电极及第二受控极、第三晶体管开关的第五导电极、第六导电极及第三受控极、第四晶体管开关的第七导电极、第八导电极及第四受控极中的对应者,且第一导电极与第五导电极电性连接至同一导电区,以及第四导电极与第八导电极电性连接至同一导电区。

6、本实用新型的封装体更可以包含一控制器,具有一第一控制极、一第二控制极、一第三控制极及一第四控制极。第一受控极对应的导电区电性连结第一控制极。第二受控极对应的导电区电性连结第二控制极。第三受控极对应的导电区电性连结第三控制极。第四受控极对应的导电区电性连结第四控制极。第一控制极输出一第一控制讯号至第一受控极以控制第一晶体管开关于一导通状态及一截止状态之间切换。第二控制极输出一第二控制讯号至第二受控极以控制第二晶体管开关于一导通状态及一截止状态之间切换。第三控制极输出一第三控制讯号至第三受控极以控制第三晶体管开关于一导通状态及一截止状态之间切换。第四控制极输出一第四控制讯号至第四受控极以控制第四晶体管开关于一导通状态及一截止状态之间切换。其中第一晶体管开关之导通状态与第二晶体管开关之导通状态之时序不重叠,且第三晶体管开关之导通状态与第四晶体管开关之导通状态之时序不重叠。

7、上述的控制器所输出的第一控制讯号与第三控制讯号之相位差为180度,以及第二控制讯号与第四控制讯号之相位差为180度。

8、本实用新型又提供了另一种封装体,具有一多层基板、至少一导电层以及一晶体基板。多层基板具有一第一层及一第二层,其中。第一层及第二层至少其中之一包含复数个导通孔。晶体基板具有一第一晶体管开关、一第二晶体管开关、一第三晶体管开关、一第四晶体管开关、一第五晶体开关及一第六晶体开关。晶体基板位于第一层及第二层之间。第一晶体管开关具有一第一导电极、一第二导电极以及一第一受控极。第二晶体管开关具有一第三导电极、一第四导电极以及一第二受控极。第三晶体管开关具有一第五导电极、一第六导电极以及一第三受控极。第四晶体管开关具有一第七导电极、一第八导电极以及一第四受控极。第五晶体管开关具有一第九导电极、一第十导电极以及一第五受控极。第六晶体管开关具有一第十一导电极、一第十二导电极以及一第六受控极。至少一导电层具有复数个彼此电性隔离的导电区。复数个导通孔的每一导通孔具有一导电直柱,分别电性连接至少一导电层的至少部分导电区至第一晶体管开关的第一导电极、第二导电极及第一受控极、第二晶体管开关的第三导电极、第四导电极及第二受控极、第三晶体管开关的第五导电极、第六导电极及第三受控极、第四晶体管开关的第七导电极、第八导电极及第四受控极、第五晶体管开关的第九导电极、第十导电极及第五受控极、六晶体管开关的第十一导电极、第十二导电极及第六受控极中的对应者。

9、本实用新型的一较佳实施例中,第一层具有复数空洞区,至少一导电层的部分导电区位于其中,且不与导电直柱电性连接的些部分导电区与晶体基板中对应晶体管开关直接电性连接。

10、本实用新型的一更佳实施例中,封中体更包含一导热绝缘层以及一散热金属层。导热绝缘层位于第一层之上,而散热金属层位于导热绝缘层之上。

11、本实用新型的封装体更包含一控制器,具有一第一控制极、一第二控制极、一第三控制极、一第四控制极、一第五控制极及一第六控制极。第一受控极对应的导电区电性连结第一控制极。第二受控极对应的导电区电性连结第二控制极。第三受控极对应的导电区电性连结第三控制极。第四受控极对应的导电区电性连结第四控制极。第五受控极对应的导电区电性连结第五控制极。第六受控极对应的导电区电性连结第六控制极。第一控制极输出一第一控制讯号至第一受控极以控制第一晶体管开关于一导通状态及一截止状态之间切换。第二控制极输出一第二控制讯号至第二受控极以控制第二晶体管开关于一导通状态及一截止状态之间切换。第三控制极输出一第三控制讯号至第三受控极以控制第三晶体管开关于一导通状态及一截止状态之间切换。第四控制极输出一第四控制讯号至第四受控极以控制第四晶体管开关于一导通状态及一截止状态之间切换。第五控制极输出一第五控制讯号至第五受控极以控制第五晶体管开关于一导通状态及一截止状态之间切换。第六控制极输出一第六控制讯号至第六受控极以控制第六晶体管开关于一导通状态及一截止状态之间切换。其中,第一晶体管开关之导通状态与第二晶体管开关之导通状态之时序不重叠,第三晶体管开关之导通状态与第四晶体管开关之导通状态之时序不重叠,且第五晶体管开关之导通状态与第六晶体管开关之导通状态之时序不重叠。

12、上述的控制器所输出的该第一控制讯号、第三控制讯号与第五控制讯号之两两之间的相位差为120度,以及第二控制讯号、第四控制讯号与第六控制讯号两两之间的相位差为120度。

13、综上所述,本实用新型透过导通孔形成导电直柱与晶体管开关电性连接,利用复数的导电直柱,不仅导电路径的长度缩短了,宽度加大了,降低了线阻及热的产生,进一步拉近了晶体管开关与散热区域的距离以及增加了散热的面积,因此热阻降低了,散热效果也获得提升。

14、以上的概述与接下来的详细说明皆为示范性质,是为了进一步说明本实用新型的申请专利范围。而有关本实用新型的其他目的与优点,将在后续的说明与图示加以阐述。

- 还没有人留言评论。精彩留言会获得点赞!