形成微电子装置的方法以及相关的微电子装置、存储器装置及电子系统与流程

在各种实施例中,本公开大体上涉及微电子装置设计及制造领域。更具体来说,本公开涉及形成微电子装置的方法以及相关的微电子装置、存储器装置及电子系统。

背景技术:

1、微电子装置设计者通常期望通过减小个别特征的尺寸且通过减小相邻特征之间的分离距离而增大微电子装置内的特征的集成水平或密度。另外,微电子装置设计者通常寻求设计不仅紧凑,而且提供性能优势以及简化设计的架构。

2、微电子装置的一个实例是存储器装置。存储器装置通常被提供为计算机或其它电子装置中的内部集成电路。存在许多类型的存储器装置,包含但不限于非易失性存储器装置(例如,nand快闪存储器装置)。一种增大非易失性存储器装置中的存储器密度的方式是利用竖直存储器阵列(也被称为“三维(3d)存储器阵列”)架构。常规竖直存储器阵列包含竖直延伸穿过包含导电材料及绝缘材料的层级的一或多个堆叠结构的存储器单元串。每一存储器单元串可包含耦合到其的至少一个选择装置。与具有常规平坦(例如,二维)晶体管布置的结构相比较,此配置允许通过在裸片上向上(例如,竖直)构建阵列而使更大数目个切换装置(例如,晶体管)位于单位裸片面积(即,所消耗有效表面的长度及宽度)中。

3、竖直存储器阵列架构通常包含存储器装置的(若干)堆叠结构的层级的导电材料与控制逻辑装置(例如,串驱动器)之间的电连接使得可唯一地选定竖直存储器阵列的存储器单元以用于写入、读取或擦除操作。一种形成此电连接的方法包含在存储器装置的(若干)堆叠结构的层级的边缘(例如,水平端)处形成所谓的“阶梯”(或“楼梯”)结构。阶梯结构包含界定层级的导电材料的接触区的个别“台阶”,导电接触结构可被定位在所述台阶上以提供对导电材料的电接入。继而,可采用导电布线结构来将导电接触结构耦合到控制逻辑装置。不幸的是,随着特征堆积密度增大且形成误差的裕度减小,常规制造方法及所得结构配置已导致非期望缺陷,这可降低所期望存储器装置性能、可靠性及耐久性。

技术实现思路

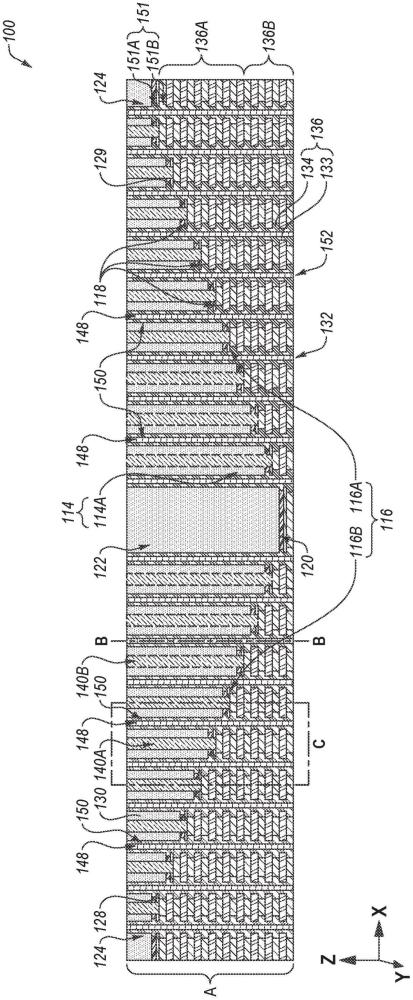

1、在一些实施例中,一种微电子装置包括堆叠结构,所述堆叠结构包括布置成层级的导电材料及绝缘材料的竖直交替序列。所述堆叠结构具有通过介电狭槽结构彼此分离的块。所述块中的每一者包括:体育场结构;填充沟槽,其竖直上覆于所述体育场结构且在所述体育场结构的水平边界内;支撑结构,其竖直延伸穿过所述填充沟槽及所述堆叠结构的所述层级中的至少一些;及介电衬层结构,其基本上覆盖所述支撑结构的侧壁。所述体育场结构包括阶梯结构,所述阶梯结构各自具有包括所述堆叠结构的所述层级中的至少一些的边缘的台阶。所述填充沟槽包括介电材料,所述介电材料插置在具有与所述介电材料不同的材料成分的至少两种额外介电材料之间。所述介电衬层结构包括所述介电材料的竖直位置处的第一突出部,及所述堆叠结构的所述层级中的所述至少一些的所述导电材料的竖直位置处的第二突出部。所述第二突出部具有大于所述第一突出部的水平尺寸。

2、在额外实施例中,一种形成微电子装置的方法包括形成包括布置成层级的牺牲材料及绝缘材料的竖直交替序列的初步堆叠结构。所述初步堆叠结构进一步包括体育场结构的行,所述行各自包括在第一水平方向上彼此相邻的所述体育场结构中的至少两者且各自包括具有包括所述初步堆叠结构的所述层级中的至少一些的边缘的台阶的阶梯结构。在所述体育场结构中的所述至少两者的所述阶梯结构的所述台阶上方形成介电衬层材料。使用采用大于或等于约630℃的温度的材料沉积工艺在所述介电衬层材料上方形成额外介电衬层材料。在所述额外介电衬层材料上方形成介电填充材料以基本上填充上覆于所述体育场结构中的所述至少两者且在所述体育场结构中的所述至少两者的水平区域内的沟槽。形成支撑结构以竖直延伸穿过所述介电填充材料、所述额外介电衬层材料、所述介电衬层材料及所述初步堆叠结构的所述层级中的所述至少一些。在形成所述支撑结构之后用导电材料替换所述初步堆叠结构的所述牺牲材料。

3、在进一步实施例中,一种存储器装置包括堆叠结构,所述堆叠结构包括各自包括导电材料及与所述导电材料竖直相邻的绝缘材料的层级,所述堆叠结构被划分成在第一方向上平行延伸且在第二方向上通过介电狭槽结构彼此分离的块。所述块中的每一者包括:体育场结构,其包括个别地具有包括所述堆叠结构的所述层级中的至少一些的水平端的台阶的相对阶梯结构;第一升高区,其在所述第一方向上与所述体育场结构的相对端相邻;及第二升高区,其在所述第二方向上与所述体育场结构的相对侧相邻,所述第二升高区的最上表面与所述第一升高区的最上表面基本上共面。所述存储器装置进一步包括所述堆叠结构的所述块内的电介质填充沟槽。所述电介质填充沟槽中的每一者竖直上覆于所述堆叠结构的所述块中的一者的所述体育场结构且在所述体育场结构的水平区域内。所述电介质填充沟槽中的每一者包括:氧化物衬层,其在所述体育场结构、所述第一升高区及所述第二升高区的表面上;氮化物衬层,其在所述氧化物衬层的表面上;及氧化物填充材料,其在所述氮化物衬层上方。所述存储器装置进一步包括竖直延伸穿过所述电介质填充沟槽到所述块中的每一者的所述体育场结构的所述台阶中的至少一些的导电接触件。所述导电接触件中的每一者被所述电介质填充沟槽中的一者的氮化物衬层水平包围且物理上接触所述氮化物衬层。所述存储器装置进一步包括竖直延伸穿过在所述第一方向上与所述体育场结构相邻的所述块中的每一者的一部分的存储器单元串。

4、在又进一步实施例中,一种电子系统包括:输入装置;输出装置;处理器装置,其可操作地耦合到所述输入装置及所述输出装置;及存储器装置,其可操作地耦合到所述处理器装置。所述存储器装置包括至少一个微电子装置结构,所述微电子装置结构包括包含布置成层级的导电材料及绝缘材料的竖直交替序列的堆叠结构。所述堆叠结构进一步包括通过至少一个介电结构分离的至少两个块。所述至少两个块中的每一者包括两个升高区、体育场结构及两个额外升高区。所述体育场结构在第一水平方向上插置在所述两个升高区之间且包括在所述第一水平方向上彼此相对的阶梯结构。所述阶梯结构各自具有包括所述堆叠结构的所述层级的边缘的台阶。所述两个额外升高区在垂直于所述第一水平方向的第二水平方向上与所述体育场结构的相对侧相邻。所述存储器装置进一步包括在所述堆叠结构的所述至少两个块上方且在所述至少两个块的水平边界内的填充沟槽。所述填充沟槽中的每一者包括:第一介电衬层材料,其在所述堆叠结构的所述至少两个块中的一者的所述体育场结构、所述两个升高区及所述两个额外升高区的表面上;第二介电衬层材料结构,其在所述第一介电衬层材料的表面上;及介电填充材料,其在所述第一介电衬层材料的表面上。所述存储器装置进一步包括竖直延伸穿过所述填充沟槽及所述堆叠结构的所述层级中的所述至少一些的支撑结构。所述存储器装置进一步包括介电衬层结构,其基本上覆盖所述支撑结构的侧壁且包括:第一突出部,其在所述第二介电衬层材料的竖直位置处;及第二突出部,其在所述堆叠结构的所述层级的所述导电材料的竖直位置处。所述第二突出部具有大于所述第一突出部的水平尺寸。导电接触结构水平插置在所述介电衬层结构之间且完全竖直延伸穿过所述填充沟槽。

- 还没有人留言评论。精彩留言会获得点赞!