一种全新的采样锁相环电路的制作方法

1.本发明涉及通信技术领域,特别是涉及一种全新的采样锁相环电路。

背景技术:

2.随着自动驾驶、云计算等各类新兴应用对高数据率和低延时的需求日益增长,无线通信系统正在使用更高阶的调制方案、更宽的信道带宽以及多输入多输出收发机来达到更高的吞吐量。更高的吞吐量则要求网络空间具有更高的传输速率,400g乃至800g光通信系统已经被提上了部署日程。为了达到误差矢量幅度(evm)要求的精度,本振(lo)的时钟抖动需要达到100fs以下,而超高速光通信系统也对时钟质量提出了类似的要求,因此,能够达到sub-100fs抖动的小数分频锁相环的设计成为一个关键点。

3.为了达到sub-100fs的抖动要求,各种降低锁相环相位噪声的技术相继被提了出来。采样锁相环(spll,sampling phase locked loops)作为一种可以有效地降低相位噪声的pll架构,在新的无线通信系统中得到了广泛的应用。与传统的锁相环不同,spll没有传统锁相环的pfd/cp噪声源,同时spll的采样鉴相器(spd)具有极高的增益,可以极大地抑制spd后面的采样电路的噪声,因此spll具有极佳的带内噪声特性。

4.传统的spll,采用spd获得参考时钟与vco分频后的时钟的相位差信息,将相位差转换成电压信号vsamp控制vco的比例电容,再将vsamp通过积分电路gm-c之后生成电压信号vc_slow用以控制vco的积分电容。为了解决spll频率捕获范围过窄的问题,需要额外附加一路pfd/cp环路用来增加其频率捕获范围。在小数分频spll中,为了解决频率切换时spd的线性度问题,需要使用数字校准电路校准需要使用数字校准电路去校准数字时间转换器(dtc)的增益,这需要数字化的相位差信息,但是传统的spll的实现方法在spd之后都是模拟电路,需要额外的比较器电路来提供数字化的相位差信息。额外的pfd/cp环路和比较器都增加了spll的设计复杂度,并增加了系统功耗。

技术实现要素:

5.本发明的目的是提供一种全新的采样锁相环电路,能够解决上述问题。

6.本发明提供的技术方案如下:在一些实施例中,本发明提供一种全新的采样锁相环电路,包括:采样锁相环主电路,用于接收外部参考信号后生成高频时钟;采样锁相环辅助电路,与所述采样锁相环主电路连接,用于为所述采样锁相环主电路提供零频率极点,并增加所述采样锁相环主电路的频率捕捉范围;其中,所述采样锁相环辅助电路包括:bbpd子电路,与所述采样锁相环主电路连接,用于基于所述外部参考信号,生成pe信号以供调整所述采样锁相环主电路的采样频率以及校准所述采样锁相环辅助电路中dtc子电路和fine dtc子电路的增益。

7.在一些实施例中,所述bbpd子电路包括:bbpd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出

端连接,用于接收所述外部参考信号和所述fbc信号,并对所述外部参考信号和所述fbc信号的跳变沿进行比较pfd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出端连接,与所述bbpd单元输出outp、outn连接,用于对bbpd单元的输出outp、outn进行重新采样生成pe信号up、dn,并在所述外部参考信号和所述fbc信号的相位差较大时对跳变沿进行比较;第一dff单元,与所述pfd单元、所述lms子电路连接,用于输出所述外部参考信号和所述fbc信号的比较信息至所述lms子电路。

8.在一些实施例中,当所述fbc信号和所述外部参考信号的比较信息中相位差超过预设阈值时,通过所述pfd单元调整频率的收敛速度,以增加所述频率捕捉范围.在一些实施例中,所述采样锁相环辅助电路,还包括:intg子电路、dac子电路、rc子电路;所述intg子电路,与所述dac子电路连接,用于基于接收到的所述pe信号生成数模控制信号并输出至所述dac子电路;所述dac子电路,与所述rc子电路连接,用于基于所述数模控制信号生成模拟控制电压并输出所述模拟控制电压至所述rc子电路;所述rc子电路,与所述采样锁相环主电路连接,用于衰减高频信号,将通过所述模拟控制电压调整所述采样锁相环主电路的采样频率。

9.在一些实施例中,所述采样锁相环辅助电路,还包括:finedtc子电路、dtc子电路、lms子电路、dsm子电路;所述dtc子电路,与所述finedtc子电路、所述lms子电路、所述dsm子电路、整数分频mmd子电路连接,用于对所述采样锁相环主电路的vco输出信号进行小数分频用于对所述外部参考信号进行小数分频。

10.在一些实施例中,还包括: 整数分频mmd子电路,与所述dsm子电路、所述lms子电路连接,用于对所述采样锁相环主电路的vco输出信号进行整数分频。

11.在一些实施例中,所述intg子电路,包括:fa单元、第二dff单元、dec单元;所述fa单元,与所述bbpd子电路、所述第二dff单元连接,用于接收所述pe信号并将所述pe信号与所述第二dff单元打拍后的信号相加;所述第二dff单元,与所述fa子电路、所述dec单元连接,用于打拍所述pe信号,并将打拍后的pe信号反馈至所述fa单元以形成积分器,并将所述fa信号输出至所述dec单元;所述dec单元,与所述dac子电路连接,用于对所述dff输出信号进行译码以输出dac输入数据至所述dac子电路。

12.在一些实施例中,所述采样锁相环主电路,包括:第一反相器、第二反相器、脉冲器、第一nmos管、第二nmos管、可变电阻器、第一开关、第二开关、第一电阻、第一电容、第二电容、第三电容、vco;所述第一反相器,与所述参考信号的输入端、所述第一开关连接脉冲器;所述脉冲器,与所述参考信号的输入端、所述第二开关连接所述第一反相器;所述第二反相器通过所述第一nmos管、第二nmos管、可变电阻器,与所述第一开关

连接;所述第一开关,与所述第一电容、所述第二开关连接;所述第二开关,与所述第二电容、所述第一电阻连接;所述第一电阻,与所述第三电容、所述vco连接。

13.在一些实施例中,所述采样锁相环辅助电路,还用于跟踪温度变化状态,当温度发生变化导致所述采样锁相环主电路的vco的频率发生变化时,通过输出所述pe信号以反向改变所述vco的频率。

14.在一些实施例中,当所述fbc信号和所述外部参考信号的比较信息中相位差超过预设阈值时,通过所述pfd单元调整频率的收敛速度,以增加所述频率捕捉范围。

15.本发明提供的一种全新的采样锁相环电路至少具有以下有益效果:1、本发明提出的采样锁相环电路,可以避免传统的spll spd只能提供模拟电压信号无法提供digital phase error的问题。

16.2、本发明提出的采样锁相环电路,可以增加spll的频率捕获范围,有效地降低spll的辅助环路复杂度的设计。

17.3、本发明提出的采样锁相环电路,可以有效地降低功耗,可以应用于高速、低功耗的应用场景。

附图说明

18.下面将以明确易懂的方式,结合附图说明优选实施方式,对一种全新的采样锁相环电路的上述特性、技术特征、优点及其实现方式予以进一步说明。

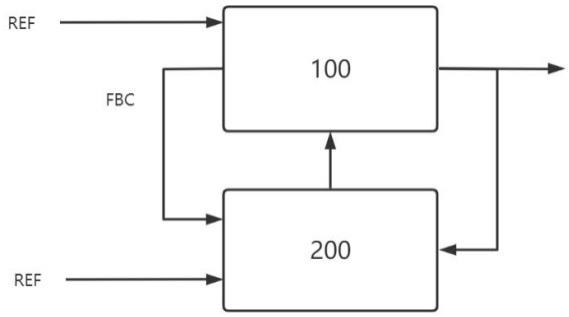

19.图1是本发明中的一种全新的采样锁相环电路的一个实施例的示意图;图2是本发明中的一种全新的采样锁相环电路的另一个实施例的原理图;图3是本发明中bbpd单元的原理图;图4是本发明中pfd单元的电路原理图;图5是本发明中vc_slow电路原理图;图6是传统采样锁相环电路的原理图。

具体实施方式

20.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,并获得其他的实施方式。

21.为使图面简洁,各图中只示意性地表示出了与本发明相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

22.在一个实施例中,如图1所示,本发明提供一种全新的采样锁相环电路,包括:采样锁相环主电路100,用于接收外部参考信号后生成高质量的高频时钟。

23.具体的,采样锁相环主电路100接收外部参考信号(ref),为内部的vco(压控振荡器)提供第一电压(vc)。

24.采样锁相环辅助电路200,与所述采样锁相环主电路连接,用于为所述采样锁相环主电路提供零频率极点,以增加所述采样锁相环主电路的频率捕捉范围。

25.其中,所述采样锁相环辅助电路包括:bbpd子电路,与所述采样锁相环主电路连接,用于基于所述外部参考信号,生成pe信号调整所述采样锁相环主电路的采样频率以及校准所述采样锁相环辅助电路中dtc子电路和fine dtc子电路的增益。

26.在本实施例中,通过添加采样锁相环辅助电路即一种全新的spll辅助环路,为spll增加频率捕捉范围,可以避免使用pfd/cp支路,从而降低了电路复杂度和功耗。

27.其中,本发明提出的spll辅助环路中含有bbpd子电路(bang-bang pd电路),可以提供digital phase error用于dtc gain calibration,避免传统的spll spd只能提供模拟电压信号无法提供digital phaseerror的问题。

28.示例性的,一类锁相环的目标频率是3g,所以一开始vco的频率需要为2.9g时才能振荡到3g。当有这个辅助环路后,辅助环路提供一个零频率极点,让一类锁相环变化为二类锁相环, vco的初始频率为2.8g时也能振荡到3g,提供一个更大的频率捕捉范围给vco,避免vco的频率捕捉范围固定在一类锁相环较小的捕捉频率范围内。

29.在一个实施例中,所述bbpd子电路包括:bbpd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出端连接,用于接收所述外部参考信号和所述fbc信号,并对所述外部参考信号和所述fbc信号的跳变沿进行比较;pfd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出端连接,与所述bbpd单元输出outp、outn连接,用于对bbpd单元的输出outp、outn进行重新采样生成pe信号up、dn,并在所述外部参考信号和所述fbc信号的相位差较大时对跳变沿进行比较;第一dff单元,与所述pfd单元、所述lms子电路连接,用于输出所述外部参考信号和所述fbc信号的比较信息至所述lms子电路。

30.具体的,如图3~4所示,所述bbpd子电路包括:bbpd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出端连接,用于接收所述外部参考信号和所述fbc信号,并对所述外部参考信号和所述fbc信号的跳变沿进行比较;pfd单元,与所述外部参考信号的输入端、所述采样锁相环主电路的fbc信号输出端连接,与所述bbpd单元输出outp、outn连接,用于对bbpd单元的输出outp、outn进行重新采样生成pe信号up、dn,并在所述外部参考信号和所述fbc信号的相位差较大时对跳变沿进行比较;第一dff单元,与所述pfd单元、所述lms子电路连接,用于输出所述外部参考信号和所述fbc信号的比较信息至所述lms子电路。

31.具体的,pfd单元为鉴频鉴相器,是一种新型的鉴相电路。它利用输入信号的跳变沿触发工作,属边缘控制数字式鉴频鉴相器。它既能鉴相又能鉴频。由于它只是对两个输入信号的跳变沿进行比较,因此对输入信号的占空比无固定要求。

32.第一dff单元,与所述pfd单元、所述lms子电路连接,用于输出所述外部参考信号和所述fbc信号的比较信息至所述lms子电路。

33.在本实施例中,如图3所示,本发明提出了一种高精度的bang-bang pd电路,当fbc=ref=0时 outp=outn=1,当fbc=1、ref=0时,outp=1、outn=0,当fbc=0、ref=1时,outp=0、outn=1,当fbc=1、ref=1时,outp/outn维持当前的状态。用采样时钟sck将outp/outn的结果采样出来即得到bbpd的差分输出(up/dn),up/dn端口信号中包含了fbc信号/ref信号的超前滞后信息,即digital phase error(pe信号),其中,pe信号是示意图上的标识,实际实现时是用up/dn来表示pe信号。将该pe信号送给lms算法模块进行计算,而无需在spd之后使用比较器进行电压比较。

34.其中,当fbc/ref的相位差比较大时,可以通过up1/dn1加快频率的收敛速度,同时增加了频率的捕获范围。

35.在一个实施例中,当所述fbc信号和所述外部参考信号的比较信息中相位差超过预设阈值时,通过所述pfd单元调整频率的收敛速度,以增加所述频率捕捉范围。

36.例如,fbc信号是3g时钟分频后得到一个低频频率,例如ref信号的频率为300mhz,vco输出信号的频率为3ghz,fbc信号的频率为300mhz。

37.本发明提出的spll辅助环路,可以有效地降低功耗,可以应用于高速、低功耗的应用场景。

38.在一个实施例中,还包括:intg子电路、dac子电路、rc子电路;所述intg子电路,与所述dac子电路连接,用于基于接收到的所述pe信号生成数模控制信号并输出至所述dac子电路;所述dac子电路,与所述rc子电路连接,用于基于所述数模控制信号生成模拟控制电压并输出所述模拟控制电压至所述rc子电路;所述rc子电路,与所述采样锁相环主电路连接,用于衰减高频信号,将通过所述模拟控制电压调整所述采样锁相环主电路的采样频率。

39.其中,intg子电路为积分器电路,dac子电路为多路数模转换器电路,rc子电路为rc滤波器电路。

40.具体的,通过积分器电路对bbpd产生的pe信号进行积分、编译输出控制信号至m路数模转换器电路,m路数模转换器电路将控制信号转换成m个可变电容的模拟控制电压,从而在较大范围内改变vco的频率。

41.本发明提出的spll辅助环路,可以增加spll的频率捕获范围,有效地降低spll的辅助环路复杂度的设计。

42.在一些实施例中,所述采样锁相环辅助电路,还包括:finedtc子电路、dtc子电路、lms子电路、dsm子电路;所述dtc子电路,与所述finedtc子电路、所述lms子电路、所述dsm子电路、整数分频mmd子电路连接,用于对所述采样锁相环主电路的vco输出信号进行小数分频用于对所述外部参考信号进行小数分频。

43.在一个实施例中,如图2所示,所述bbpd子电路,与所述lms子电路连接,用于基于所述外部参考信号,生成pe信号输出至所述lms子电路。

44.所述lms子电路,与dsm子电路、dtc子电路连接,用于根据接收到的pe信号调整dtc

子电路/fine dtc子电路的增益,以满足spd的线性度。

45.具体的,lms子电路包括运算lms算法的电路模块,通过将bbpd产生的digital phase error(pe)信号进行分析运算,对pe信号进行最小均方计算,得出频率校准信息,避免了在spd之后使用比较器进行电压比较,同样降低了功耗。

46.本发明提出的spll辅助环路,可以避免传统的spll spd只能提供模拟电压信号无法提供digital phase error的问题。

47.在一个实施例中,还包括: 整数分频mmd子电路,与所述dsm子电路、所述lms子电路连接,用于对所述采样锁相环主电路的vco输出信号进行整数分频。

48.具体的,所示dsm子电路为差分积分调制器 (delta-sigma modulator, delta-sigma调制器, dsm),控制分频比在不同参考时钟周期采用不同的整数值,这样其“平均”分频比就是一个非整数值。

49.差分积分调制器的作用是将输入模拟信号转换为由-1和1构成的串行数据。输出串行数据经过1位dac的放大后,与输入信号作差,误差信号送入积分累加,积分器的输出再送入1位adc产生新的1位数据流。当采样数据足够多时,调制器输出的1位数据流的平均值就等于输入信号的平均值,即1位数字流y(n)包含了输入信号的幅度信息。

50.另外,fcw信号为频率控制字,如果fcw信号是整数,则只需要整数分频,那么dsm子电路可以删除。

51.在一个实施例中,所述intg子电路,包括:fa单元、第二dff单元、dec单元;所述fa单元,与所述bbpd子电路、所述第二dff单元连接,用于接收所述pe信号并将所述pe信号与所述第二dff单元打拍后的信号相加;所述第二dff单元,与所述fa子电路、所述dec单元连接,用于打拍所述pe信号,并将打拍后的pe信号反馈至所述fa单元以形成积分器,并将所述fa信号输出至所述dec单元;所述dec单元,与所述dac子电路连接,用于对所述dff输出信号进行译码以输出dac输入数据至所述dac子电路。

52.具体的,本实施例提出了一种vc_slow的实现方式,所述fa单元和所述dff单元构成积分器,所述dec单元为译码器。其中,bbpd产生的pe信号被送到fa单元的输入端,fa单元的输出经过dff单元打拍后再返回到fa单元的另一个输入端从而形成积分器,积分器的输出经过译码器之后产生m路dac的控制信号,这些控制信号经过m路dac之后即可形成m个可变电容的模拟控制电压,从而在较大范围内改变vco的频率。

53.因为m路dac能够改变较大范围的vco频率,本发明提出的spll辅助环路还可以跟踪温度变化,当芯片的温度发生变化导致vco频率变化时,bbpd输出的pe信号可以通过dac反向改变vco的频率,从而抵消温度的影响。

54.综合上述情况,当pll正常工作时,在ref信号和fbc信号的相位差比较大的时候,pfd单元输出的up1/dn1信号会加速pll频率收敛的速度。当pll fbc的信号/ref信号的相位差比较小时,bbpd输出的up/dn信号会被用来更加精细地调节vco的增益,从而降低对sampling环路的增益要求。同时,up/dn会被用于dtc的校准算法,当系统温度变化时,bbpd支路也可以跟踪温度变化并调节vco的增益。

55.在一些实施例中,所述采样锁相环主电路,包括:第一反相器、第二反相器、脉冲器、第一nmos管、第二nmos管、可变电阻器、第一开关、第二开关、第一电阻、第一电容、第二

电容、第三电容、vco;所述第一反相器,与所述参考信号的输入端、所述第一开关连接脉冲器;所述脉冲器,与所述参考信号的输入端、所述第二开关连接所述第一反相器;所述第二反相器通过所述第一nmos管、第二nmos管、可变电阻器,与所述第一开关连接;所述第一开关,与所述第一电容、所述第二开关连接;所述第二开关,与所述第二电容、所述第一电阻连接;所述第一电阻,与所述第三电容、所述vco连接。

56.具体的,如图2所示,所述采样锁相环主电路100,包括:第一反相器a1、第二反相器a2、脉冲器t、第一nmos管n1、第二nmos管n2、可变电阻器r1、第一开关vs1、第二开关vs2、第一电阻r2、第一电容cs1、第二电容cs2、第三电容c2、vco(压控振荡器);所述第一反相器a1,与所述参考信号(ref)的输入端、所述第一开关vs1连接;所述脉冲器t,与所述参考信号(ref)的输入端、所述第二开关vs2连接;所述第二反相器a2通过所述第一nmos管n1、第二nmos管n2、可变电阻器r1,与所述第一开关vs1连接;所述第一开关vs1,与所述第一电容cs1、所述第二开关vs2连接;所述第二开关vs2,与所述第二电容cs2、所述第一电阻r2连接;所述第一电阻r2,与所述第三电容c2、所述vco连接。

57.在一个实施例中,所述采样锁相环辅助电路,还用于跟踪温度变化状态,当温度发送变化导致所述采样锁相环主电路的vco的频率发生变化时,通过输出所述pe信号以反向改变所述vco的频率。

58.在一个实施例中,所述采样锁相环辅助电路,还用于跟踪温度变化状态,当温度发生变化导致所述采样锁相环主电路的vco的频率发生变化时,通过输出所述pe信号以反向改变所述vco的频率。

59.在一个实施例中,本发明提供一种采样锁相环,包括:采样锁相环主电路、采样锁相环辅助环路;其中,采样锁相环辅助环路包括bbpd/intg/dac/rc,为spll提供了一个零频率的极点,使pll从i类锁相环变成了ii类锁相环。

60.需要说明的是,为了便于理解本发明的创新技术,对传统的spll进行介绍,如图6所示,传统的spll使用gm-c作为积分器来给spll提供一个低频极点,这个零频率的极点使spll从i类锁相环变成ii类锁相环,使得pll能够跟踪频率的变化。但是,因为这个低频极点位于spd的后面,它无法帮助spd提高频率捕捉范围,spll仍然需要一个pfd/cp环路提升其频率捕捉范围。同时因为spd支路上的信号都是模拟波形,需要一个额外的比较器产生digital phase error信号,用于dtc gain calibration。

61.与传统的结构相比,这种极点提供方式同时为spll增加了频率捕捉范围,可以避免使用pfd/cp支路,从而降低了电路复杂度和功耗。而且,bbpd产生了digital phase error(pe)信号,避免了在spd之后使用比较器,同样降低了功耗。bbpd输出的pe信号为dtc校准环路提供了输入信息,校准环路在校准了dtcgain之后,可以有效降低小数分频的跳频范围,减小了对spd线性工作范围的要求。

62.在本实施例中,所属领域的技术人员可以清楚地了解到,为了描述的方便和简洁,仅以上述各程序模块的划分进行举例说明,实际应用中,可以根据需要而将上述功能分配由不同的程序模块完成,即将所述装置的内部结构划分成不同的程序单元或模块,以完成以上描述的全部或者部分功能。实施例中的各程序模块可以集成在一个处理单元中,也可是各个单元单独物理存在,也可以两个或两个以上单元集成在一个处理单元中,上述集成的单元既可以采用硬件的形式实现,也可以采用软件程序单元的形式实现。另外,各程序模块的具体名称也只是为了便于相互区分,并不用于限制本技术的保护范围。

63.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详细描述或记载的部分,可以参见其他实施例的相关描述。

64.本领域普通技术人员可以意识到,结合本文中所公开的实施例描述的各示例的单元,能够以电子硬件、或者计算机软件和电子硬件的结合来实现。这些功能究竟以硬件还是软件来执行,取决于技术方案的特定应用和设计约束条件。专业技术人员可以对每个特定的应用来使用不同方法来实现所描述的功能,但是这种实现不应认为超出本技术的范围。

65.在本技术所提供的实施例中,应该理解到,所揭露的系统,可以通过其他的方式实现。示例性的,以上所描述的实施例仅仅是示意性的,示例性的,所述模块或单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,示例性的,多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通讯连接可以是通过一些接口,装置或单元的间接耦合或通讯连接,可以是电性、机械或其他的形式。

66.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

67.另外,在本技术各个实施例中的各功能单元可能集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

68.应当说明的是,上述实施例均可根据需要自由组合。以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1