latch电路、二三分频器及HS-MMD的制作方法

本发明涉及电路,尤其涉及一种latch电路、二三分频器及hs-mmd。

背景技术:

1、锁相环(phase locked loop,pll)被广泛应用于各种时钟电路中,用于提供其他芯片时钟基准与信号的调制解调。其中,反馈分频器(feedback divider)是锁相环环路内部的主要模块之一,其用于将压控振荡器(voltage control oscillator,vco)的高速信号分频,并将分频后的信号送入鉴频鉴相器(phase frequency detector,pfd),由pfd对分频后的信号与输入参考频率进行频率与相位的比较,不断调节vco频率,最终使pll环路锁定。

2、目前,通常使用多模分频器(multi modulus divider,mmd)作为反馈分频器,且需要额外设置高速预分频器先进行预分频后将信号输入至mmd。

3、但是,额外设置高速预分频器不利于pll的模块化集成,pll的集成程度低。

技术实现思路

1、本发明提供一种latch电路、二三分频器及hs-mmd,用以解决现有技术中pll的集成程度低的问题。

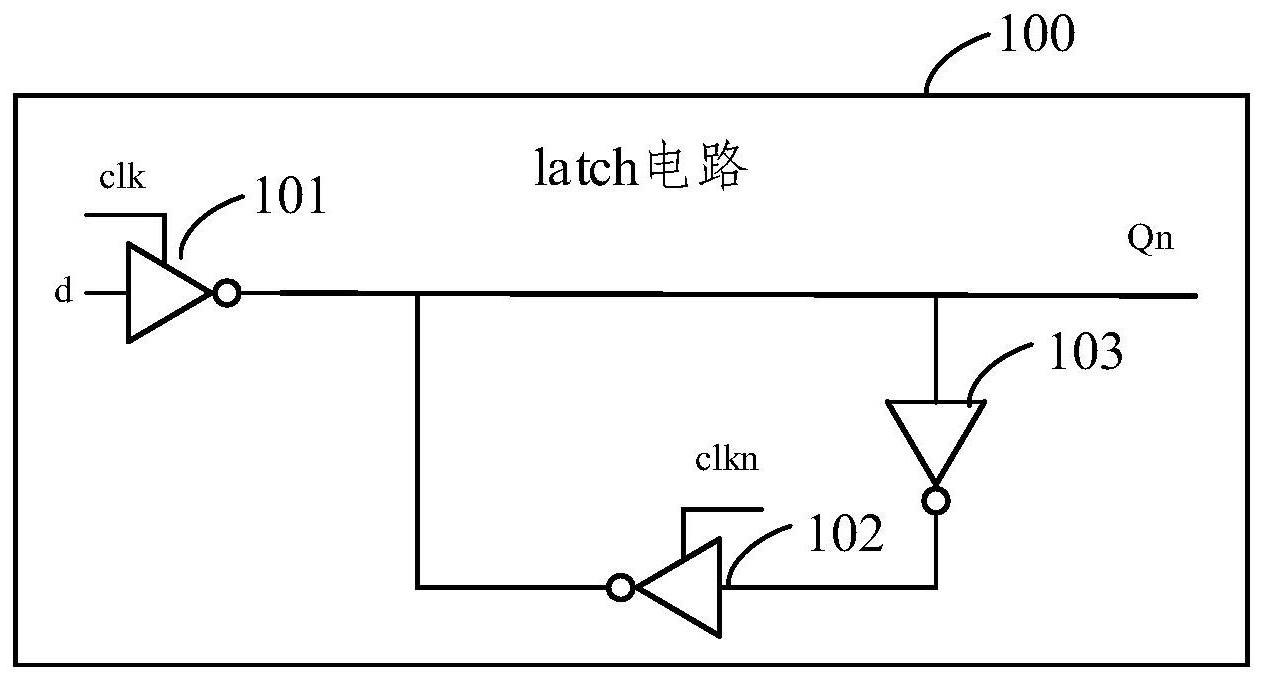

2、本发明提供一种锁存器latch电路,包括:第一三态门、第二三态门和第一反相器;

3、所述第一三态门的输入端作为所述latch电路的第一输入端,所述第一三态门的控制端作为所述latch电路的第二输入端,所述第一三态门的控制端用于接收第一时钟信号,所述第一三态门的输出端作为所述latch电路的输出端,所述第一三态门的输出端还连接于所述第一反相器的输入端,所述第一反相器的输出端连接于所述第二三态门的第一输入端,所述第二三态门的输出端连接于所述第一三态门的输出端,所述第二三态门的第二输入端用于接收第二时钟信号。

4、根据本发明提供的一种latch电路,所述latch电路还包括缓冲器;

5、所述第一三态门的输出端通过所述缓冲器作为所述latch电路的输出端。

6、根据本发明提供的一种latch电路,所述第一三态门、所述第二三态门和所述第一反相器中的至少一项采用了超低阈值电压ulvt类型的mos管。

7、本发明还提供一种基于锁存器latch电路的二三分频器,包括:

8、第一逻辑模块、第二逻辑模块、第三逻辑模块、第四逻辑模块、第一latch电路、第二latch电路、第三latch电路和第四latch电路,所述第一latch电路、所述第二latch电路、所述第三latch电路和所述第四latch电路为上述任一实施例所述的latch电路;

9、所述第一逻辑模块的第一输入端作为所述基于latch电路的二三分频器的输出端,所述第一逻辑模块的输出端连接于所述第一latch电路的第一输入端,所述第一latch电路的第二输入端用于接收第一时钟信号,所述第一latch电路的输出端连接于所述第二latch电路的第一输入端,所述第二latch电路的第二输入端用于接收第三时钟信号,所述第二latch电路的输出端连接于所述第二逻辑模块的输入端,所述第二逻辑模块的输出端连接于所述第一逻辑模块的第一输入端,所述第二latch电路的输出端还连接于所述第三逻辑模块的第一输入端,所述第三逻辑模块的第二输入端用于接收调整信号,所述第三逻辑模块的输出端连接于所述第三latch电路的第一输入端,所述第三latch电路的第二输入端用于接收所述第一时钟信号,所述第三latch电路的输出端连接于所述第四逻辑模块的第一输入端,所述第四逻辑模块的第二输入端用于接收控制信号,所述第四逻辑模块的输出端连接于所述第四latch电路的第一输入端,所述第四latch电路的第二输入端用于接收所述第三时钟信号,所述第四latch电路的输出端连接于所述第一逻辑模块的第二输入端。

10、根据本发明提供的一种基于latch电路的二三分频器,所述第一逻辑模块用于:在所述第一逻辑模块的第一输入端处于低电平,且所述第一逻辑模块的第二输入端处于低电平的情况下,通过所述第一逻辑模块的输出端输出高电平。

11、根据本发明提供的一种基于latch电路的二三分频器,所述第二逻辑模块用于:在所述第二逻辑模块的输入端处于低电平的情况下,通过所述第二逻辑模块的输出端输出高电平;在所述第二逻辑模块的输入端处于高电平的情况下,通过所述第二逻辑模块的输出端输出低电平。

12、根据本发明提供的一种基于latch电路的二三分频器,所述第三逻辑模块用于:在所述第三逻辑模块的第一输入端处于高电平,且所述第三逻辑模块的第二输入端处于高电平的情况下,通过所述第三逻辑模块的输出端输出低电平。

13、根据本发明提供的一种基于latch电路的二三分频器,所述第四逻辑模块用于:在所述第四逻辑模块的第一输入端处于高电平,且所述第四逻辑模块的第二输入端处于高电平的情况下,通过所述第四逻辑模块的输出端输出低电平。

14、根据本发明提供的一种基于latch电路的二三分频器,所述第一逻辑模块包括或非门;

15、所述或非门的第一输入端作为所述第一逻辑模块的第一输入端,所述或非门的第二输入端作为所述第一逻辑模块的第二输入端,所述或非门的输出端作为所述第一逻辑模块的输出端。

16、根据本发明提供的一种基于latch电路的二三分频器,所述第一逻辑模块包括与门和第二反相器;

17、所述与门的第一输入端作为所述第一逻辑模块的第一输入端,所述与门的第二输入端连接于所述第二反相器的输出端,所述第二反相器的输入端作为所述第一逻辑模块的第二输入端,所述与门的输出端作为所述第一逻辑模块的输出端。

18、根据本发明提供的一种基于latch电路的二三分频器,所述第二逻辑模块包括第三反相器;

19、所述第三反相器的输入端作为所述第二逻辑模块的输入端,所述第三反相器的输出端作为所述第二逻辑模块的输出端。

20、根据本发明提供的一种基于latch电路的二三分频器,所述第三逻辑模块包括第一与非门;

21、所述第一与非门的第一输入端作为所述第三逻辑模块的第一输入端,所述第一与非门的第二输入端作为所述第三逻辑模块的第二输入端,所述第一与非门的输出端作为所述第三逻辑模块的输出端。

22、根据本发明提供的一种基于latch电路的二三分频器,所述第四逻辑模块包括第二与非门;

23、所述第二与非门的第一输入端作为所述第四逻辑模块的第一输入端,所述第二与非门的第二输入端作为所述第四逻辑模块的第二输入端,所述第二与非门的输出端作为所述第四逻辑模块的输出端。

24、本发明还提供一种高速多模分频器hs-mmd,包括:串联连接的n个二三分频器,n为大于1的整数,所述n个二三分频器中的第一个二三分频器为上述任一实施例所述的基于latch电路的二三分频器。

25、本发明提供的latch电路、二三分频器及hs-mmd,由于相关技术中,需要额外设置高速预分频器先对来自vco的高速信号进行预分频后,将信号输入至mmd,这主要是因为mmd的传输延迟高,本发明实施例提供的latch电路,将相关技术中mmd的latch电路的传输路径上的反相器,设置在了latch电路的反馈支路上,在保证latch电路功能的基础上,有效降低了latch电路的传输延迟,进而有效降低了mmd的传输延迟,可以无需设置高速预分频器,mmd直接可以处理来自vco的信号,有利于pll的模块化集成,提高了pll的集成程度。

- 还没有人留言评论。精彩留言会获得点赞!