一种频率综合器的制作方法

1.本技术涉及射频技术领域,具体而言,涉及一种频率综合器。

背景技术:

2.频率综合器可以产生电子系统需要的各种形式的频率信号,在现代雷达、卫星通信和导航、射频与微波测试等领域被广泛应用,频率综合器合成的频率信号的质量可以影响电子系统的性能。面对复杂场景的应用需求,具有超宽带、小步进、低杂散、低相噪等特性的高信号质量的频率综合器能显著提升电子系统的性能。

3.现有技术中,频率合成主要包括直接频率合成、间接频率合成和数字频率合成三种合成方法,其中,直接频率合成技术通过倍频、分频、混频、滤波等方法得到所需的频率信号,具有硬件电路复杂、成本高、体积大、不便于集成、频带范围有限、输出信号杂散大等缺点;间接频率合成技术通过锁相环技术得到所需的频率信号,存在高分辨率和快转换速度之间的矛盾,一般用于大步进频率合成技术中;直接数字频率合成技术直接以离散时间的方式产生信号,通过改变幅度、频率和相位来生成被调制信号,存在工作频带窄、宽带杂散抑制性能较差的问题。

4.因此,采用单一的某种频率合成方法,无法满足复杂场景的需求。

技术实现要素:

5.本发明的目的在于,针对上述现有技术的不足,提供一种频率综合器,以解决现有技术中单一的某种频率合成方法无法满足复杂场景的需求的技术问题。

6.为实现上述目的,本技术实施例采用的技术方案如下:第一方面,本技术实施例提供一种频率综合器,该频率综合器包括:频标产生单元、参考产生单元、本振产生单元、混频锁相单元以及扩频单元;所述频标产生单元的第一输出端连接所述参考产生单元的输入端,所述频标产生单元的第二输出端连接所述本振产生单元的输入端,以向所述参考产生单元、所述本振产生单元输入输入信号;所述参考产生单元的输出端连接所述混频锁相单元的第一输入端,所述本振产生单元的输出端连接所述混频锁相单元的第二输入端,通过所述混频锁相单元输出扩展后的信号;所述混频锁相单元的输出端连接所述扩频单元的输入端,通过所述扩频单元输出扩大带宽的目标信号。

7.可选地,所述频标产生单元包括:晶振、第一谐波发生器、第一功分器、第一带通滤波器、第二带通滤波器、第三带通滤波器、第四带通滤波器、第一放大器、第二放大器、第三放大器、第四放大器;所述晶振连接所述第一谐波发生器的输入端,所述第一谐波发生器的输出端连接所述第一功分器的输入端,所述第一功分器的输出端分别连接所述第一带通滤波器、所述

第二带通滤波器、所述第三带通滤波器、所述第四带通滤波器,所述第一带通滤波器还连接所述第一放大器的输入端,所述第二带通滤波器还连接所述第二放大器的输入端,所述第三带通滤波器还连接所述第三放大器的输入端,所述第四带通滤波器还连接所述第四放大器的输入端;所述第一放大器的输出端与所述第二放大器的输出端为所述频标产生单元的第一输出端,所述第三放大器的输出端与所述第四放大器的输出端为所述频标产生单元的第二输出端。

8.可选地,所述参考产生单元包括:第一混频锁相环、输入电路、混频电路、第一分频器;所述第一放大器的输出端连接所述输入电路的输入端,所述输入电路的输出端连接所述第一混频锁相环的混频输入端;所述第二放大器的输出端连接所述混频电路的输入端,所述混频电路的输出端连接所述第一混频锁相环的射频输入端;所述第一混频锁相环的输出端连接所述第一分频器的输入端,所述第一分频器的输出端为所述参考产生单元的输出端。

9.可选地,所述第一混频锁相环包括:第一混频器、第一低通滤波器、第五放大器、第二低通滤波器、第一锁相环、第一环路滤波器、第一压控振荡器、耦合器、第一高通滤波器、第六放大器;所述第一混频器的第二输入端为所述第一混频锁相环的混频输入端;所述第一混频器的输出端依次通过所述第一低通滤波器和所述第五放大器连接所述第二低通滤波器,所述第二低通滤波器还连接所述第一锁相环的参考输入端,所述第一锁相环的输出端依次通过所述第一环路滤波器和所述第一压控振荡器连接所述耦合器的输入端,所述耦合器的第一输出端依次通过所述第一高通滤波器和所述第六放大器连接所述第一混频器的第一输入端;所述第一锁相环的射频输入端为所述第一混频锁相环的射频输入端,所述耦合器的第二输出端为所述第一混频锁相环的输出端。

10.可选地,所述混频电路包括:第二功分器、直接数字频率合成器、第五带通滤波器、第六带通滤波器、第七放大器、第二混频器、第七带通滤波器、第八放大器;所述第二功分器的输入端为所述混频电路的输入端;所述第二功分器的第一输出端依次通过所述第五带通滤波器和所述第七放大器连接所述第二混频器的第一输入端,所述第二功分器的第二输出端依次通过所述直接数字频率合成器和所述第六带通滤波器连接所述第二混频器的第二输入端;所述第二混频器的输出端通过所述第七带通滤波器连接所述第八放大器的输入端,所述第八放大器的输出端为所述混频电路的输出端。

11.可选地,所述本振产生单元包括:第一开关、第九放大器、第二谐波发生器、第二开关、第八带通滤波器、第九带通滤波器、第十带通滤波器、第三开关、第十放大器、第三低通滤波器;所述第一开关的一端为所述本振产生单元的输入端;所述第一开关的另一端依次通过所述第九放大器和所述第二谐波发生器连接所

述第二开关的一端,所述第二开关的另一端分别通过并联的所述第八带通滤波器、所述第九带通滤波器、所述第十带通滤波器连接所述第三开关的一端,所述第三开关的另一端通过所述第十放大器连接所述第三低通滤波器的输入端,所述第三低通滤波器的输出端为所述本振产生单元的输出端。

12.可选地,所述混频锁相单元包括:第二混频锁相环、第四低通滤波器、第十一放大器;所述第四低通滤波器的输入端为所述混频锁相单元的第一输入端;所述第四低通滤波器的输出端连接所述第二混频锁相环的射频输入端,所述本振产生单元的输出端连接所述第二混频锁相环的混频输入端;所述第二混频锁相环的输出端连接所述第十一放大器的输入端,所述第十一放大器的输出端为所述混频锁相单元的输出端。

13.可选地,所述第二混频锁相环包括:第二锁相环、第二环路滤波器、第二压控振荡器、二分频器、第二高通滤波器、第三混频器、第五低通滤波器、第十二放大器;所述第二锁相环的参考输入端为所述第二混频锁相环的射频输入端;所述第二锁相环的输出端通过所述第二环路滤波器连接所述第二压控振荡器的输入端,所述第二压控振荡器的第一输出端连接所述二分频器的输入端,所述二分频器的输出端通过所述第二高通滤波器连接所述第三混频器的第一输入端,所述第三混频器的输出端依次通过所述第五低通滤波器和所述第十二放大器连接所述第二锁相环的射频输入端;所述第三混频器的第二输入端为所述第二混频锁相环的混频输入端;所述第二压控振荡器的第二输出端为所述第二混频锁相环的输出端。

14.可选地,所述第二混频锁相环还包括:第三功分器;所述第二压控振荡器的输出端连接所述第三功分器的输入端,所述第三功分器的第一输出端为所述第二压控振荡器的第一输出端,所述第三功分器的第二输出端为所述第二压控振荡器的第二输出端。

15.可选地,所述扩频单元包括:第四开关、第二分频器、第一开关滤波器组、倍频器、第二开关滤波器组、第五开关;所述第四开关的一端为所述扩频单元的输入端;所述第四开关的另一端依次通过所述第二分频器和所述第一开关滤波器组连接所述第五开关的一端,所述第四开关的另一端还连接所述第五开关的一端,所述第四开关的另一端还依次通过所述倍频器和所述第二开关滤波器组连接所述第五开关的一端;所述第五开关的另一端为所述扩频单元的输出端。

16.相对现有技术而言,本技术具有以下有益效果:本技术提供的一种频率综合器,该频率综合器包括:频标产生单元、参考产生单元、本振产生单元、混频锁相单元以及扩频单元,频标产生单元的第一输出端连接参考产生单元的输入端,频标产生单元的第二输出端连接本振产生单元的输入端,以向参考产生单元、本振产生单元输入低杂散、低相噪的频标信号,参考产生单元的输出端连接混频锁相单元的第一输入端,以向混频锁相单元提供低杂散、低相噪、小步进、小带宽覆盖的参考信号,本振产生单元的输出端连接混频锁相单元的第二输入端,以向混频锁相单元提供低杂散、

低相噪、大步进的变频本振,混频锁相单元的输出端连接扩频单元的输入端,混频锁相单元通过混频锁相环技术将小带宽覆盖的参考信号扩展为较大带宽的宽带信号,同时保持低杂散、低相噪及小步进特性,扩频单元通过采用倍频滤波、分频滤波及直通等方式输出扩大带宽的目标信号,使得目标信号具备低杂散、低相噪、小步进特性,且在外部控制信号下可在超宽带的频率范围内按照可低至1hz的间隔实现任意频率的切换,以满足复杂场景的需求,降低对复杂场景中电子系统的性能的影响。

附图说明

17.为了更清楚地说明本发明实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本发明的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

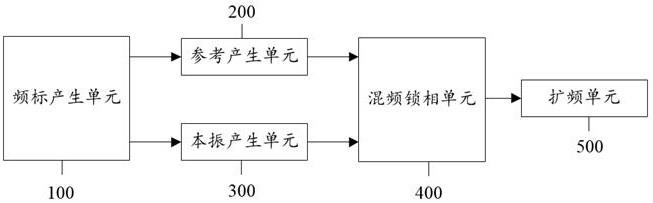

18.图1为本技术实施例提供的第一种频率综合器的结构示意图;图2为本技术实施例提供的第二种频率综合器的结构示意图;图3为本技术实施例提供的第三种频率综合器的结构示意图;图4为本技术实施例提供的第四种频率综合器的结构示意图;图5为本技术实施例提供的一种混频电路的结构示意图;图6为本技术实施例提供的第五种频率综合器的结构示意图;图7为本技术实施例提供的第六种频率综合器的结构示意图;图8为本技术实施例提供的第七种频率综合器的结构示意图;图9为本技术实施例提供的第八种频率综合器的结构示意图;图10为本技术实施例提供的第九种频率综合器的结构示意图。

19.图标:频标产生单元100;参考产生单元200;本振产生单元300;混频锁相单元400;扩频单元500;晶振101;第一谐波发生器102;第一功分器103;第一带通滤波器104;第二带通滤波器105;第三带通滤波器106;第四带通滤波器107;第一放大器108;第二放大器109;第三放大器110;第四放大器111;第一混频锁相环210;输入电路220;混频电路230;第一分频器240;第一混频器211;第一低通滤波器212;第五放大器213;第二低通滤波器214;第一锁相环215;第一环路滤波器216;第一压控振荡器217;耦合器218;第一高通滤波器219;第六放大器251;第二功分器231;直接数字频率合成器232;第五带通滤波器233;第六带通滤波器234;第七放大器235;第二混频器236;第七带通滤波器237;第八放大器238;第一开关301;第九放大器302;第二谐波发生器303;第二开关304;第八带通滤波器305;第九带通滤波器306;第十带通滤波器307;第三开关308;第十放大器309;第三低通滤波器310;第二混频锁相环410;第四低通滤波器420;第十一放大器430;第二锁相环411;第二环路滤波器412;第二压控振荡器413;二分频器414;第二高通滤波器415;第三混频器416;第五低通滤波器417;第十二放大器418;第三功分器419;第四开关501;第二分频器502;第一开关滤波器组503;倍频器504;第二开关滤波器组505;第五开关506。

具体实施方式

20.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例

中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本技术实施例的组件可以以各种不同的配置来布置和设计。

21.因此,以下对在附图中提供的本技术的实施例的详细描述并非旨在限制要求保护的本技术的范围,而是仅仅表示本技术的选定实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

22.在本发明的描述中,若出现术语“第一”、“第二”、“第三”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

23.需要说明的是,在不冲突的情况下,本发明的实施例中的特征可以相互结合。

24.现有技术中的频率合成包括直接频率合成、间接频率合成和数字频率合成,采用单一的某种频率合成技术,产生的信号无法满足复杂场景的需求,会降低复杂场景中电子系统的性能。

25.为了解决上述技术问题,本技术提供一种频率综合器,可以产生标准频率信号并对该标准频率信号进行处理,以获得扩大带宽的目标信号,使得该频率综合器可以实现超宽带频率覆盖,并且,该频率综合器输出的频率信号的步进小、相位噪声较低、杂散低,可以满足复杂场景中的需求,降低对复杂场景中电子系统的性能的影响。

26.如下通过具体示例,对本技术实施例所提供的一种频率综合器进行解释说明。图1为本技术实施例提供的第一种频率综合器的结构示意图,如图1所示,该频率综合器包括:频标产生单元100、参考产生单元200、本振产生单元300、混频锁相单元400以及扩频单元500。

27.频标产生单元100用于产生相同频率或者不同频率的频标信号,该频标信号可通过直接对高性能的标准频率信号进行倍频滤波的方式获得,具有低杂散、低相噪的特性。其中,频标信号还可以称为标准频率信号。

28.频标产生单元100存在两个输出端,可分别通过两个输入端输出频标信号。其中,频标产生单元100的第一输出端连接参考产生单元200的输入端,频标产生单元100的第二输出端连接本振产生单元300的输入端,以向参考产生单元200、本振产生单元300输入输入信号,该输入信号为频标信号,因此,参考产生单元200的输入端和本振产生单元300的输入端分别接收频标产生单元100输出的频标信号,其中,频标产生单元100的两个输出端可以输出相同频率的频标信号,还可输出不同频率的频标信号,在本技术实施例中不作具体限制。

29.参考产生单元200的输出端连接混频锁相单元400的第一输入端。参考产生单元200接收到频标产生单元100输出的低杂散、低相噪的频标信号之后,对该频标信号进行信号处理,该信号处理可以为直接数字频率合成(direct digital synthesis,dds)、混频、滤波、放大、分频、扩频等,以获得小步进、低杂散、低相噪、小带宽覆盖的输出信号,该输出信号可以作为混频锁相单元400的参考信号,以输入至混频锁相单元400进行信号处理。

30.本振产生单元300的输出端连接混频锁相单元400的第二输入端。本振产生单元300接收到频标产生单元100输出的低杂散、低相噪的频标信号之后,对该频标信号进行信号处理,该信号处理可以为扩频、滤波等,以获得低相噪、低杂散、大步进的输出信号,该输

出信号可以作为混频锁相单元400的本振信号(变频本振),以输入至混频锁相单元400进行信号处理。

31.混频锁相单元400通过第一输入端和第二输入端获得参考信号和本振信号之后,通过混频锁相单元400输出扩展后的信号。具体地,混频锁相单元400将输出扩展后的信号与本振信号进行混频得到一个差频信号,该差频信号与参考信号进行实时比相以产生一个反馈控制信号控制扩展后的信号,使得混频锁相单元400可以稳定输出扩展后的信号。由于参考信号为小步进、低杂散、低相噪、小带宽覆盖的信号,本振信号为低杂散、低相噪、大步进的信号,因此,混频锁相单元400输出的扩展后的信号为小步进、低杂散、低相噪、较大带宽的宽带信号。

32.可选地,该扩展后的信号可以为10~20ghz的小步进、低杂散、低相噪的单音输出信号。

33.混频锁相单元400的输出端连接扩频单元500的输入端,通过扩频单元500输出扩大带宽的目标信号。扩频单元500接收到混频锁相单元400输出的扩展后的信号后,可以对该信号进行分频滤波、倍频滤波、直通等操作,以输出扩大带宽的目标信号,该目标信号可以实现超宽带频率覆盖,同时,具备小步进、低杂散、低相噪特性。扩频单元500的输出端即为频率综合器的输出端,用于输出目标信号。

34.可选地,该扩大带宽的目标信号可以为0.625ghz~40.0ghz的小步进、低杂散、低相噪的单音输出信号。

35.本技术提供的一种频率综合器,本振产生单元向参考产生单元和本振产生单元输入本振信号,参考产生单元向混频锁相单元提供低杂散、低相噪、小步进、小带宽覆盖的参考信号,本振产生单元向混频锁相单元提供低杂散、低相噪、大步进的变频本振,混频锁相单元通过混频锁相环技术将小带宽覆盖的参考信号扩展为较大带宽的宽带信号,同时保持低杂散、低相噪及小步进特性,扩频单元通过采用倍频滤波、分频滤波及直通等方式输出扩大带宽的目标信号,使得目标信号可以实现超宽带频率覆盖,并且具备小步进、低杂散、低相噪特性,在外部控制信号下可在超宽带的频率范围内按照可低至1hz的间隔实现任意频率的切换,以满足复杂场景的需求,降低对复杂场景中电子系统的性能的影响。

36.在上述图1所示的第一种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图2为本技术实施例提供的第二种频率综合器的结构示意图,如图2所示,频标产生单元100包括:晶振101、第一谐波发生器102、第一功分器103、第一带通滤波器104、第二带通滤波器105、第三带通滤波器106、第四带通滤波器107、第一放大器108、第二放大器109、第三放大器110、第四放大器111。

37.晶振101连接第一谐波发生器102的输入端,在本技术实施例中,晶振101可以输出100mhz的低相噪参考信号,以驱动第一谐波发生器102产生100mhz的谐波信号。

38.第一谐波发生器102的输出端连接第一功分器103的输入端,第一功分器103的输出端分别连接第一带通滤波器104、第二带通滤波器105、第三带通滤波器106、第四带通滤波器107。第一功分器103将第一谐波发生器102的输出信号功分成四路,并分别进行滤波。

39.其中,第一带通滤波器104、第二带通滤波器105、第三带通滤波器106、第四带通滤波器107的滤波参数可以相同,以产生相同频率的频标信号,滤波参数还可以不同,以产生不同频率的频标信号。示例地,第一带通滤波器104可以滤波以取出频率为fbp1的频标信

号,fbp1可以为1.6ghz,第二带通滤波器105可以滤波以取出频率为fbp2的频标信号,fbp2可以为0.8ghz,第三带通滤波器106可以滤波以取出频率为fbp3的频标信号,fbp3可以为1.6ghz,第四带通滤波器107可以滤波以取出频率为fbp4的频标信号,fbp4可以为1.9ghz。

40.第一带通滤波器104还连接第一放大器108的输入端,第二带通滤波器105还连接第二放大器109的输入端,第三带通滤波器106还连接第三放大器110的输入端,第四带通滤波器还连接第四放大器111的输入端。其中,该多个放大器的放大参数相同,以将带内信号的幅度放大,方便后续的信号处理。

41.第一放大器108的输出端与第二放大器109的输出端为频标产生单元100的第一输出端,用于连接参考产生单元200的输入端,因此,频标产生单元100输入频率为fbp1和频率为fbp2的两路频标信号至参考产生单元200的输入端。

42.第三放大器110的输出端与第四放大器111的输出端为频标产生单元100的第二输出端,用于连接本振产生单元300的输入端,因此,频标产生单元100输入频率为fbp3和频率为fbp4的两路频标信号至频标产生单元300的输入端。

43.本技术实施例提供的一种频率综合器,频标产生单元,包括:晶振、第一谐波发生器、第一功分器、第一带通滤波器、第二带通滤波器、第三带通滤波器、第四带通滤波器、第一放大器、第二放大器、第三放大器、第四放大器,以产生低杂散、低相噪的频标信号,进而可将频标信号发送至参考产生单元和本振产生单元以对信号进行处理。

44.在上述图2所示的第二种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图3为本技术实施例提供的第三种频率综合器的结构示意图,如图3所示,参考产生单元200包括:第一混频锁相环210、输入电路220、混频电路230、第一分频器240。

45.第一放大器108的输出端连接输入电路220的输入端,以将频率为fbp1的信号输入至输入电路220,使得输入电路220对该信号进行滤波、放大等处理。

46.输入电路220的输出端连接第一混频锁相环210的混频本振输入端,该输入电路220的输出端的输出信号可以作为第一混频锁相环210中混频器的输入信号。

47.第二放大器109的输出端连接混频电路230的输入端,以将频率为fbp2的信号输入至混频电路230,使得混频电路230基于该信号生成更高频率的小步进、低杂散的单音输出信号。

48.混频电路230的输出端连接第一混频锁相环210的参考输入端,该混频电路230的输出端的输出信号可以作为第一混频锁相环210中锁相环的射频端的输入信号。

49.第一混频锁相环210接收到输入电路220的输出信号和混频电路230的输出信号之后,可以根据该两路信号,输出频率为预设频率的稳定的射频信号,该预设频率可以为n*fref。在本技术实施例中,fref的取值范围可以为103.125~111.25mhz。其中,n为第一分频器240的分频比,在本技术实施例中n可以为16。

50.第一混频锁相环210的输出端连接第一分频器240的输入端,第一分频器240的输出端为参考产生单元200的输出端。第一混频锁相环210输出频率为n*fref的信号后,第一分频器240对该信号进行分频,由于第一分频器240的分频比为n,则第一分频器240可以输出频率为fref的信号,该频率为fref的信号为参考产生单元200的输出信号,该输出信号具有小步进、低杂散、低相噪特性及较宽的频率覆盖。

51.本技术实施例提供的一种频率综合器,参考产生单元包括:第一混频锁相环、输入电路、混频电路、第一分频器,通过输入电路和混频电路接收频标产生单元输出的频标信号并对其进行滤波、混频、分频等处理,将处理之后的信号输入至第一混频锁相环,使得依次通过第一混频锁相环和第一分频器输出小步进、低杂散、低相噪、小带宽覆盖的信号。

52.在上述图3所示的第三种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图4为本技术实施例提供的第四种频率综合器的结构示意图,如图4所示,第一混频锁相环210包括:第一混频器211、第一低通滤波器212、第五放大器213、第二低通滤波器214、第一锁相环215、第一环路滤波器216、第一压控振荡器217、耦合器218、第一高通滤波器219、第六放大器251。

53.第一混频器211的第二输入端为第一混频锁相环210的混频本振输入端,用于接收输入电路220输出的信号。

54.在本技术实施例中,输入电路220包括一个带通滤波器和一个放大器,用于对频标产生单元100输出的频率为fbp4的频标信号进行滤波和放大,处理后的信号输入至第一混频器211的第二输入端,作为第一混频器211的本振信号,因此,该第一混频器211的第二输入端为第一混频器211的混频本振输入端。

55.第一混频器211的输出端依次通过第一低通滤波器212和第五放大器213连接第二低通滤波器214,第二低通滤波器214还连接第一锁相环215的参考输入端,使得输入电路220、第一混频器211、第一低通滤波器212、第五放大器213和第二低通滤波器214共同组成一个下变频链路,得到一路中频信号,输入至第一锁相环215的参考输入端,作为第一锁相环215的参考信号。

56.第一锁相环215的射频输入端为第一混频锁相环210的参考输入端,以接收混频电路230对频率为fbp2的信号进行混频后的输出信号,作为第一锁相环215的射频信号。

57.第一锁相环215的输出端依次通过第一环路滤波器216和第一压控振荡器217连接耦合器218的输入端,耦合器218的第一输出端依次通过第一高通滤波器219和第六放大器251连接第一混频器211的第一输入端。其中,第一锁相环215的参考输入端输入的为参考信号,第一锁相环215的射频输入端输入的为射频信号,第一锁相环215可以将射频信号进行预分频,并与参考信号进行实时比相,以控制第一压控振荡器217可以稳定输出频率为n*fref的射频信号。

58.耦合器218的第二输出端为第一混频锁相环210的输出端,该第二输出端为耦合器218的主路输出端,即第一压控振荡器217稳定输出的射频信号经过耦合器218的主路输出至第一分频器240进行分频,以得到频率为fref的信号。

59.在本技术实施例中,第一压控振荡器217的输出信号依次经过耦合器218、第一高通滤波器219、第六放大器251输入第一混频器211,进而使得第一压控振荡器217的输出信号,在下变频链路下变频,得到一路中频信号。

60.本技术实施例提供的一种频率综合器,第一混频锁相环包括:第一混频器、第一低通滤波器、第五放大器、第二低通滤波器、第一锁相环、第一环路滤波器、第一压控振荡器、耦合器、第一高通滤波器、第六放大器,通过第一锁相环对射频信号进行预分频,并与参考信号进行实时比相,以控制第一压控振荡器输出对应频率的稳定信号。

61.在上述图4所示的第四种频率综合器的结构示意图的基础上,本技术实施例还提

供了一种混频电路。可选地,图5为本技术实施例提供的一种混频电路的结构示意图,如图5所示,混频电路230包括:第二功分器231、直接数字频率合成器232、第五带通滤波器233、第六带通滤波器234、第七放大器235、第二混频器236、第七带通滤波器237、第八放大器238。

62.第二功分器231的输入端为混频电路230的输入端,以接收频标产生单元100输出的频率为fbp2的频标信号。

63.第二功分器231的第一输出端依次通过第五带通滤波器233和第七放大器235连接第二混频器236的第一输入端,使得对频率为fbp2的频标信号进行滤波和放大,该处理后的信号作为第二混频器236的本振信号。

64.第二功分器231的第二输出端依次通过直接数字频率合成器232和第六带通滤波器234连接第二混频器236的第二输入端。第二功分器231的第二输出端可将频率为fbp2的频标信号输入直接数字频率合成器232,作为直接数字频率合成器232的参考信号,使得直接数字频率合成器232产生频率为fdds的小步进、低杂散的单音输出信号,其中,fdds的取值范围可为50~75mhz,该单音输出信号输入至第二混频器236。

65.第二混频器236的输出端通过第七带通滤波器237连接第八放大器238的输入端,第八放大器238的输出端为混频电路230的输出端。第二混频器236对本振信号和该单音输出信进行混频,该混频可以为共频计算,混频之后的信号经过滤波、放大后得到输出频率为fbp2+fdds的小步进、低杂散的单音输出信号,以输入至第一锁相环215的射频输入端。

66.本技术实施例提供的一种混频电路,包括:第二功分器、直接数字频率合成器、第五带通滤波器、第六带通滤波器、第七放大器、第二混频器、第七带通滤波器、第八放大器,采用直接数字频率合成器实现小步进的频率覆盖(50~75mhz),进而得到输出频率为fbp2+fdds的小步进、低杂散的单音输出信号,以作为第一锁相环的射频输入信号。

67.在上述图2所示的第二种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图6为本技术实施例提供的第五种频率综合器的结构示意图,如图6所示,本振产生单元300包括:第一开关301、第九放大器302、第二谐波发生器303、第二开关304、第八带通滤波器305、第九带通滤波器306、第十带通滤波器307、第三开关308、第十放大器309、第三低通滤波器310。

68.第一开关301的一端为本振产生单元300的输入端,用于连接第三放大器110和第四放大器111的输出端,以接收频率为fbp3的频标信号和频率为fbp4的频标信号。其中,第一开关301为单刀双掷开关,每次只允许一种频率的频标信号通过,即第一开关301可以切换1.6ghz(fbp3)和1.9ghz(fbp4)的频标信号通过。

69.第一开关301的另一端依次通过第九放大器302和第二谐波发生器303连接第二开关304的一端。第一开关301的另一端输出频率为fbp3的频标信号或者频率为fbp4的频标信号,该信号经过第九放大器302进行放大后,驱动第二谐波发生器303产生fbp3或者fbp4的二次、三次和四次谐波。

70.具体地,若第一开关301切换1.6ghz(fbp3)的频标信号通过,则第二谐波发生器303可产生3.2ghz、4.8ghz和6.4ghz的信号;若第一开关301切换1.9ghz(fbp4)的频标信号通过,则第二谐波发生器303可产生3.8ghz、5.7ghz和7.6ghz的信号。

71.第二开关304的另一端分别通过并联的第八带通滤波器305、第九带通滤波器306、第十带通滤波器307连接第三开关308的一端,其中,第二开关304和第三开关308均为单刀

三掷开关。第二开关304和第八带通滤波器305、第九带通滤波器306、第十带通滤波器307、第三开关308可以组成一个开关滤波器组,该开关滤波器组可分别将3.2ghz、4.8ghz、6.4ghz、3.8ghz、5.7ghz或7.6ghz的单音信号滤波取出。

72.具体地,若第一开关301切换1.6ghz(fbp3)的频标信号通过,并且,若第二开关304连通第八带通滤波器305,则流经第三开关308的信号频率可为3.2ghz;若第二开关304连通第九带通滤波器306,则流经第三开关308的信号频率可为4.8ghz;若第二开关304连通第十带通滤波器307,则流经第三开关308的信号频率可为6.4ghz。

73.具体地,若第一开关301切换1.9ghz(fbp4)的频标信号通过,并且,若第二开关304连通第八带通滤波器305,则流经第三开关308的信号频率可为3.8ghz;若第二开关304连通第九带通滤波器306,则流经第三开关308的信号频率可为5.7ghz;若第二开关304连通第十带通滤波器307,则流经第三开关308的信号频率可为7.6ghz。

74.第三开关308的另一端通过第十放大器309连接第三低通滤波器310的输入端,第三低通滤波器310的输出端为本振产生单元300的输出端。滤波取出的单音信号经过放大、滤波(限制第十放大器309产生的谐波)后输入混频锁相单元400,为混频锁相单元400提供本振信号。

75.本技术实施例提供的一种频率综合器,本振产生单元包括:第一开关、第九放大器、第二谐波发生器、第二开关、第八带通滤波器、第九带通滤波器、第十带通滤波器、第三开关、第十放大器、第三低通滤波器,通过第二谐波发生器以及带通滤波器可以对输入至本振产生单元的信号的频率进行扩展以及滤波等,以得到低相噪、低杂散、大步进的输出信号,进而为混频锁相单元提供本振信号。

76.在上述图1所示的第一种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图7为本技术实施例提供的第六种频率综合器的结构示意图,如图7所示,混频锁相单元400包括:第二混频锁相环410、第四低通滤波器420、第十一放大器430。

77.第四低通滤波器420的输入端为混频锁相单元400的第一输入端,用于连接参考产生单元200,以对参考产生单元200输出的频率为fref的信号进行滤波。

78.第四低通滤波器420的输出端连接第二混频锁相环410的参考输入端,本振产生单元300的输出端连接第二混频锁相环410的混频本振输入端。参考产生单元200和本振产生单元300的输出信号作为第二混频锁相环410的输入信号,第二混频锁相环410可以根据该两路输入信号,经由外部的控制,输出特定频率范围的单音射频信号,该特定频率范围的信号可以为10~20ghz的单音信号。其中,第二混频锁相环410的参考输入端输入的射频信号为频率为fref的信号,fref的取值范围为103.125~111.25mhz,即通过第二混频锁相环410将射频输出信号频率范围扩宽至10~20ghz。

79.第二混频锁相环410的输出端连接第十一放大器430的输入端,第十一放大器430的输出端为混频锁相单元400的输出端。第二混频锁相环410输出稳定的信号后,对该信号进行放大,以将放大后的信号传输至扩频单元500。

80.本技术实施例提供的一种频率综合器,混频锁相单元包括:第二混频锁相环、第四低通滤波器、第十一放大器,可以通过第二混频锁相环控制输出更宽的频率覆盖范围的扩频信号,并经过第十一放大器放大后作为混频锁相单元的输出信号。

81.在上述图7所示的第六种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图8为本技术实施例提供的第七种频率综合器的结构示意图,如图8所示,第二混频锁相环410包括:第二锁相环411、第二环路滤波器412、第二压控振荡器413、二分频器414、第二高通滤波器415、第三混频器416、第五低通滤波器417、第十二放大器418。

82.第二锁相环411的参考输入端为第二混频锁相环410的参考输入端,用于接收第四低通滤波器420滤波之后的信号。

83.第二锁相环411的输出端通过第二环路滤波器412连接第二压控振荡器413的输入端,第二压控振荡器413的第一输出端连接二分频器414的输入端,二分频器414的输出端通过第二高通滤波器415连接第三混频器416的第一输入端。第二锁相环411控制第二压控振荡器413输出稳定的频率为10~20ghz的信号,第二压控振荡器413的第一输出端的信号经过分频器414后被分频为5~10ghz的信号,再通过第二高通滤波器415进行滤波。

84.第三混频器416的第二输入端为第二混频锁相环410的混频本振输入端,用于接收本振产生单元300输出的本振信号。第三混频器416接收到两路信号之后,对该两路不同频率的信号进行分段混频,混频后产生中频信号,该中频信号的频率范围保持在1.4ghz~2.6ghz。

85.第三混频器416的输出端依次通过第五低通滤波器417和第十二放大器418连接第二锁相环411的射频输入端。该中频信号经过第五低通滤波器417进行滤波,再经过第十二放大器418放大后,进入第二锁相环411的射频输入端,作为第二锁相环411的射频信号。

86.第二锁相环411接收到参考信号和射频信号之后,对射频信号进行预分频,并与参考信号进行实时比相,以控制第二压控振荡器413稳定输出频率为10~20ghz的射频信号。

87.第二压控振荡器413的第二输出端为第二混频锁相环410的输出端,用于稳定输出频率为10~20ghz的射频信号。

88.本技术实施例提供的一种频率综合器,第二混频锁相环包括:第二锁相环、第二环路滤波器、第二压控振荡器、二分频器、第二高通滤波器、第三混频器、第五低通滤波器、第十二放大器,通过第二锁相环对射频信号进行预分频,并与参考产生单元输出的参考信号进行实时比相,以控制第二压控振荡器输出特定频率的单音信号。

89.在上述图8所示的第七种频率综合器的结构示意图的基础上,本技术实施例还提供了另一种频率综合器。可选地,图9为本技术实施例提供的第八种频率综合器的结构示意图,如图9所示,第二混频锁相环410还包括:第三功分器419。

90.第二压控振荡器413的输出端连接第三功分器419的输入端,第三功分器419的第一输出端为第二压控振荡器413的第一输出端,第三功分器419的第二输出端为第二压控振荡器413的第二输出端。若第二压控振荡器413只有一个输出端时,可通过第三功分器419将其输出信号共分为两路,一路为第二压控振荡器413的第一输出端,用于连接二分频器414,另一路为第二压控振荡器413的第二输出端,用于连接第十一放大器430。

91.在本技术实施例中,该第三功分器419还可以为一个耦合器。

92.本技术实施例提供的一种频率综合器,第二混频锁相环还包括:第三功分器,以将第二压控振荡器的输出端分为两个,进而将第二压控振荡器的输出信号功分为两路信号。

93.在上述图1所示的第一种频率综合器的结构示意图的基础上,本技术实施例还提

供了另一种频率综合器。可选地,图10为本技术实施例提供的第九种频率综合器的结构示意图,如图10所示,扩频单元500包括:第四开关501、第二分频器502、第一开关滤波器组503、倍频器504、第二开关滤波器组505、第五开关506。

94.其中,第四开关501和第五开关506均为单刀三掷开关。第二分频器502为n分频器。

95.第四开关501的一端为扩频单元500的输入端,用于连接混频锁相单元400,以传输混频锁相单元400发送的稳定的10~20ghz的射频信号。

96.第四开关501的另一端依次通过第二分频器502和第一开关滤波器组503连接第五开关506的一端,以通过分频的方式将10~20ghz的输入信号进行分频。第二分频器502为n分频器时,n为2时,分频之后的信号的频率为5-10ghz,n为4时,分频之后的信号的频率为2.5-5ghz,n为8时,分频之后的信号的频率为1.25-2.5ghz,n为16时,分频之后的信号的频率为0.625-1.25ghz,因此,通过第二分频器502和第一开关滤波器组503组成的分频支路,可以保证信号在0.625~10ghz频率范围内的连续频率覆盖。

97.其中,第一开关滤波器组分6段对输出的0.625~10ghz信号进行滤波, 6段频率划分为:0.625~1.3ghz、1.3~2ghz、2~2.9ghz、2.9~4.3ghz、4.3~6.2ghz、和6.2~10ghz。

98.第四开关501的另一端还连接第五开关506的一端,组成直通支路,混频锁相单元400输出的10~20ghz的信号经第四开关501和第五开关506直通输出,以保证信号在10~20ghz的连续频率覆盖。

99.第四开关501的另一端还依次通过倍频器504和第二开关滤波器组505连接第五开关506的一端,组成倍频支路,倍频器504为二倍频器,以对混频锁相单元400输出的10~20ghz的信号进行二次倍频,保证信号在20~40ghz的连续频率覆盖。

100.其中,第二开关滤波器组505分4段对输出20~40ghz信号进行滤波,4段频率划分为:20~25ghz、25~29ghz、29~34.5ghz和34.5~40ghz。

101.第五开关506的另一端为扩频单元500的输出端,以输出0.625ghz~40ghz的目标信号,实现超宽带频率覆盖。

102.本技术实施例提供的一种频率综合器,扩频单元包括:第四开关、第二分频器、第一开关滤波器组、倍频器、第二开关滤波器组、第五开关,通过分频、倍频和直通三种方式,将10~20ghz的输入信号频率扩大至0.625ghz~40ghz,实现超宽带频率覆盖,同时,由开关滤波器组分段滤波的方式保证了-60dbc以下的低杂散输出,即目标信号的频率覆盖范围宽、跳频步进小、相位噪声和杂散低,只需要外部提供各个单元所需的控制信号,即可在0.625ghz~40.0ghz频带内按照可低至1hz的间隔实现任意频率切换,杂散抑制大于60dbc,相位噪声优于98dbc/hz@10khz(@40ghz)。

103.上仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1