半导体结构和芯片的制作方法

本公开涉及集成电路,具体而言,涉及一种能够降低版图布局面积的半导体结构以及应用该半导体结构的芯片。

背景技术:

1、在dram(dynamic random access memory,动态随机存取存储器)的版图布局中,包括存储单元区域(array),感应放大区域(sa)以及字线驱动区域(swd)。其中字线驱动区域主要负责为存储器的字线开启提供驱动电压。

2、字线驱动区域由数目巨大的重复的驱动单元组成,一个驱动单元包括一个pmos与一对nmos,即2n1p的结构。由于电路工作设计与需求,nmos与pmos必须相邻放置。而由于驱动单元的数量巨大,晶体管的数量巨大,占用了较大的版图布局面积。

3、随着芯片技术节点的前进,对器件尺寸的微型化要求越来越高,因此,需要针对晶体管数量众多的场景对dram的版图布局进行优化。

4、需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现思路

1、本公开的目的在于提供一种半导体结构与芯片,用于至少在一定程度上克服dram中大量晶体管占用大量版图布局面积的问题。

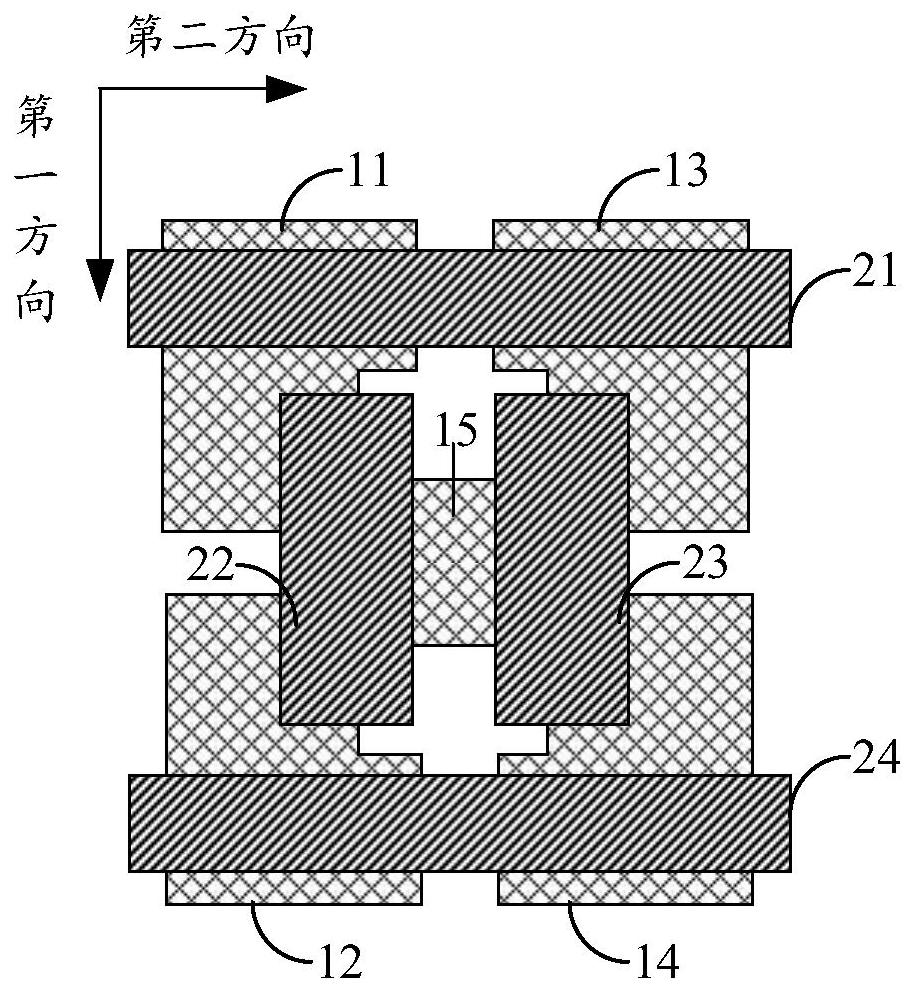

2、根据本公开的第一方面,提供一种半导体结构,包括:多个有源区,其中,第一有源区、第二有源区、第三有源区、第四有源区为阵列分布,所述第一有源区和所述第二有源区并列设置,所述第三有源区和所述第四有源区并列设置,所述第一有源区、第二有源区、第三有源区、第四有源区围绕并连接第五有源区,所述第五有源区用于接地;第一栅极介质区,连接所述第一有源区和所述第三有源区;第二栅极介质区,连接所述第一有源区、所述第二有源区、所述第五有源区;第三栅极介质区,连接所述第三有源区、所述第四有源区、所述第五有源区;第四栅极介质区,连接所述第三有源区和所述第四有源区。

3、在本公开的一种示例性实施例中,所述第一有源区和所述第二有源区延第一方向并列设置,所述第三有源区和所述第四有源区沿所述第一方向并列设置,所述第三有源区和所述第一有源区沿第二方向并列设置,所述第四有源区和所述第二有源区沿所述第二方向并列设置,所述第二方向与所述第一方向垂直。

4、在本公开的一种示例性实施例中,所述第一栅极介质区延所述第二方向延伸,所述第二栅极介质区延所述第一方向延伸,所述第三栅极介质区延所述第一方向延伸,所述第四栅极介质区延所述第二方向延伸。

5、在本公开的一种示例性实施例中,所述多个有源区在版图布局中位于第一层,所述第一栅极介质区、所述第二栅极介质区、所述第三栅极介质区、所述第四栅极介质区在所述版图布局中位于第二层。

6、在本公开的一种示例性实施例中,所述第一有源区和所述第一栅极介质区构成第一晶体管,所述第一有源区和所述第二栅极介质区、所述第五有源区共同构成第二晶体管;所述第三有源区和所述第一栅极介质区构成第三晶体管,所述第三有源区和所述第三栅极介质区、所述第五有源区共同构成第四晶体管;所述第二有源区和所述第四栅极介质区构成第五晶体管,所述第二有源区和所述第二栅极介质区、所述第五有源区共同构成第六晶体管;所述第四有源区和所述第二栅极介质区构成第七晶体管,所述第四有源区和所述第三栅极介质区、所述第五有源区共同构成第八晶体管。

7、在本公开的一种示例性实施例中,所述第一栅极介质区用于连接第一主字线,所述第四栅极介质区用于连接第二主字线,所述第二栅极介质区用于连接第一控制信号,所述第三栅极介质区用于连接第二控制信号;位于所述第一栅极介质区和所述第二栅极介质区之间的所述第一有源区用于连接第一子字线;位于所述第一栅极介质区和所述第三栅极介质区之间的所述第三有源区用于连接第二子字线;位于所述第四栅极介质区和所述第二栅极介质区之间的所述第二有源区用于连接第三子字线;位于所述第四栅极介质区和所述第三栅极介质区之间的所述第四有源区用于连接第四子字线;其中,所述第一子字线和所述第二子字线与所述第一主字线对应,所述第三子字线和所述第四子字线与所述第二主字线对应。

8、在本公开的一种示例性实施例中,所述第五有源区包括主体部分和第一桥、第二桥、第三桥、第四桥,其中,所述第一桥用于连接所述第一有源区和所述主体部分,所述第二桥用于连接所述第二有源区和所述主体部分,所述第三桥用于连接所述第三有源区和所述主体部分,所述第四桥用于连接所述第四有源区和所述主体部分,所述第一桥、所述第二桥连接所述第二栅极介质区,所述第三桥、所述第四桥连接所述第三栅极介质区。

9、在本公开的一种示例性实施例中,所述第一桥、所述第二桥、所述第三桥、所述第四桥均为矩形,且均沿所述第二方向延伸。

10、在本公开的一种示例性实施例中,所述第一桥、所述第二桥在所述第二方向上的长度小于所述第二栅极介质区在所述第二方向上的宽度,所述第三桥、所述第四桥在所述第二方向上的长度小于所述第三栅极介质区在所述第二方向上的宽度。

11、在本公开的一种示例性实施例中,所述第二栅极介质区同时连接所述第一有源区、所述第一桥、所述主体部分、所述第二桥、所述第二有源区;所述第三栅极介质区同时连接所述第三有源区、所述第三桥、所述主体部分、所述第四桥、所述第四有源区。

12、在本公开的一种示例性实施例中,所述第一有源区分为第一部分和第二部分,所述第一有源区的第一部分用于连接所述第一栅极介质区,所述第一有源区的第二部分用于连接所述第二栅极介质区;所述第二有源区分为第一部分和第二部分,所述第二有源区的第一部分用于连接所述第四栅极介质区,所述第二有源区的第二部分用于连接所述第二栅极介质区;所述第三有源区分为第一部分和第二部分,所述第三有源区的第一部分用于连接所述第一栅极介质区,所述第三有源区的第二部分用于连接所述第三栅极介质区;所述第四有源区分为第一部分和第二部分,所述第四有源区的第一部分用于连接所述第四栅极介质区,所述第四有源区的第二部分用于连接所述第三栅极介质区。

13、在本公开的一种示例性实施例中,所述第一有源区的第一部分、所述第二有源区的第一部分、所述第三有源区的第一部分、所述第四有源区的第一部分在第二方向上均具有第一宽度,所述第一有源区的第二部分、所述第二有源区的第二部分、所述第三有源区的第二部分、所述第四有源区的第二部分在第二方向上均具有第二宽度,所述第二宽度小于所述第一宽度。

14、在本公开的一种示例性实施例中,所述第一有源区的第一部分和所述第二有源区的第一部分在所述第一方向上具有第一边沿间距,所述第二栅极介质区在所述第一方向上的长度小于所述第一边沿间距;所述第三有源区的第一部分和所述第四有源区的第一部分在所述第一方向上具有第二边沿间距,所述第三栅极介质区在所述第一方向上的长度小于所述第二边沿间距。

15、在本公开的一种示例性实施例中,所述第二栅极介质区和所述第三栅极介质区在所述第一方向上的长度相等。

16、在本公开的一种示例性实施例中,还包括:第六有源区和第七有源区,在所述第二方向上与所述第一有源区、所述第三有源区并列设置,所述第六有源区和所述第七有源区均连接所述第一栅极介质区;第八有源区和第九有源区,在所述第二方向上与所述第二有源区、所述第四有源区并列设置,所述第八有源区和所述第九有源区均连接所述第四栅极介质区。

17、在本公开的一种示例性实施例中,所述第六有源区用于与所述第一栅极介质区共同构成第一p型晶体管,所述第七有源区用于与所述第一栅极介质区共同构成第二p型晶体管,所述第七有源区用于与所述第四栅极介质区共同构成第三p型晶体管,所述第八有源区用于与所述第四栅极介质区共同构成第四p型晶体管。

18、在本公开的一种示例性实施例中,所述第六有源区、所述第七有源区、所述第八有源区、所述第九有源区的形状相同,且均包括连接电源电压的第一部分和用以连接信号的第二部分,以及连接栅极介质区的第三部分。

19、在本公开的一种示例性实施例中,所述第六有源区的所述第二部分用于连接设置在所述第一有源区上的第一结点,所述第七有源区的所述第二部分用于连接设置在所述第三有源区上的第三结点,所述第八有源区的所述第二部分用于连接设置在所述第二有源区上的第二结点,所述第九有源区的所述第二部分用于连接设置在所述第四有源区上的第四结点;其中,所述第一结点位于所述第一有源区中所述第一栅极介质区、所述第二栅极介质区的连接位置之间,所述第二结点位于所述第二有源区中所述第一栅极介质区、所述第三栅极介质区的连接位置之间,所述第三结点位于所述第三有源区中所述第四栅极介质区、所述第二栅极介质区的连接位置之间,所述第四结点位于所述第四有源区中所述第四栅极介质区、所述第三栅极介质区的连接位置之间。

20、在本公开的一种示例性实施例中,所述第一结点、所述第二结点、所述第三结点、所述第四结点分别通过设置于第三层的信号线连接对应的有源区,所述第三层与所述多个有源区所在的层和所述第一栅极介质区所在的层属于不同层。

21、在本公开的一种示例性实施例中,所述第六有源区的第一部分、所述第七有源区的第一部分、所述第八有源区的第一部分、所述第九有源区的第一部分均相邻。

22、根据本公开的第二方面,提供一种芯片,其特征在于,包括如上任一项所述的半导体结构。

23、本公开实施例通过设置四个有源区环绕并连接第五有源区,并在第一方向上和第二方向上分别设置两个栅极介质区,可以通过五个有源区构成八个类型相同的晶体管,极大地降低集成电路中多个相同类型且有相互连接关系的晶体管的版图布局面积,可以有效降低芯片的整体体积。

24、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

- 还没有人留言评论。精彩留言会获得点赞!