倍频电路和电子设备的制作方法

本技术的实施例涉及信号处理,尤其涉及一种倍频电路和电子设备。

背景技术:

1、电子设备中广泛采用晶体振荡器(crystal oscillator,xo)作为参考时钟源,用以产生本地振荡信号(local oscillator,lo)。晶体振荡器凭借自身高稳定的振荡特性,能够减少电子设备发出的信号中的噪声,提升信号的质量。通常晶体振荡器与锁相环路(phase locked loop,pll)配合使用,锁相环路利用外部输入的参考信号,控制环路内部振荡信号的频率和相位,实现输出信号频率对输入信号频率的自动跟踪,以提高电子设备信号发射频率的稳定性。

2、随着技术的发展,高性能的电子设备需要高性能的锁相环路搭配高频率的晶体振荡器,而高频率的晶体振荡器的成本远高于低频率的晶体振荡器。

技术实现思路

1、本技术的实施例提供一种倍频电路和电子设备,用于在提供稳定的高频率振荡信号的基础上,降低电子设备的成本。

2、为达到上述目的,本技术采用如下技术方案:

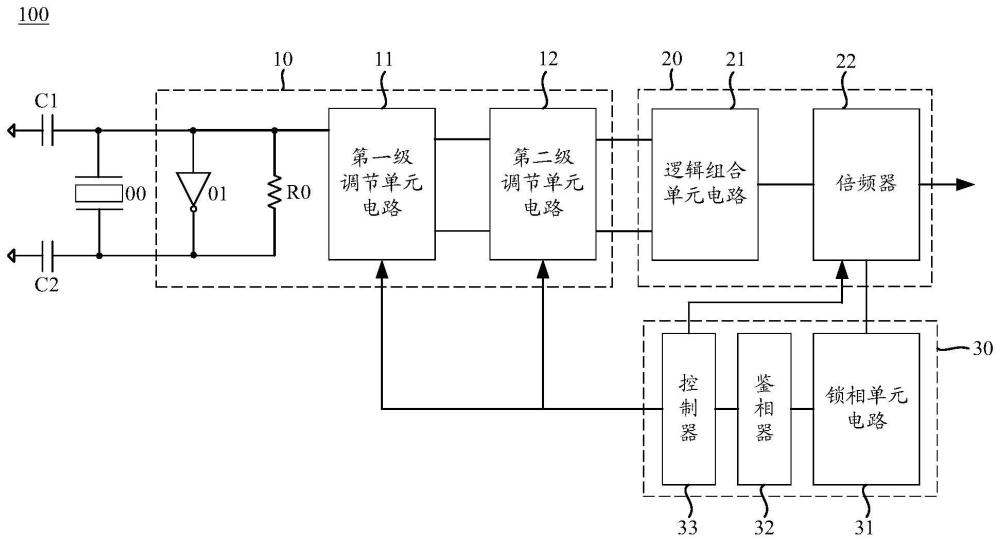

3、本技术实施例的第一方面,提供一种倍频电路。倍频电路包括占空比调节子电路、倍频合成子电路和校准子电路。占空比调节子电路与晶体振荡器耦接。占空比调节子电路被配置为输出n个预调制信号,其中,每个预调制信号的频率与晶体振荡器输出的正弦波信号的频率相同。n个预调制信号的占空比均小于或等于1/2,n为正整数。倍频合成子电路与占空比调节子电路耦接。倍频合成子电路被配置为基于n个预调制信号输出倍频信号。倍频信号的频率为预调制信号频率的2n倍。校准子电路与倍频合成子电路耦接,还分别与占空比调节子电路和倍频合成子电路耦接。校准子电路被配置为基于倍频信号的相位,向占空比调节子电路和倍频合成子电路输出调节信号,以使倍频合成子电路输出稳定的倍频信号。

4、倍频电路可以包括占空比调节子电路、倍频合成子电路和校准子电路。占空比调节子电路、倍频合成子电路和校准子电路依次耦接。

5、n个预调制信号可以包括占空比相等的多个预调制信号。示例性地,在一个正弦波信号的周期内,占空比调节子电路输出两个预调制信号,两个预调制信号的占空比相等。又示例性地,在一个正弦波信号的周期内,占空比调节子电路输出四个预调制信号,其中,两个预调制信号占空比相等,且与另外两个预调制信号的占空比不相等。

6、在n个预调制信号的占空比不全部相等的情况下,占空比最小的预调制信号的占空比可以为1/2n。示例性地,倍频电路输出8倍频信号,则占空比调节子电路输出的n个预调制信号中,占空比最小的预调制信号的占空比为1/8。

7、n个预调制信号的占空比均小于或等于1/2。示例性地,每个预调制信号的占空比均小于或等于1/2。可以理解地,在n个预调制信号的占空比不全部相等的情况下,占空比最大的预调制信号的占空比小于或等于1/2。

8、占空比调节子电路没有引入延时量大的外部信号,完全以晶体振荡器提供的正弦波信号作为输入,通过占空比调节子电路自身的结构对正弦波信号进行转换,得到n个预调制信号。因此预调制信号不会因外部信号引发较大的延时量,并且具有与晶体振荡器发出的正弦波信号相同或相近的高稳定性特点,从而能够便于提升基于预调制信号而得到倍频信号的稳定性。

9、校准子电路接收倍频信号,并对倍频信号进行校准处理,基于校准结果向占空比调节子电路和倍频合成子电路输出调节信号,实现对输出的倍频信号的负反馈控制,以使倍频合成子电路输出稳定的倍频信号。

10、可以理解地,倍频电路利用校准子电路实现对倍频信号的负反馈控制。示例性地,校准子电路分析倍频信号的相位得到调节信号,占空比调节子电路和倍频合成子电路基于调节信号调整信号输出,使得倍频信号的相位误差逐渐减小,倍频电路输出的倍频信号趋于稳定。

11、示例性地,调节信号可以包括第一调节子信号和第二调节子信号。准子电路向占空比调节子电路和倍频合成子电路输出调节信号,具体可以为:校准子电路向占空比调节子电路输出第一调节子信号,且校准子电路向倍频合成子电路输出第二调节子信号。占空比调节子电路可以基于第一调节子信号修正n个预调制信号的占空比。倍频合成子电路可以基于第二调节子信号修正n个预调制信号的频率合成,得到更精确的倍频信号。

12、校准子电路可以采用相位校准方式对倍频信号进行校准。通过相位校准方式对倍频信号进行校准,其校准精度能够优于采用电压控制校准方式对倍频信号进行校准。这样能够提升倍频信号的校准精度,进而提升倍频信号修正相位误差的效率,提高倍频电路输出的倍频信号的稳定性。

13、在第一方面的一些实施例中,占空比调节子电路包括至少两级调节单元电路。至少两级调节单元电路包括第一级调节单元电路和第二级调节单元电路。第一级调节单元电路与晶体振荡器耦接。第一级调节单元电路被配置为接收晶体振荡器输出的正弦波信号并输出n个第一信号。第一信号为方波信号,每个第一信号的频率与晶体振荡器输出的正弦波信号的频率相同。第二级调节单元电路与第一级调节单元电路耦接。第二级调节单元电路被配置为接收n个第一信号,并分别对n个第一信号的占空比进行调节后输出n个第二信号。

14、第一级调节单元电路可以包括一个输入端和n个输出端。第一级调节单元电路被配置为利用输入端接收晶体振荡器输出的正弦波信号,并利用n个输出端输出n个第一信号。第一信号为方波信号,每个第一信号的频率与晶体振荡器输出的振荡信号的频率相同。

15、第二级调节单元电路可以包括n个输入端和n个输出端。第二级调节单元电路的n个输入端可以与第一级调节单元电路的n个输出端一一对应耦接。第二级调节单元电路被配置为接收n个第一信号,并分别对n个第一信号的占空比进行调节后输出n个第二信号。

16、第二级调节单元电路可以对每个第一信号的占空比进行微调,得到相较于第一信号而言占空比更精确的第二信号。

17、在本实施例中,第二级调节单元电路输出的n个第二信号为n个预调制信号。可以理解地,第二级调节单元电路的n个输出端均与倍频合成子电路耦接。倍频合成子电路接收n个第二信号作为上述n个预调制信号,并基于n个第二信号输出倍频信号。

18、在第一方面的一些实施例中,第一级调节单元电路包括n个电压比较器。每个电压比较器分别与晶体振荡器、第一电源端和接地端耦接。每个电压比较器被配置为基于晶体振荡器输出的正弦波信号,输出一个第一信号。

19、电压比较器的第一控制端在正弦波信号的控制下,电压比较器的输出端分时输出高电位信号和低电位信号,从而使得电压比较器输出方波信号。例如,在正弦波信号的电位值大于0的半个周期内,电压比较器输出高电位信号;在正弦波信号的电位值小于0的半个周期内,电压比较器输出低电位信号。

20、另外,电压比较器的第二控制端还可以与校准子电路耦接。校准子电路输出的调节信号通过控制电压比较器的输出端在一个周期内输出的高电位信号与低电位之间的比例,可以调整第一信号的占空比。

21、在第一方面的一些实施例中,一个电压比较器包括第一晶体管、第二晶体管和第三晶体管。第一晶体管的控制极与晶体振荡器耦接,第一晶体管的第一极与第一电源端耦接,第一晶体管的第二极与第二级调节单元电路耦接。第二晶体管的控制极与晶体振荡器耦接,第二晶体管的第一极与第一晶体管的第二极耦接。第三晶体管的控制极与校准子电路耦接,第三晶体管的第一极与第二晶体管的第二极耦接,第三晶体管的第二极与接地端耦接。

22、正弦波信号控制第一晶体管处于导通状态且第二晶体管处于截止状态时,使得电压比较器的输出端与第一电源端之间导通,电压比较器的输出端输出的第一信号为高电位信号。

23、正弦波信号控制第一晶体管处于截止状态且第二晶体管处于导通状态时,电压比较器的输出端与第一电源端之间断开。此时存在第三晶体管处于截止状态和第三晶体管处于导通状态两种情况。在第三晶体管处于截止状态的情况下,电压比较器的输出端与接地端之间也断开,此时电压比较器的输出端处于无源状态,电压比较器的输出端保持上一阶段的电位,即电压比较器的输出端输出的第一信号仍旧为高电位信号。在第三晶体管处于导通状态的情况下,使得电压比较器的输出端与接地端之间导通,接地端下拉电压比较器的输出端的电位,电压比较器的输出端输出的第一信号为低电位信号。

24、由上所述可以看到,第三晶体管处于导通状态或截止状态,能够在一个周期中影响电压比较器的输出端输出的第一信号中高电位信号和低电位信号的比例,从而改变第一信号的占空比。因此,校准子电路可以与第三晶体管的控制极耦接,通过控制第三晶体管处于导通状态或截止状态来调节第一信号的占空比。

25、在第一方面的一些实施例中,第一级调节单元电路包括n个反相器。每个反相器分别与晶体振荡器、第二电源端和接地端耦接。其中,第二电源端为电压可调电源。每个反相器被配置为基于晶体振荡器输出的正弦波信号且调节第二电源端的电压值,输出第一信号。

26、反相器的输入端在正弦波信号的控制下,反相器的输出端分时输出可调电位信号和低电位信号。例如,在正弦波信号的电位值大于0的半个周期内,反相器输出可调电位信号;在正弦波信号的电位值小于0的半个周期内,反相器输出低电位信号。

27、另外,通过控制电压可调电源输出的可调电位信号的电位值的输出端在一个周期内输出的高电位信号与低电位之间的比例,可以调整第一信号的占空比。

28、在第一方面的一些实施例中,一个反相器包括第四晶体管和第五晶体管。第四晶体管的控制极与晶体振荡器耦接,第四晶体管的第一极与第二电源端耦接,第四晶体管的第二极与第二级调节单元电路耦接。第五晶体管的控制极与晶体振荡器耦接,第五晶体管的第一极与第二级调节单元电路耦接,第五晶体管的第二极与接地端耦接。

29、正弦波信号控制第四晶体管处于导通状态且第五晶体管处于截止状态时,使得反相器的输出端与第二电源端之间导通,反相器的输出端输出的第一信号为可调电位信号。

30、此时,可调电位信号可以提供高电位信号,也可以提供低电位信号。通过控制第二电源端输出的可调电位信号的电位值,能够调节第一信号中高电位信号和低电位信号之间的比例,从而调节第一信号的占空比。

31、正弦波信号控制第四晶体管处于截止状态且第五晶体管处于导通状态时,使得反相器的输出端与接地端之间导通,反相器的输出端输出的第一信号为低电位信号。

32、由上所述可以看到,在第四晶体管处于导通状态且第五晶体管处于截止状态的阶段,能够通过调节第二电源端输出的可调电位信号的电位值,可以在一个周期中影响反相器的输出端输出的第一信号中高电位信号和低电位信号的比例,从而改变第一信号的占空比。因此,校准子电路可以与第二电源端的控制端耦接,通过控制第二电源端输出的可调电位信号的电位值,来调节第一信号的占空比。

33、在第一方面的一些实施例中,第二级调节单元电路包括n个沟道比调节器。每个沟道比调节器与第一级调节单元电路耦接。每个沟道比调节器被配置为接收第一级调节单元电路输出的一个第一信号,并对第一信号的占空比进行调节输出一个第二信号。

34、利用沟道比调节器增加信号流经路径中p型沟道与n型沟道之间的比例,可以增加第一信号的下降沿延时时间,减小第一信号的上升沿延时时间。或者,利用沟道比调节器降低第一信号流经路径中p型沟道与n型沟道之间的比例,可以增加第一信号的上升沿延时时间,减小第一信号的下降沿延时时间。其中,p型沟道与n型沟道之间的比例与第一信号的下降沿延时时间正相关,并且p型沟道与n型沟道之间的比例与第一信号的上升沿延时时间负相关。

35、调整信号的上升沿延时时间和下降沿延时时间,能够改变信号内部高电位信号与低电位信号之间的比例,实现对信号的占空比进行微调。

36、本实施例中,通过沟道比调节器对每个信号流经路径中p型沟道与n型沟道之间的比例进行调节,能够对信号的上升沿延时时间和下降沿延时时间进行调整,进而改变信号内部高电位信号与低电位信号之间的比例,实现对第一信号的占空比进行微调,使得沟道比调节器输出的第二信号的占空比精度优于第一信号的占空比精度。

37、在第一方面的一些实施例中,每个沟道比调节器包括m个晶体管对。m为大于等于2的正整数。每个晶体管对包括第六晶体管和第七晶体管;其中,第六晶体管和第七晶体管中一者为p型晶体管且另一者为n型晶体管。n型晶体管的控制极与第一级调节单元电路耦接,n型晶体管的第一极通过第一开关与第三电源端耦接,n型晶体管的第二极与倍频合成子电路耦接。p型晶体管的控制极与第一级调节单元电路耦接,p型晶体管的第一极与倍频合成子电路耦接,p型晶体管的第二极通过第二开关与接地端耦接。

38、在第一开关和第二开关均处于闭合状态的情况下,一个晶体管对中一个晶体管处于导通状态且另一个晶体管处于截止状态。示例性地,在第一信号为高电位信号的阶段,作为n型晶体管的第六晶体管处于导通状态,作为p型晶体管的第七晶体管处于截止状态。此时,第六晶体管的第二极与第三电源端之间导通,第六晶体管的第二极输出第三电源端提供的高电位信号。在第一信号为低电位信号的阶段,作为n型晶体管的第六晶体管处于截止状态,作为p型晶体管的第七晶体管处于导通状态。此时,第六晶体管的第二极与接地端之间导通,下拉了第六晶体管的第二极的电位,第六晶体管的第二极输出低电位信号。

39、可以看到,在第一信号为高电位信号时,晶体管对也输出高电平信号;在第一信号为低电位信号时,晶体管对也输出低电平信号。

40、在晶体管对相连的第一开关处于断开状态且相连的第二开关处于闭合状态时,在第一信号为高电位信号的阶段,即使第六晶体管处于导通状态,第六晶体管的第二极与第三电源端之间仍断开,则该晶体管对无法输出高电位信号。而在第一信号为低电位信号的阶段,第七晶体管处于导通状态,第六晶体管的第二极与接地端之间导通,第六晶体管的第二极输出低电位信号。

41、尽管在第一信号为高电位信号的阶段,因为第一开关处于断开状态使得晶体管对无法输出高电位信号,但是由于m个晶体管对的输出端相互耦接,在其他晶体管对相连的第一开关处于闭合状态时,沟道比调节器整体仍旧输出高电位信号,不会对信号的电位造成影响。

42、并且,由于晶体管对相连的第一开关处于断开状态且相连的第二开关处于闭合状态,使得晶体管对输出的第二信号中增加了流经p型沟道的数量。

43、类似地,在晶体管对相连的第二开关处于断开状态且相连的第一开关处于闭合状态时,在第一信号为低电位信号的阶段,即使第七晶体管处于导通状态,第六晶体管的第二极与接地端之间仍断开,则该晶体管对无法输出低电位信号。

44、尽管在第二信号为低电位信号的阶段,因为第二开关处于断开状态使得晶体管对无法输出低电位信号,但是由于m个晶体管对的输出端相互耦接,在其他晶体管对相连的第二开关处于闭合状态时,沟道比调节器整体仍旧输出低电位信号,不会对信号的电位造成影响。

45、并且,由于晶体管对相连的第二开关处于断开状态且相连的第一开关处于闭合状态,使得晶体管对输出的第二信号中增加了流经n型沟道的数量。

46、在此基础上,通过调整m个晶体管对相连的m个第一开关处于闭合状态或断开状态的数量、以及m个晶体管对相连的m个第二开关处于闭合状态或断开状态的数量,可以调整第二信号流经的p型沟道和n型沟道的数量,进而调整第二信号流经的p型沟道与n型沟道之间的比例。

47、示例性地,m=10。将10个晶体管对相连的6个第一开关处于闭合状态且剩余4个第一开关处于断开状态,并且将10个晶体管对相连的2个第二开关处于闭合状态且剩余8个第二开关处于断开状态。这样,第二信号流经的p型沟道的数量为2个,第二信号流经的n型沟道的数量为6个,第二信号流经的p型沟道与n型沟道之间的比例为1/3。

48、本实施例中,可以通过调整m个晶体管对相连的m个第一开关处于闭合状态或断开状态的数量、以及m个晶体管对相连的m个第二开关处于闭合状态或断开状态的数量的方式,调整第二信号流经的p型沟道与n型沟道之间的比例,进而调整信号的占空比,使得沟道比调节器输出的第二信号的占空比精度优于第一信号的占空比精度。

49、在第一方面的一些实施例中,第一开关和第二开关分别与校准子电路耦接。在校准子电路输出调节信号的情况下,至少一个晶体管对中第一开关处于断开状态且第二开关处于闭合状态;或者至少一个晶体管对中第二开关处于断开状态且第一开关处于闭合状态。

50、示例性地,高电位的调节信号控制第一开关处于闭合状态,低电位的调节信号控制第一开关处于断开状态;高电位的调节信号控制第二开关处于断开状态,低电位的调节信号控制第二开关处于闭合状态。可以理解地,当m个调节信号均为高电位信号的情况下,m个第一开关处于闭合状态且m个第二开关处于断开状态,m个n型晶体管接入第二级调节单元电路的输出端。当m个调节信号均为低电位信号的情况下,m个第一开关处于断开状态且m个第二开关处于闭合状态,m个p型晶体管接入第二级调节单元电路的输出端。

51、同一个晶体管对相连的第一开关和第二开关可以通过同一信号线与校准子电路耦接。可以理解地,同一个晶体管对相连的第一开关和第二开关接收校准子电路提供的同一调节信号。

52、这样,校准子电路可以通过一个调节信号同时控制一个晶体管对相连的第一开关和第二开关,从而增加信号流经的一个p型沟道或n型沟道。基于这种方式,校准子电路可以通过m个调节信号同时控制一个第二级调节单元电路中m个晶体管对相连的m个第一开关和m个第二开关的状态,从而改变信号流经的p型沟道的数量与n型沟道的数量之间的比值,实现对第二信号的占空比的调节。

53、在第一方面的一些实施例中,至少两级调节单元电路还包括:第三级调节单元电路。第三级调节单元电路与第二级调节单元电路耦接。第三级调节单元电路被配置为接收n个第二信号,并分别对n个第二信号的相位进行调节后输出n个第三信号。

54、第三级调节单元电路可以包括n个输入端和n个输出端。第三级调节单元电路的n个输入端与第二级调节单元电路的n个输出端一一对应耦接。第三级调节单元电路被配置为接收n个第二信号,并分别对n个第二信号的相位进行调节后输出n个第三信号。

55、第三级调节单元电路可以对每个第二信号的相位进行微调,得到相较于第二信号而言信号相位更精确的第三信号。

56、在本实施例中,第三级调节单元电路输出的n个第三信号为n个预调制信号。可以理解地,第三级调节单元电路的n个输出端均与倍频合成子电路耦接。倍频合成子电路接收n个第三信号作为上述n个预调制信号,并基于n个第三信号输出倍频信号。

57、在第一方面的一些实施例中,第三级调节单元电路包括n个延时器。每个延时器分别与倍频合成子电路、第四电源端和接地端耦接;延时器被配置为接收第二信号,并对第二信号进行相位调整输出第三信号。

58、延时器的第一控制端在第二信号的控制下,延时器的输出端分时输出高电位信号和低电位信号。例如,在第二信号的电位值处于高电位的阶段内,延时器输出高电位信号;在第二信号的电位值处于低电位的阶段内,延时器输出低电位信号。

59、另外,延时器的第二控制端还可以与校准子电路耦接。校准子电路输出的调节信号通过控制延时器的延时量,调节延时器的输出端输出的第三信号的相位。

60、在第一方面的一些实施例中,每个延时器包括第八晶体管、第九晶体管、第十晶体管、第十一晶体管、电阻器和电容器。第八晶体管的控制极与第二级调节单元电路耦接,第八晶体管的第一极与第四电源端耦接,第八晶体管的第二极与电阻器的第一端耦接。第九晶体管的控制极与第二级调节单元电路耦接,第九晶体管的第一极与电阻器的第一端耦接,第九晶体管的第二极与接地端耦接。第十晶体管的控制极与电阻器的第二端耦接,第十晶体管的第一极与第四电源端耦接,第十晶体管的第二极与倍频合成子电路耦接。第十一晶体管的控制极与电阻器的第二端耦接,第十一晶体管的第一极与倍频合成子电路耦接,第十一晶体管的第二极与接地端耦接。电容器的第一极板与电阻器的第二端耦接,电容器的第二极板与接地端耦接。

61、其中,电阻器为可调电阻器,电阻器的控制端与校准子电路耦接;电阻器被配置为基于校准子电路提供的调节信号,调整电阻器的电阻值。电容器为可调电容器,电容器的控制端与校准子电路耦接;电容器被配置为基于校准子电路提供的调节信号,调整电容器的电容值。

62、示例性地,在第二信号为高电平信号的阶段,第八晶体管处于导通状态、第九晶体管处于截止状态。第八晶体管的第二极与第四电源端之间导通,第八晶体管的第二极输出高电平信号。这样,使得第十晶体管处于导通状态、第十一晶体管处于截止状态。第十晶体管的第二极与第四电源端之间导通,第十晶体管输出的第三信号为高电平信号。

63、在第二信号为低电平信号的阶段,第八晶体管处于截止状态、第九晶体管处于导通状态。第八晶体管的第二极与接地端之间导通,第八晶体管的第二极输出低电位信号。这样,使得第十晶体管处于截止状态、第十一晶体管处于导通状态。第十晶体管的第二极与接地端之间导通,第十晶体管输出的第三信号为低电位信号。

64、可以看到,延时器在第二信号为高电位信号的控制下也输出高电平信号;延时器在第二信号为低电位信号的控制下也输出低电平信号。

65、延时器中电阻器和电容器共同组成了延时电路。其中,电阻器为可调电阻器,电容器为可调电容器。电阻器的控制端与校准子电路耦接。电阻器被配置为基于校准子电路提供的调节信号,调整电阻器的电阻值。电容器的控制端与校准子电路耦接;电容器被配置为基于校准子电路提供的调节信号,调整电容器的电容值。

66、通过改变电阻器的电阻值和/或电容器的电容值,调整第三信号相对于第二信号的延时量,从而调整第三信号的相位延时量,使得延时器可以对每个第二信号的相位进行微调,得到相较于第二信号而言信号相位更精确的第三信号。

67、在第一方面的一些实施例中,倍频合成子电路包括逻辑组合单元电路和倍频器。逻辑组合单元电路与占空比调节子电路耦接。逻辑组合单元电路被配置为基于n个预调制信号,输出初倍频信号。初倍频信号的频率为预调制信号的频率的n倍。倍频器与逻辑组合单元电路耦接。倍频器被配置为基于初倍频信号,输出倍频信号;倍频信号的频率为初倍频信号的频率的2倍。

68、逻辑组合单元电路被配置为接收占空比调节子电路提供的n个预调制信号,并基于n个预调制信号输出初倍频信号。初倍频信号的频率为预调制信号的频率的n倍。示例性地,占空比调节子电路提供4个25mhz的预调制信号,逻辑组合单元电路基于4个25mhz的预调制信号,输出1个100mhz的初倍频信号。

69、倍频器被配置为接收逻辑组合单元电路提供的初倍频信号,并基于初倍频信号输出倍频信号。倍频信号的频率为初倍频信号的频率的2倍。示例性地,逻辑组合单元电路提供1个100mhz的初倍频信号,倍频器基于该100mhz的初倍频信号输出200mhz的倍频信号。

70、本实施例中,倍频合成子电路利用逻辑组合单元电路将n个预调制信号进行整合,形成n倍频的初倍频信号,再利用倍频器对初倍频信号进行倍频处理得到2n倍频的倍频信号。这样,能够利用晶体振荡器提供的高稳定性的正弦波信号,得到频率为正弦波信号的频率2n倍的方波信号。

71、在第一方面的一些实施例中,倍频器包括延时单元和异或逻辑单元。延时单元与逻辑组合单元电路耦接。延时单元被配置为接收初倍频信号,并对初倍频信号进行相位调整输出次倍频信号。异或逻辑单元分别与逻辑组合单元电路和延时单元耦接。异或逻辑单元被配置为基于初倍频信号和次倍频信号,输出倍频信号。

72、在一些实施例中,逻辑组合单元电路可以为单一的逻辑门电路。在另一些实施例中,逻辑组合单元电路也可以为多个逻辑门电路。

73、在第一方面的一些实施例中,逻辑组合单元电路包括异或门逻辑电路。

74、在第一方面的一些实施例中,校准子电路包括:锁相单元电路、鉴相器和控制器。锁相单元电路与倍频合成子电路耦接。锁相单元电路被配置为对倍频信号进行锁相处理,输出目标倍频信号。鉴相器分别与倍频合成子电路和锁相单元电路耦接。鉴相器被配置为对倍频信号和目标倍频信号进行比较,输出比较结果。控制器与鉴相器耦接,还分别与占空比调节子电路和倍频合成子电路耦接。控制器被配置为基于比较结果,分别向占空比调节子电路和倍频合成子电路输出调节信号。

75、锁相单元电路被配置为对倍频信号进行锁相处理,滤除倍频信号的周期抖动以输出更稳定的目标倍频信号。鉴相器被配置为比较倍频合成子电路提供的倍频信号和锁相单元电路提供的目标倍频信号,输出比较结果。

76、在一些示例中,控制器的输出端包括多个子输出端,每个子输出端输出一个控制子指令。可以理解地,调节信号包括多个控制子指令。

77、在一些示例中,控制器可以对鉴相器提供的比较结果进行分析,得出多个分析结果。示例性地,多个分析结果包括占空比分析结果、相位延迟分析结果等。控制器基于多个分析结果可以得到多个控制子指令,其中,多个分析结果和多个控制子指令一一对应。

78、示例性地,控制器的输出端包括第一子输出端、第二子输出端、第三子输出端和第四子输出端。调节信号包括第一控制子指令、第二控制子指令、第三控制子指令和第四控制子指令。控制器的第一子输出端输出第一控制子指令,控制器的第二子输出端输出第二控制子指令,控制器的第三子输出端输出第三控制子指令,控制器的第四子输出端输出第四控制子指令。

79、在第一方面的一些实施例中,锁相单元电路包括锁相环路或倍增延迟锁定环路。

80、本技术实施例的第二方面,提供一种电子设备。该电子设备包括如上第一方面任一实施例中的倍频电路。

81、可以理解地,上述提供的任一电子设备,均可以由上文所提供的对应的倍频电路来实现,或与上文所提供的对应的倍频电路相关联,因此,其所能达到的有益效果可参考上文所提供的倍频电路中的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!