基于硅掺杂碲化锗的选通管器件及其制备方法

本发明属于选通管器件,涉及一种选通管器件,具体涉及一种基于硅掺杂碲化锗的选通管器件及其制备方法。

背景技术:

1、近些年来,伴随着大数据、5g通信、人工智能、云计算等高新技术的兴起,所需存储和读取的信息量也是不断增加,因此需要性能更加优良的存储器来满足这些新兴技术对数据存储的需求。目前商用的主流半导体存储器是浮栅结构的闪存(flash)存储器,然而近年来,浮栅闪存存储器除了在特征尺寸上有缩小之外,在其他方面并没有特别大的改进。当前的浮栅闪存存储器的特征尺寸已经缩小到了纳米级别,此时由于面临许多理论和技术上的限制,尺寸难以进一步缩小;同时其平面集成架构也难以进一步提高存储密度来满足人们对存储信息量的需求。

2、相变存储器(pcm)因为具有良好的可扩展性、低能耗、快速转换速度、较长的耐受时间和简单的器件结构等优点,与浮栅闪存存储器相比具有明显优势,被认为是最适合三维集成的新型存储器之一,并且已经在2017年成功商用。但是由于pcm存在漏电流串扰的问题,研发一种选通管器件是解决该问题的关键。

3、目前,人们基于各种材料开发出了基于不同特性的选通管器件,如基于vo2,nbo2的金属绝缘体转变(mit)的选通管器件;基于混合离子电子导电(miec)的至少含有一个惰性电极的选通管器件;基于绝缘的超线性阈值(slm)介质的场辅助超线性阈值(fast)选通管器件;基于金属导电细丝形成和断裂的可编程金属化选通管器件。但是上述选通管器件都存在难以和pcm集成的缺点。其中,双向阈值开关(ots)的选通管器件是两端结构,其结构简单且可扩展性好,独特的双极对称性使得在集成后读取和写入数据时没有极性的限制。ots凭借优秀的综合性能,被视为与pcm集成的最佳器件。

4、目前的ots选通管器件主要基于硒(se)、锗(ge)的化合物体系,其中基于碲(te)的二元化合物材料简单,实现了较小的阈值电压。然而,用现有的技术所制造出来的ots选通管器件在制作完成后大多都需要forming过程使器件从初始状态转变到高阻态以达到激活器件的目的,激活后器件才表现出基于易失性的阈值转变,具有选择性功能,而这增加了存储器电路操作的复杂性。同时,由于forming过程通常都需要加一个大电压,这还可能使ots选通管器件的电阻产生不可预测的变化,并且大电压还可能还会降低器件的耐受性。因此,研究出一种不需要forming过程(forming-free)的ots选通管器件就成为了研究的重要目标。

技术实现思路

1、本发明的目的,是要提供一种基于硅掺杂碲化锗的选通管器件,避免了较大的forming电压对选通管器件内部结构不可逆转的损伤,并增加了选通管器件的稳定性和耐受性,扩大了选通管器件的应用范围;

2、本发明的另一个目的,是要提供上述基于硅掺杂碲化锗的选通管器件的一种制备方法,通过采用磁控溅射技术,用硅掺杂的碲化锗薄膜作为转换层,制备了具有forming-free特性的基于ots的选通管器件。

3、本发明为实现上述目的,所采用的技术方案如下:

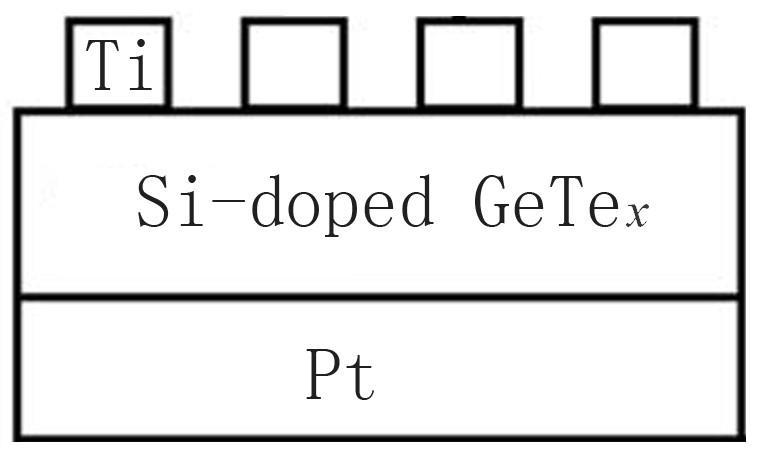

4、一种基于硅掺杂碲化锗的选通管器件,所述基于硅掺杂碲化锗的选通管器件从下至上依次为:底电极,转换层,顶电极;

5、所述底电极的材料为pt,转换层的材料为硅掺杂的碲化锗薄膜,顶电极的材料为ti,转换层中硅和碲化锗的摩尔比为1:40~50。

6、作为限定,所述底电极的厚度为150~250 nm,形状为矩形,边长为50~300 μm。

7、作为第二种限定,所述转换层的厚度为50~140 nm,转换层的形状与底电极相同。

8、作为第三种限定,所述顶电极的厚度为30 ~70 nm,形状为矩形或圆形,边长或直径为50~300 μm。

9、本发明还提供了上述基于硅掺杂碲化锗的选通管器件的一种制备方法,包括以下步骤:

10、s1、对所述底电极进行预处理;

11、s2、在所述底电极表面制备转换层;

12、s3、在所述转换层远离底电极一侧的表面制备顶电极;

13、所述底电极的材料为pt,转换层的材料为硅掺杂的碲化锗薄膜,顶电极的材料为ti,转换层中硅和碲化锗的摩尔比为1:40~50。

14、作为限定,步骤s1对所述底电极进行预处理的具体过程为:

15、s11、通过无水乙醇将pt基底的pt导电面擦洗干净,并用去离子水冲洗,然后分别用去离子水,丙酮,无水乙醇超声清洗30~40 min;

16、s12、将清洗干净的pt基底吹干,在基底的一侧边缘处贴上绝缘胶带,形成预留底电极。

17、作为第二种限定,步骤s2在所述底电极表面制备转换层的具体过程为:

18、s21、在磁控溅射设备上分别安装碲化锗靶和硅靶,在设备的真空室中通入惰性气体氩气;

19、s22、将步骤s1的底电极置于磁控溅射设备中,开启磁控溅射电源,控制真空室内的系统压力为0.1~0.6 pa、温度为250~300 k,碲化锗靶的溅射功率设为10~30 w,硅靶的溅射功率为3~10 w,两个靶同时开始溅射,溅射时间为1800~4200 s,沉积完毕后,关闭磁控溅射电源。

20、作为进一步限定,碲化锗靶采用射频磁控溅射,硅靶采用射频溅射。

21、作为第三种限定,步骤s3在所述转换层远离底电极一侧的表面制备顶电极的具体过程为:

22、s31、在磁控溅射设备上分别安装金属钛靶,在设备的真空室中通入惰性气体氩气;

23、s32、将步骤2得到的转换层置于磁控溅射设备中,开启磁控溅射电源,控制真空室内的系统压力为0.1~0.6 pa、温度为250~300 k,溅射功率为30~40 w,溅射时间为1800~4200 s,沉积完毕后,关闭磁控溅射电源。

24、作为进一步限定,金属钛靶采用直流磁控溅射法。

25、本发明由于采用了上述的技术方案,其与现有技术相比,所取得的技术进步在于:

26、(1)本发明的选通管器件用硅掺杂的碲化锗薄膜作为转换层,在阈值电压和保持电压上都相比于未掺杂硅的碲化锗选通管器件都有所减小,对于集成电路而言,可以极大地缓解外围电路的设计压力和功耗;

27、(2)本发明的选通管器件避免了较大的forming电压对选通管器件内部结构不可逆转的损伤,使得选通管器件的状态更容易判断,测试也更加容易;并增加了选通管器件的稳定性和耐受性,扩大了应用范围;

28、(3)本发明采用磁控溅射技术,用硅掺杂的碲化锗薄膜作为转换层,制备了具有forming-free特性的基于ots的选通管器件;

29、(4)本发明制备的选通管器件具有forming-free特性,从电路设计的角度来看,利用具有forming-free特性的选通管器件进行集成,减少了电路设计中的高压电源模块和施加在器件上的限流模块,极大地简化了电路,降低了电路设计的要求。

30、综上所述,本发明适用于制备基于硅掺杂碲化锗的选通管器件,经硅掺杂碲化锗的选通管器件具有forming-free特性,由于免除了forming过程器件的稳定性和耐受性都得到改善。

- 还没有人留言评论。精彩留言会获得点赞!