一种高速采样器电路、一种高速采样器及采样方法与流程

本发明属于集成电路设计,涉及一种高速采样器电路、一种高速采样器及采样方法。

背景技术:

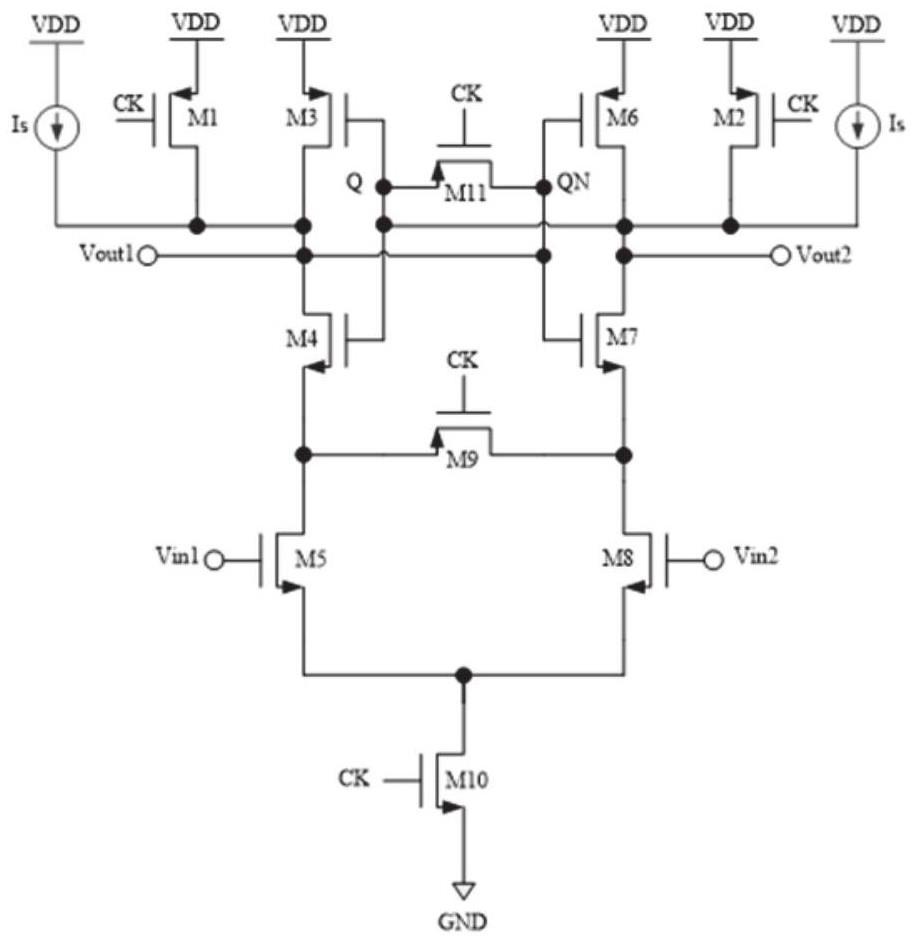

1、高速采样器作为时钟数据恢复的核心电路,用来对已均衡的差分模拟信号进行采样,得到正确的数字信号。可以理解为一个模数转换电路,在可以接收模拟差分信号的接收器/比较器或者可以接收单端信号的接收器/比较器中广泛应用。评价采样电路性能的指标主要有采样敏感度和充放电速度。采样敏感度是指采样器能够正确采出数据的最小输入差模值,充放电速度指采样器工作时,信号高低电平转换所需要的时间。采样器决定着均衡后的数据是否能被正确识别。传统的采样器电路结构如图1所示,其主要完成对差分数据vin1和vin2的采样。电路工作主要分为2个阶段:预充和采样。在图1中,采样器处于预充阶段时,ck为低电平,m1、m2和m9导通,m10关断,将vout1和vout2预充到vdd,差分输出均为高电平。在采样阶段,ck从低电平跳变到高电平,m1、m2和m9关断,m10导通。在采样的初始阶段,由于vout1和vout2为高电平,所以m3和m6关断,m4和m7打开,通过m5和m8对vin1和vin2的数据进行采样和放大。由于vin1和vin2为一对差分数据,所以必然有一路的放电速度大于另外一路。不妨假设某一时刻,vin1>vin2,因此,m4、m5和m10构成的放电回路强于m7、m8和m10构成的放电回路,所以vout1会被优先拉到低电平,当vout1为低电平时,m6打开,m7关断,将vout2拉高到高电平vdd,通过反馈,vout1将被进一步拉低到gnd,即vin1>vin2,vout1=0,vout2=vdd;当vin1<vin2,vout1=vdd,vout2=0,完成对差分信号的采样和放大。

2、对于高速采样器而言,这种差分结构的采样电路最主要的是在电位预充阶段保持电路的对称均衡,在采样阶段则需保证数据输入管除数据值的输入差异外无其他干扰存在。在空间辐射环境中,卫星所处的轨道环境中存在着大量高能带电粒子。近年的研究结果表明,随着集成电路技术的不断发展,器件的特征尺寸进入到纳米级别,其电源电压和节点电容也不断减小,使得集成电路对粒子辐照的敏感性增强。传统的采样器在面向空间应用时,会受到来自高能宇宙射线的辐射。高能宇宙射线与构成mos器件的材料相互作用产生大量的电子空穴对,电子空穴对被器件的敏感节点收集,就会诱发单粒子效应,造成器件功能异常或者逻辑状态改变,威胁航天器的在轨运行。因此当传统高速采样器在粒子辐照下运行时,在电位预充阶段保持电路的对称均衡会被干扰,影响到时钟进行准确采样,若set发生的位置和时刻正好处于采样器的敏感节点的敏感时间窗口,则会直接导致采样结果出错。

3、在高速采样器的预充阶段,由于单粒子效应的影响,使得差分电路两端预充电位不等,从而影响采样的放电过程。现有的针对传统采样器预充阶段的抗辐射加固技术如图2所示,(硕士论文:高速相位插值型时钟数据恢复电路的set加固设计,谭佳伟,国防科技大学研究生院,2017年),在q和qn节点增加一个pmos晶体管m11,其栅极连接到ck信号,源极连接到q节点,漏极连接到qn节点。该晶体管在预充阶段导通,在采样阶段关闭,这样就能保证预充电压的对称性。当添加短路管m11后,在预充阶段将保持m4和m7漏端的电压相等,同步充电到高电位。在预充阶段,m4和m7晶体管位置遭受单粒子轰击,则单边晶体管所收集到的电荷将经由短路的传输管传递到另外一边,保证预充过程两边预充电压的平衡。然而,该方法在采样阶段并不能增强采样器的抗辐射性能。

技术实现思路

1、针对现有技术中存在的问题,本发明提供一种高速采样器电路、一种高速采样器及采样方法,从而有效解决现有技术中采样器在采样过程中无法有效抵抗粒子辐射的技术问题。

2、本发明是通过以下技术方案来实现:

3、一种抗辐射加固高速采样器电路,包括pmos管m1,pmos管m2,pmos管m3,pmos管m6,pmos管m11,pmos管m9,nmos管m4,nmos管m7,nmos管m5,nmos管m8,nmos管m10,电流源is1以及电流源is2;

4、所述pmos管m1,pmos管m3,pmos管m2以及pmos管m6的源极接电源电压vdd;所述pmos管m1以及pmos管m3的漏极接差分输出vout1,所述pmos管m2以及pmos管m6的漏极接差分输出vout2;所述pmos管m1以及pmos管m2的栅极接时钟信号ck;

5、所述nmos管m4的漏极接差分输出vout1,栅极接pmos管m3的栅极,源极接nmos管m5的漏极;

6、所述nmos管m7的漏极接差分输出vout2,栅极接pmos管m6的栅极,源极接nmos管m8的漏极;

7、所述nmos管m5的栅极接差分输入vin1,所述nmos管m8的栅极接差分输入vin2,所述nmos管m5与m8源极均接nmos管m10的漏极;所述nmos管m10的源极接地,栅极接时钟信号ck;

8、所述pmos管m11的源极接pmos管m3以及nmos管m4的栅极,栅极接时钟信号ck,漏极接pmos管m6以及nmos管m7的栅极;

9、所述pmos管m9的源极接nmos管m4的源极以及nmos管m5的漏极,栅极接时钟信号ck,漏极接nmos管m7的源极以及nmos管m8的漏极;

10、所述电流源is1以及电流源is2的一端均接电源电压vdd,电流源is1的另一端接差分输出vout1,电流源is2的另一端接差分输出vout2。

11、优选的,所述电流源is1与电流源is2均为二极管,所述两个二极管的正极均接电源电压vdd,负极分别接差分输出vout1以及差分输出vout2。

12、优选的,所述电流源is1与电流源is2均为pmos管,所述两个pmos管的源极均接电源电压vdd,漏极分别接差分输出vout1以及差分输出vout2。

13、优选的,所述电流源is1与电流源is2均为nmos管,所述两个nmos管的源极分别接差分输出vout1以及差分输出vout2,漏极以及栅极均接电源电压vdd。

14、优选的,所述电流源is1与电流源is2均为电阻。

15、优选的,所述作为电流源is1与电流源is2的电阻的阻值相同。

16、优选的,所述电流源is1与电流源is2均为pnp型三极管或均为npn型三极管;当所述电流源is1与电流源is2均为pnp型三极管时,所述两个pnp型三极管的发射极均接电源电压vdd,一个pnp型三极管的集电极以及基极均接差分输出vout1,另一个pnp型三极管的集电极以及基极均接差分输出vout2;当所述电流源is1与电流源is2均为npn型三极管时,所述两个npn型三极管的发射极分别接差分输出vout1以及差分输出vout2,两个npn型三极管的集电极以及基极均接电源电压vdd。

17、一种高速采样器,包括上述的抗辐射加固高速采样器电路。

18、上述的高速采样器在接收器或比较器中的应用。

19、上述高速采样器的采样方法,包括预充阶段和采样阶段;在所述预充阶段,ck为低电平,m1、m2和m9导通,m10关断;在所述采样阶段,ck为高电平,m1、m2、m9和m11关断,m10导通。

20、与现有技术相比,本发明具有以下有益的技术效果:

21、本发明公开一种高速采样器电路、一种高速采样器及采样方法,该高速采样器电路设计有两个等效的电流源is,用来补偿粒子辐照引起的节点vout1和vout2的扰动,在本发明的电路结构中,在采样过程中,如果有粒子轰击到m7的漏极区区域,产生辐射光电流,m7的漏极连接到vout2,此状态下,vout2=vdd,m7为nmos管,其衬底接gnd,在漏极与衬底之间建立通路,将使vout2的电压降低,增加的is电流源将给vout2节点充电,将vout2电位重新拉到vdd,等效于增大了该电路结构的抗单粒子翻转对的临界电荷,增加了该结构在采样过程中的抗辐射性能。

- 还没有人留言评论。精彩留言会获得点赞!