一种低通滤波器及设备的制作方法

本发明涉及滤波器,具体地涉及一种低通滤波器及设备。

背景技术:

1、目前,在物联网高速发展的背景下,便携式或可穿戴设备应用广泛。而在这些设备中,低通滤波器是信息获取过程中的关键电路模块,其承担滤除杂波和提供一定增益的功能。当前主要有以下两种低通滤波器实现方式。

2、1)连续时间滤波,其常采用电阻或跨导与电容构造传输函数来实现低通滤波功能,进而所实现的低通滤波器的截止频率常由电阻或跨导与电容的时间常数决定。这一低通滤波器实现方式最大的问题是精度和线性度问题,比如无源电阻电容受工艺变化影响会导致低通截止频率漂移,跨导工作线性范围差会导致线性度和低通截止频率精度低。并且,连续时间滤波实现方式依赖大电阻或低跨导与大电容,无疑会需要更多的功耗和面积,不利于集成。

3、2)开关电容滤波,其采用开关电容替换电阻构造传输函数来实现低通滤波功能,进而所实现的低通滤波器的截止频率由电容比与开关频率来决定。但是,目前主流开关电容滤波器,主要针对高阶和高精度方面,而缺少低功耗方面的研究。高阶和高精度开关电容滤波器通过多个运放单元构造极为复杂的传输函数,并且还需要优化各级电路的失调误差来实现,这必然需要很大的功耗和面积,因而其在便携式或可穿戴设备中的应用范围或性能仍受到极大局限。

4、因此,在便携式或可穿戴设备的续航问题依旧突出的情况下,低通滤波器如何在低功耗下仍能维持高性能则成为当前的技术难题。

技术实现思路

1、本发明实施例的目的是提供一种低通滤波器及设备,用于至少部分地解决上述技术问题。

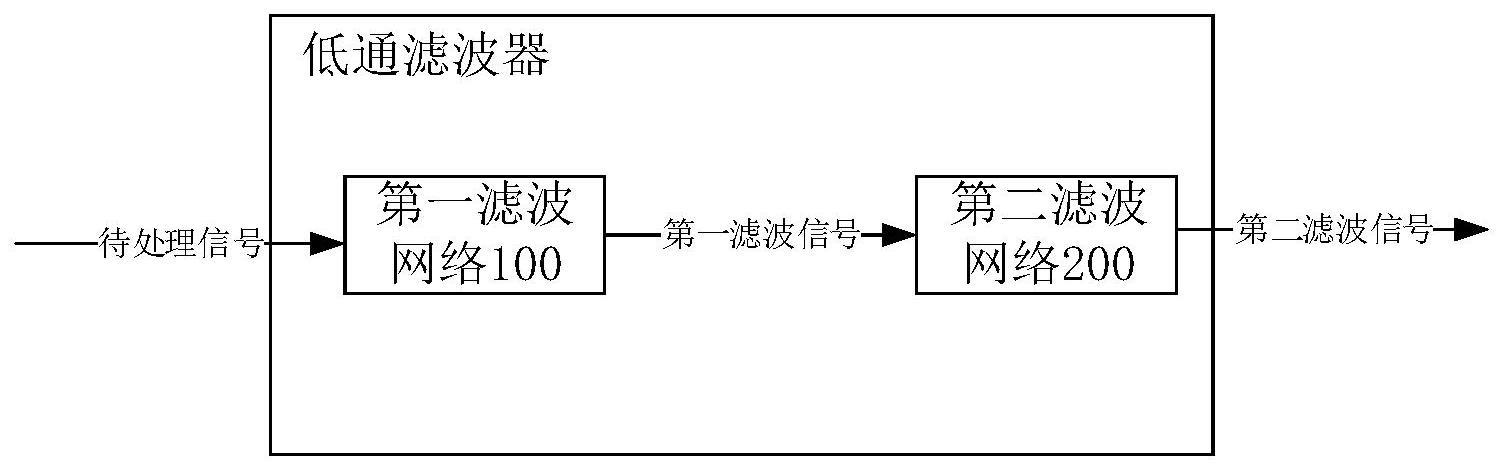

2、为了实现上述目的,本发明实施例提供一种低通滤波器,包括:第一滤波网络,其输入端接入待处理信号,用于提供针对该待处理信号的低通截止频率和可调增益以进行信号滤波,并输出第一滤波信号;以及第二滤波网络,其输入端接入所述第一滤波信号,用于滤除该第一滤波信号中的杂波,并输出第二滤波信号。

3、可选地,所述第一滤波网络包括:可调增益控制模块,包括分别连接所述第一滤波网络的正输入端和负输入端的正路径部分和负路径部分,用于在与相应输入端导通时对所述待处理信号进行第一次的增益调节和低通截止频率设计,以输出第一处理信号;运算放大器,其正负输入端和分别连接所述可调增益控制模块的正负路径部分的输出端,用于在与相应的正负路径部分导通时接收并放大所述第一处理信号,以输出第二处理信号作为所述第一滤波信号;以及时钟开关模块,包括适配于所述第一滤波网络中的各个模块之间的导通需求而设置的多个时钟控制开关,用于控制相应模块之间的导通。

4、可选地,所述正路径部分和所述负路径部分分别包括并联的若干组开关电容结构,且每组开关电容结构包括串联的可控开关和可调电容。

5、可选地,所述运算放大器包括各自连接所述可调增益控制模块的输出端的核心放大器和共模负反馈电路。

6、可选地,所述核心放大器包括:晶体管m1,其源极接地,栅极连接偏置第二偏置电压vb2;晶体管m2和晶体管m3,两者的源极相连后连接至所述晶体管m1的漏极,两者的栅极分别作为所述运算放大器的正负输入端;晶体管m4与晶体管m5,两者的漏极相连后连接至所述晶体管m2的漏极,两者的源极接入电源电压,且晶体管m4的栅极连接该晶体管m4的漏极,晶体管m5的栅极连接晶体管m3的漏极;晶体管m6与晶体管m7,两者的漏极相连后连接至所述晶体管m3的漏极,两者的源极接入电源电压,且晶体管m7的栅极连接该晶体管m7的漏极,晶体管m6的栅极连接晶体管m2的漏极;晶体管m8和晶体管m9,两者的栅极分别连接晶体管m4和晶体管m7的栅极,两者的源极连接电源电压,两者的漏极分别作为所述运算放大器的正负输出端;晶体管m10,其源极接地,栅极连接偏置第三偏置电压vb3;晶体管m11和晶体管m12,两者的源极相连后连接至所述晶体管m10的漏极,两者的栅极分别作为所述运算放大器的正负输入端;晶体管m13与晶体管m14,两者的漏极相连后连接至所述晶体管m11的漏极,两者的源极接地,且晶体管m13的栅极连接该晶体管m13的漏极,晶体管m14的栅极连接晶体管m12的漏极;晶体管m15与晶体管m16,两者的漏极相连后连接至所述晶体管m12的漏极,两者的源极接地,且晶体管m16的栅极连接该晶体管m16的漏极,晶体管m15的栅极连接晶体管m11的漏极;晶体管m17和晶体管m18,两者的源极接地,两者的漏极相连作为所述运算放大器的正输出端,晶体管m17的栅极连接晶体管m13的栅极,晶体管m18的栅极接入第四偏置电压vb4;晶体管m19和晶体管m20,两者的源极接地,两者的漏极相连作为所述运算放大器的负输出端,晶体管m19的栅极连接晶体管m16的栅极,晶体管m20的栅极接入第四偏置电压vb4。

7、可选地,所述共模负反馈电路包括:晶体管m21,其源极接入电源电压,栅极接入第三偏置电压vb3;晶体管m22和晶体管m23,两者的源极相连后连接所述晶体管m21的漏极,晶体管m23的漏极接入第四偏置电压vb4;晶体管m24和晶体管m25,两者的源极接地,两者的栅极相连后连接晶体管m24的漏极,且晶体管m24的漏极连接晶体管m22的漏极,晶体管m25的漏极接入第四偏置电压vb4;晶体管m26、晶体管m27、晶体管m28和晶体管m29,其中晶体管m26和晶体管m27两者的漏极和栅极各自相连后再互连,m28和晶体管m29两者的漏极和栅极各自相连后再互连,晶体管m26的源极作为所述运算放大器的正输出端,晶体管m28的源极作为所述运算放大器的负输出端,晶体管m27和晶体管m29的源极相连后连接晶体管m22的栅极;晶体管m30、晶体管m31、晶体管m32和晶体管m33,其中晶体管m30和晶体管m31两者的漏极和栅极各自相连后再互连,m32和晶体管m33两者的漏极和栅极各自相连后再互连,晶体管m31和晶体管m33的源极相连后接入第四偏置电压,晶体管m30和晶体管m32的源极相连后晶体管m23的栅极。

8、可选地,所述第一滤波网络还包括反馈模块,且该反馈模块包括设置在所述运算放大器的正输入端与负输出端之间的第一反馈部分和设置在所述运算放大器的负输入端与正输出端之间的第二反馈部分,且所述第一反馈部分和所述第二反馈部分分别连接所述可调增益控制模块的正负路径部分的输出端,并在与相应的正负路径部分导通时对所述第一处理信号进行第二次的增益调节和低通截止频率设计,以输出第三处理信号至所述运算放大器的输出端,使得所述运算放大器结合所述第二处理信号和所述第三处理信号来形成所述第一滤波信号。

9、可选地,所述反馈模块的所述第一反馈部分包括:一端连接所述可调增益控制模块的正路径部分的输出端,另一端连接所述运算放大器的负输出端的电容cf1;以及两端连接第一偏置电压vb1以及与所述电容cf1形成并联结构的电容ch1。所述反馈模块的所述第二反馈部分包括:一端连接所述可调增益控制模块的负路径部分的输出端,另一端连接所述运算放大器的正输出端的电容cf2;以及两端连接第一偏置电压vb1以及与所述电容cf2形成并联结构的电容ch2。

10、可选地,所述时钟开关模块包括以下开关对中的一者或多者:第一开关对,包括一端分别连接所述网络输入端的正输入端和负输入端、另一端分别连接所述可调增益控制模块的正路径部分和负路径部分的输入端的时钟控制开关s1和s2;第二开关对,包括一端各自接入第一偏置电压vb1、另一端分别连接所述可调增益控制模块的正路径部分和负路径部分的输入端的时钟控制开关s3和s4;第三开关对,包括一端各自接入第一偏置电压vb1、另一端分别连接所述可调增益控制模块的正路径部分和负路径部分的输出端的时钟控制开关s5和s6;第四开关对,包括一端分别连接在所述第三开关对的相应时钟控制开关与所述运算放大器的正负输入端之间、另一端分别连接所述电容cf1和所述电容cf2的时钟控制开关s7和s8;第五开关对,包括一端分别连接所述运算放大器的正负输入端、另一端分别连接所述电容cf1和所述电容cf2的时钟控制开关s9和s10;第六开关对,包括一端分别连接所述电容ch1和所述电容ch2、另一端分别连接所述电容cf1和所述电容cf2的时钟控制开关s11和s12;第七开关对,包括一端各自连接第一偏置电压vb1、另一端分别连接所述电容ch1和所述电容ch2的时钟控制开关s13和s14;第八开关对,包括一端分别连接所述电容ch1和所述电容ch2、另一端分别连接所述运算放大器的负输出端和正输出端的时钟控制开关s15和s16;以及第九开关对,包括一端各自连接第一偏置电压vb1,另一端分别连接所述电容ch1和所述电容ch2的时钟控制开关s17和s18。

11、可选地,所述时钟控制开关s1、s2、s5、s6、s9、s10、s13、s14、s17、s18在时钟ф1状态导通,所述时钟控制开关s3、s4、s7、s8、s11、s12、s15、s16在时钟ф2状态导通,且ф1不同于ф2。

12、可选地,所述第一滤波网络还包括失调存储模块,该失调存储模块包括:连接在所述可调增益控制模块的正路径部分的输出端与所述运算放大器的正输入端之间的第一失调校准部件;以及连接在所述可调增益控制模块的负路径部分的输出端与所述运算放大器的负输入端之间的第二失调校准部件。

13、可选地,所述第一失调校准部件是电容ce1,所述第二失调校准部件是电容ce2。

14、可选地,所述第二滤波网络是无源滤波电路。

15、本发明实施例还提供一种设备,包括上述任意的低通滤波器。

16、通过上述技术方案,本发明实施例的低通滤波器配置了两个滤波网络,第一滤波网络进行了低通截止频率和可调增益的设计,有助于适应场景来降低滤波器功耗,便于其在多场景下的应用,而第二滤波网络通过杂波滤除来进一步降低了滤波器功耗,且改善了信号的线性度。

17、本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

- 还没有人留言评论。精彩留言会获得点赞!