实现快速锁相的锁相环、分频器和通信设备的制作方法

本发明属于射频收发机领域,具体涉及一种实现快速锁相的锁相环、分频器和通信设备。

背景技术:

1、本部分旨在为权利要求书中陈述的本发明的实施方式提供背景或上下文。此处的描述不因为包括在本部分中就承认是现有技术。

2、随着半导体工艺尺寸不断缩小和系统复杂性提升,收发机芯片工作频率不断提高,为了确保芯片工作的稳定性,对于收发机时钟的频率和质量要求越来越高。锁相环(phase locked loop,pll)作为片上系统(system-on-a-chip,soc)的一种时钟源,广泛应用于各种收发机中。

3、锁相环的快速锁相一直是研发追求目标,但是受到稳定性、动态响应、精度和噪声等因素相互制约,锁相速度难以进一步提高。现有加速锁定方案包括改变电荷泵内部的电流,但此方案涉及的电路结构比较复杂,不仅容易给锁相环系统带来噪声,而且改变锁相环环路参数,从而难以广泛应用于各种锁相环系统。

4、因此,如何加快锁相速度是一个亟待解决的问题。

技术实现思路

1、针对上述现有技术中存在的锁相时间较长的问题,提出了一种实现快速锁相的锁相环、分频器和通信设备,能够加快锁相速度。

2、本发明提供了以下方案。

3、第一方面,提供一种实现快速锁相的锁相环,锁相环包括:鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、快速锁相控制单元和第一方面的分频器;其中,快速锁相控制单元,其被配置为当接收到锁相使能信号时,响应于参考时钟信号的上升沿输出高电平的复位信号;分频器,其包括级联的多级分频单元和复位/置位控制电路;其中,复位/置位控制电路接收快速锁相控制单元输出的复位信号,并响应于从低电平跳变为高电平的复位信号,将各级分频单元的状态编码所构成的状态编码组合从第一状态转移为第二状态,以使分频器输出的反馈信号从低电平跳变为高电平;鉴频鉴相器,其被配置为响应于高电平的复位信号,输出参考时钟信号和反馈信号的相位误差。

4、在一种实施方式中,其中的分频器还包括:时钟输出电路,其中,各级分频单元,均包含多个d触发器以及组合逻辑单元,各级分频单元中的预选d触发器的输出作为各级分频单元的状态输出;时钟输出电路,用于根据多级分频单元中的至少两个分频单元的状态输出生成分频器的反馈信号。

5、在一种实施方式中,各级分频单元包括多个d触发器,复位/置位控制电路包括设置在每个d触发器上的复位端rn或置位端sn。

6、在一种实施方式中,复位/置位控制电路被配置为:响应于复位信号为低电平,将各级分频单元的多个d触发器的复位端rn或置位端sn拉低,使各级分频单元的状态编码所构成的状态编码组合为预设的第一状态;以及,响应于复位信号跳变为高电平,将各级分频单元的多个d触发器的复位端rn或置位端sn拉高,使各级分频单元的状态编码所构成的状态编码转移为第二状态。

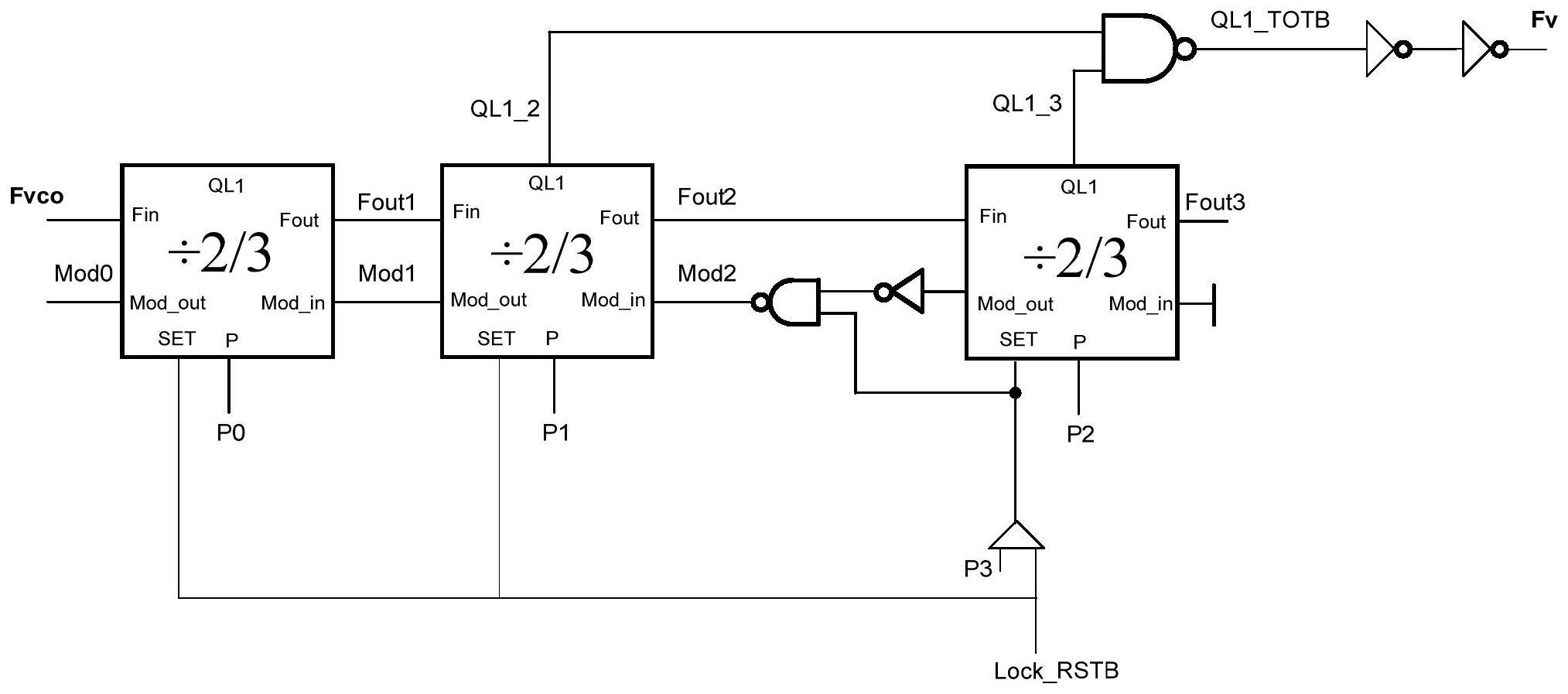

7、在一种实施方式中,分频器包括:第一级分频单元、第二级分频单元和第三级分频单元;其中,第二级分频单元的状态输出ql1_2和第三级分频单元的状态输出ql1_3提供至与非门,与非门的输出作为分频器输出的反馈信号。

8、在一种实施方式中,第一级分频单元包含4个d触发器;复位/置位控制电路包括:设置在第一级分频单元的第一级第一d触发器、第一级第三d触发器、第一级第四d触发器的复位端rn,设置在第一级第二d触发器上的置位端sn;以及,将复位端rn和置位端sn连接至快速锁相控制单元的输出端的电路。

9、在一种实施方式中,第二级分频单元包括4个d触发器;复位/置位控制电路包括:设置在第二级分频单元的第二级第一d触发器、第二级第二d触发器上的置位端sn;设置在第二级第三d触发器、第二级第四d触发器上的复位端rn;以及,将复位端rn和置位端sn连接至快速锁相控制单元的输出端的电路。

10、在一种实施方式中,第三级分频单元包括4个d触发器;复位/置位控制电路包括:设置在第三级分频单元的第三级第一d触发器、第三级第二d触发器上的置位端sn;设置在第三级第三d触发器、第三级第四d触发器上的复位端rn;与门电路,其输入端接收复位信号和除数控制信号,其输出端连接第三级分频单元的复位端rn和置位端sn。

11、在一种实施方式中,各级分频单元被配置为:根据除数控制信号以及模数输入信号,对所接收的时钟信号完成频率除以n或者除以n+1的功能,n为大于1的自然数。

12、第二方面,提供一种分频器,包括:级联的多级分频单元;复位/置位控制电路,复位/置位控制电路响应于从低电平跳变为高电平的复位信号,通过复位/置位操作将各级分频单元的状态编码所构成的状态编码组合从第一状态转移为第二状态,以使分频器输出的反馈信号从低电平跳变为高电平,其中,复位信号响应于锁相使能信号以及参考时钟的上升沿,从低电平跳变为高电平。

13、在一种实施方式中,其中的分频器还包括:时钟输出电路,其中,各级分频单元,均包含多个d触发器以及组合逻辑单元,各级分频单元中的预选d触发器的输出作为各级分频单元的状态输出;时钟输出电路,用于根据多级分频单元中的至少两个分频单元的状态输出生成分频器的反馈信号。

14、在一种实施方式中,各级分频单元包括多个d触发器,复位/置位控制电路包括设置在每个d触发器上的复位端rn或置位端sn。

15、在一种实施方式中,复位/置位控制电路被配置为:响应于复位信号为低电平,将各级分频单元的多个d触发器的复位端rn或置位端sn拉低,使各级分频单元的状态编码所构成的状态编码组合为预设的第一状态;以及,响应于复位信号跳变为高电平,将各级分频单元的多个d触发器的复位端rn或置位端sn拉高,使各级分频单元的状态编码所构成的状态编码转移为第二状态。

16、在一种实施方式中,分频器包括:第一级分频单元、第二级分频单元和第三级分频单元;其中,第二级分频单元的状态输出ql1_2和第三级分频单元的状态输出ql1_3提供至与非门,与非门的输出作为分频器输出的反馈信号。

17、在一种实施方式中,第一级分频单元包含4个d触发器;复位/置位控制电路包括:设置在第一级分频单元的第一级第一d触发器、第一级第三d触发器、第一级第四d触发器的复位端rn,设置在第一级第二d触发器上的置位端sn;以及,将复位端rn和置位端sn连接至快速锁相控制单元的输出端的电路。

18、在一种实施方式中,第二级分频单元包括4个d触发器;复位/置位控制电路包括:设置在第二级分频单元的第二级第一d触发器、第二级第二d触发器上的置位端sn;设置在第二级第三d触发器、第二级第四d触发器上的复位端rn;以及,将复位端rn和置位端sn连接至快速锁相控制单元的输出端的电路。

19、在一种实施方式中,第三级分频单元包括4个d触发器;复位/置位控制电路包括:设置在第三级分频单元的第三级第一d触发器、第三级第二d触发器上的置位端sn;设置在第三级第三d触发器、第三级第四d触发器上的复位端rn;与门电路,其输入端接收复位信号和除数控制信号,其输出端连接第三级分频单元的复位端rn和置位端sn。

20、在一种实施方式中,各级分频单元被配置为:根据除数控制信号以及模数输入信号,对所接收的时钟信号完成频率除以n或者除以n+1的功能,n为大于1的自然数。

21、第三方面,提供一种实现快速锁相的通信设备,其特征在于,包括如第二方面的锁相环。

22、上述实施例的优点之一,通过在锁相环设置快速锁相控制单元,从而能响应于锁相使能信号以及参考时钟的上升沿,输出从低电平跳变为高电平的复位信号,以及在该分频器上设置简单的复位/置位控制电路,使分频器响应于从低电平跳变为高电平的复位信号,对应输出从低电平跳变为高电平反馈信号,能够使分频器支持快速锁相功能,从而实现快速锁相。

23、本发明的其他优点将配合以下的说明和附图进行更详细的解说。

24、应当理解,上述说明仅是本发明技术方案的概述,以便能够更清楚地了解本发明的技术手段,从而可依照说明书的内容予以实施。为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举例说明本发明的具体实施方式。

- 还没有人留言评论。精彩留言会获得点赞!