双线性化鉴频鉴相电路及小数分频的电荷泵锁相环的制作方法

本发明涉及锁相环,特别是涉及一种双线性化鉴频鉴相电路及小数分频的电荷泵锁相环。

背景技术:

1、锁相环被广泛应用于时钟同步、频率综合、无线系统、数字电路、高性能微处理器等领域,用于提供时钟频率或本振频率。在各种锁相环结构中,电荷泵锁相环应用最为广泛,电荷泵锁相环的捕获范围大,工作频率范围仅由压控振荡器的频率范围决定,它在锁定时有静态相差为零的优点,即输出信号可以无相差的跟踪输入信号。锁相环按分频比覆盖范围分类,有整数分频锁相环和小数分频锁相环两类,小数分频锁相环具有高频率分辨率和高鉴相频率等特点,小数分频的电荷泵锁相环是目前锁相环产品的重点发展方向。

2、小数分频的电荷泵锁相环包括鉴频鉴相器、电荷泵、环路滤波器、压控振荡器、反馈分频器及sigma-delta调制器,鉴频鉴相器将参考输入信号和反馈分频输出信号之间的频率和相位进行比较,电荷泵将鉴频鉴相器的输出信号转换为充电电流或放电电流,环路滤波器将电荷泵的输出电流转换为电压信号控制压控振荡器,压控振荡器产生所需频率的压控振荡信号。在此过程中,由于sigma-delta调制器的作用,在不同周期的上升沿时刻,反馈分频输出信号相位相比参考输入信号相位会出现超前或滞后现象,延时范围为:-3tvco~4tvco(若sigma-delta调制器的插值范围为-3~+4)。sigma-delta调制器的高频处噪声会折叠到环路带宽内,恶化锁相环闭环带内相位噪声,特别在宽环路带宽下,恶化尤为明显。

3、为解决这一问题,可在反馈分频输出信号与参考输入信号之间增加固定相位偏移,避开充放电电流的非线性区域。而传统技术方案是在电荷泵输出端增加恒定偏差电流来解决非线性问题,但该方案要实现低相位噪声需要较大的电荷泵电流,较大的电荷泵电流又会引入参考杂散。

4、因此,目前亟需一种既能实现电荷泵充放电电流的线性化、又能降低闭环相位噪声的小数分频的电荷泵锁相环技术方案。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种小数分频的电荷泵锁相环技术方案,设计双线性化鉴频鉴相电路,基于双线性化鉴频鉴相电路,既能实现电荷泵充放电电流的线性化,又能实现电荷泵双倍充放电电流效果,以降低锁相环闭环相位噪声。

2、为实现上述目的及其它相关目的,本发明提供的技术方案如下。

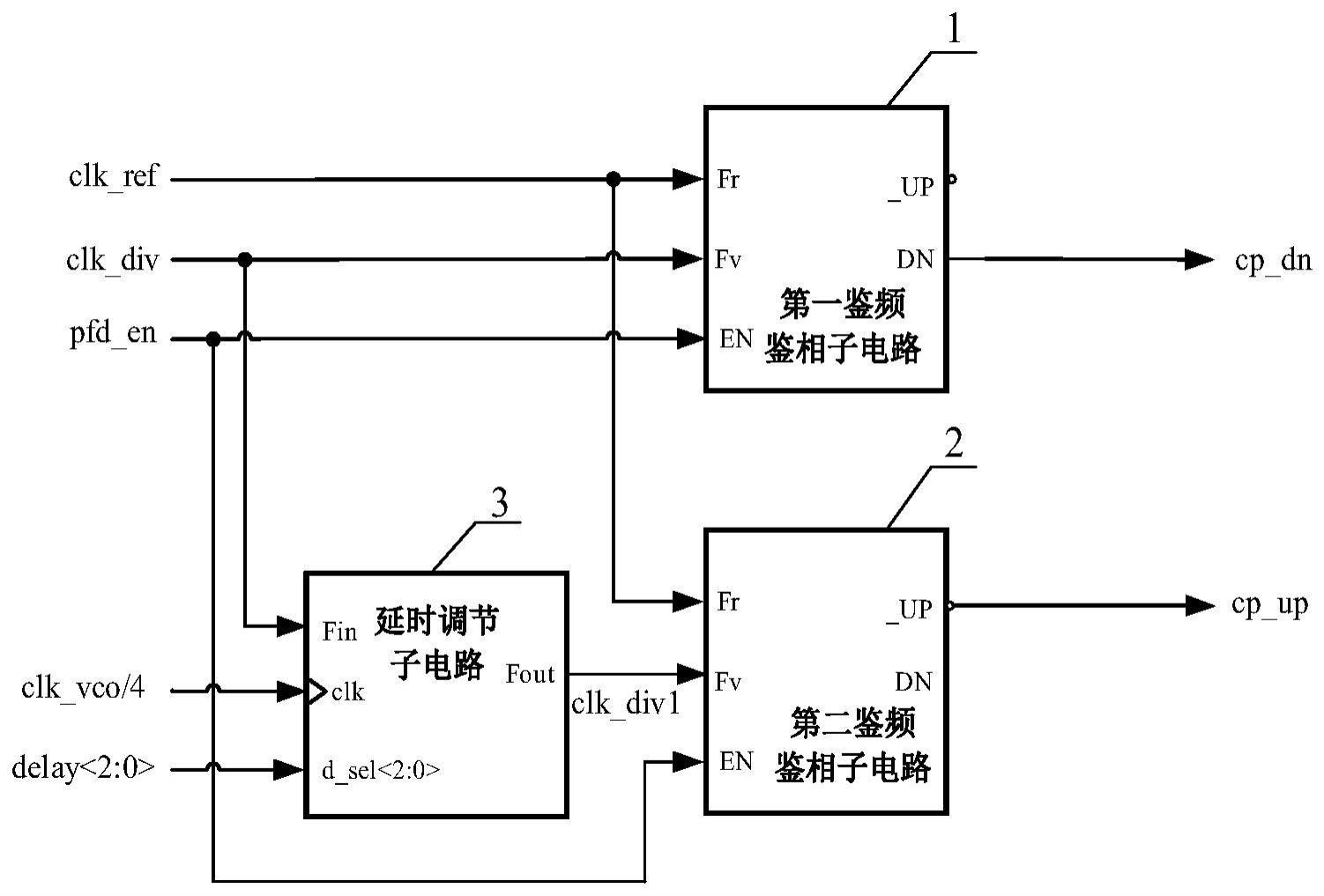

3、一种双线性化鉴频鉴相电路,应用于小数分频的电荷泵锁相环,包括:

4、第一鉴频鉴相子电路,接收参考输入信号、反馈分频输出信号、鉴频鉴相使能信号,在所述鉴频鉴相使能信号的控制下,对所述参考输入信号及所述反馈分频输出信号进行鉴频鉴相处理,得到第一控制信号,所述第一控制信号作为电荷泵的放电控制信号;

5、第二鉴频鉴相子电路,接收所述参考输入信号、反馈分频输出延时信号、所述鉴频鉴相使能信号,在所述鉴频鉴相使能信号的控制下,对所述参考输入信号及所述反馈分频输出延时信号进行鉴频鉴相处理,得到第二控制信号,所述第二控制信号作为所述电荷泵的充电控制信号;

6、延时调节子电路,接收所述反馈分频输出信号、时钟信号及延时调节控制信号,在所述延时调节控制信号的控制下,对所述反馈分频输出信号进行延时处理,得到所述反馈分频输出延时信号;

7、其中,基于所述延时调节子电路的延时处理,所述反馈分频输出信号与所述反馈分频输出延时信号之间具有预设相位差,所述第一控制信号的上升沿与所述第二控制信号的上升沿之间具有所述预设相位差,所述电荷泵的放电电流的下降沿与所述电荷泵的充电电流的下降沿之间也具有所述预设相位差,使得所述电荷泵的放电电流与所述电荷泵的充电电流同步变化。

8、可选地,所述第一鉴频鉴相子电路的结构与所述第二鉴频鉴相子电路的结构相同。

9、可选地,所述延时调节子电路包括第一延时控制单元、第二延时控制单元、第三延时控制单元、第一或门、第二或门、第三或门、第四或门、第一d触发器、第二d触发器及第三d触发器,所述第一延时控制单元的输入端作为所述延时调节子电路的输入端,所述第一延时控制单元的输入端接所述反馈分频输出信号,所述第一延时控制单元的输出端接所述第二延时控制单元的输入端,所述第一延时控制单元的输出端还接所述第二或门的第一输入端,所述第一延时控制单元的延时控制端接第一个所述延时调节控制信号,所述第二延时控制单元的输出端接所述第三延时控制单元的输入端,所述第二延时控制单元的输出端还接所述第一或门的第一输入端,所述第二延时控制单元的延时控制端接第二个所述延时调节控制信号,所述第三延时控制单元的输出端接所述第一或门的第二输入端,所述第三延时控制单元的延时控制端接第三个所述延时调节控制信号,所述第一或门的输出端接所述第二或门的第二输入端,所述第二或门的输出端接所述第三或门的第二输入端,所述第三或门的输出端接所述第一d触发器的数据输入端,所述第一d触发器的数据输出正端接所述第三或门的第一输入端,所述第一d触发器的时钟输入端作为所述延时调节子电路的时钟端,所述第一d触发器的时钟输入端接所述时钟信号,所述第一d触发器的数据输出正端还接所述第二d触发器的数据输入端,所述第二d触发器的时钟输入端接所述时钟信号,所述第二d触发器的数据输出正端接所述第三d触发器的数据输入端,所述第二d触发器的数据输出正端还接所述第四或门的第一输入端,所述第三d触发器的时钟输入端接所述时钟信号,所述第三d触发器的数据输出正端接所述第四或门的第二输入端,所述第四或门的输出端作为所述延时调节子电路的输出端,所述第四或门的输出端输出所述反馈分频输出延时信号。

10、一种小数分频的电荷泵锁相环,包括上述任一项所述的双线性化鉴频鉴相电路、所述电荷泵、环路滤波器、压控振荡器、反馈分频器及sigma-delta调制器,所述双线性化鉴频鉴相电路接收所述参考输入信号、所述反馈分频输出信号、所述鉴频鉴相使能信号、所述时钟信号及所述延时调节控制信号,经所述双线性化鉴频鉴相电路处理后,得到所述第一控制信号及所述第二控制信号,所述电荷泵的控制端分别与所述第一控制信号及所述第二控制信号连接,所述第一控制信号作为所述电荷泵的放电控制信号,所述第二控制信号作为所述电荷泵的充电控制信号,所述电荷泵的输出端接所述环路滤波器的输入端,所述环路滤波器的输出端接所述压控振荡器的输入端,所述压控振荡器的输出端输出压控振荡输出信号,所述压控振荡器的输出端还接所述反馈分频器的输入端,所述反馈分频器的输出端输出所述反馈分频输出信号,所述反馈分频器的输出端还接所述sigma-delta调制器的输入端,所述sigma-delta调制器的输出端接所述反馈分频器的控制端。

11、可选地,所述时钟信号的周期与所述压控振荡输出信号的周期之比为4/1。

12、可选地,所述充电电流与所述放电电流相等。

13、如上所述,本发明的双线性化鉴频鉴相电路及小数分频的电荷泵锁相环,至少具有以下

14、有益效果:

15、结合第一鉴频鉴相子电路、第二鉴频鉴相子电路及延时调节子电路设计双线性化鉴频鉴相电路,基于延时子电路的延时处理,使得反馈分频输出信号与反馈分频输出延时信号之间具有预设相位差,第一控制信号的上升沿与第二控制信号的上升沿之间具有预设相位差,电荷泵的放电电流的下降沿与电荷泵的充电电流的下降沿之间也具有预设相位差,使得电荷泵的放电电流与电荷泵的充电电流同步变化,这实现了电荷泵充放电电流的线性化;同时,设置电荷泵的充电电流与电荷泵的放电电流相等,一个周期内有双倍充放电电流效果,能有效降低电荷泵的输出噪声及锁相环的闭环噪声。

- 还没有人留言评论。精彩留言会获得点赞!