一种具有失配校准功能的动态锁存比较器的制作方法

本发明属于集成电路,更具体地,涉及一种具有失配校准功能的动态锁存比较器。

背景技术:

1、动态锁存比较器(strong arm latch)广泛地应用于灵敏放大、小信号采样和信号的采样比较等场景,由于动态锁存比较器具有采样和放大的双重作用,并且灵敏度极高,所以在集成电路内部被广泛采用,特别是高速接口部分,例如pcie、usb、高速serdes、hdmi等接口的接收器部分经常使用动态锁存比较器电路来接收微弱小信号。然而,动态锁存比较器的性能,特别是动态锁存比较器天生的失配特性会严重影响整体电路的性能,例如,在28gbps、56gbps的高速serdes接收电路中,接收器希望能分辨1mv~3mv的输入幅度差别,而动态锁存比较器固有的器件失配很可能带来5mv~10mv的误差,并且一个接收器电路一般会使用多个动态锁存比较器,此外,因为集成电路工艺波动的随机性,同一个接收器电路中多个动态锁存比较器的失配也是随机的,因此,必须要考虑每个动态锁存比较器的失配并进行校准,不然会严重影响高速接收器电路的性能。

2、现有的对动态锁存比较器的失配进行校准的电路均不可避免地对动态锁存比较器的速度或者功耗产生显著的负面影响。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本发明提供了一种具有失配校准功能的动态锁存比较器,能够在对比较器进行失配校准的同时,不对比较器的速度和功耗产生负面影响。

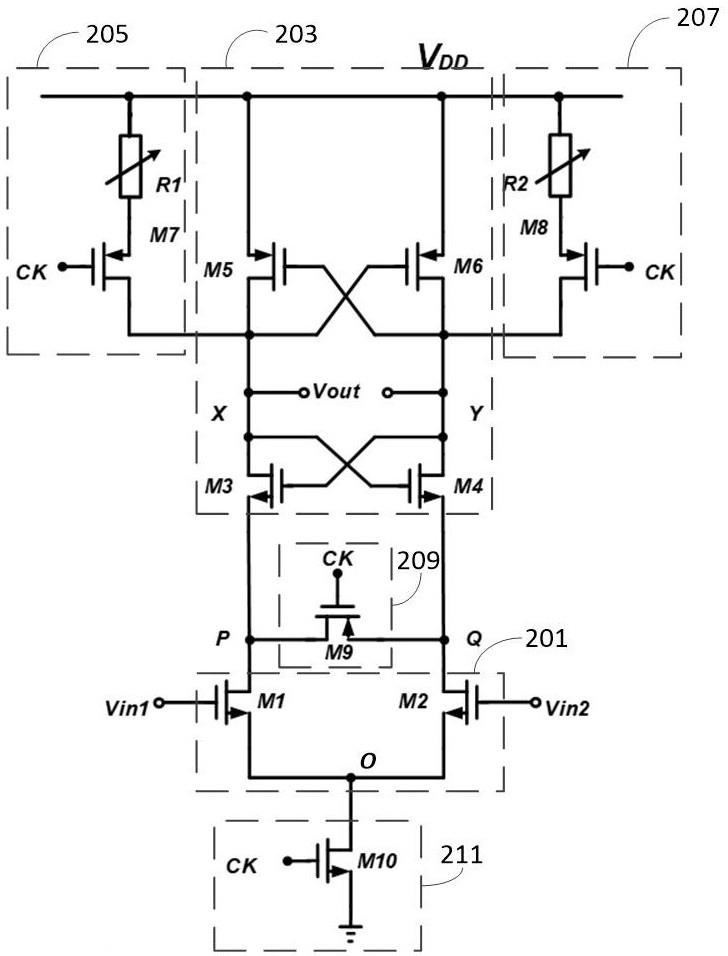

2、为实现上述目的,本发明提供了一种比较器,包括输入模块、锁存模块、第一开关模块、第二开关模块、第三开关模块和第四开关模块;输入模块用于根据第一输入电压vin1和第二输入电压vin2,产生第一比较结果;锁存模块用于将第一比较结果放大,产生第二比较结果,并将第二比较结果锁存和输出;第一开关模块、第二开关模块和第三开关模块用于对锁存模块进行状态重置;第四开关模块用于使能输入模块;第一开关模块包括第一阻值调节模块,第二开关模块包括第二阻值调节模块;第一阻值调节模块和第二阻值调节模块用于在锁存模块建立锁存的过程中,通过调节产生第二比较结果的端口电平,对比较器进行失配校准。

3、在一些实施方式中,第一开关模块和第二开关模块用于对产生第二比较结果的端口进行状态重置,第三开关模块用于对产生第一比较结果的端口进行状态重置;第一阻值调节模块具有可调节的阻抗值或者等效阻抗值,第二阻值调节模块具有可调节的阻抗值或者等效阻抗值。

4、在一些实施方式中,输入模块的第一端用于获取第一输入电压vin1,输入模块的第二端用于获取第二输入电压vin2;锁存模块的第一端连接第一开关模块的输出端,锁存模块的第二端连接第二开关模块的输出端,锁存模块的第三端连接输入模块的第三端和第三开关模块的第一端,锁存模块的第四端连接输入模块的第四端和第三开关模块的第二端;输入模块的第五端连接第四开关模块的输出端。

5、在一些实施方式中,将锁存模块和第一开关模块的公共端标记为节点x,将锁存模块和第二开关模块的公共端标记为节点y,将锁存模块的第三端和输入模块的第三端的公共端分别标记为节点p,将锁存模块的第四端和输入模块的第四端的公共端分别标记为节点q,将输入模块和第四开关模块的公共端标记为节点o;输入模块用于在节点p和节点q产生第一比较结果;锁存模块用于在节点x和节点y产生第二比较结果;第一开关模块用于控制节点x的电平,第二开关模块用于控制节点y的电平,第三开关模块用于控制节点p和节点q的电平,第四开关模块用于控制节点o的电平。

6、在一些实施方式中,第一开关模块、第二开关模块、第三开关模块和第四开关模块均受到控制电压ck的控制;在控制电压ck为第一电平时,第一开关模块、第二开关模块和第三开关模块处于第一状态,第四开关模块处于第二状态,对锁存模块进行状态重置,输入模块不工作;

7、在控制电压ck由第一电平变化至第二电平时,第一开关模块、第二开关模块和第三开关模块从第一状态变化到第二状态,第四开关模块从第二状态变化到第一状态,第一输入电压vin1和第二输入电压vin2的压差经过输入模块后,使得节点p和节点q的电平出现差异,产生第一比较结果;锁存模块建立锁存,进入锁存态,节点p和节点q的电平差异经锁存模块放大,在节点x和节点y之间产生第二比较结果;

8、在控制电压ck为第二电平时,第一输入电压vin1和第二输入电压vin2的压差通过第二比较结果被锁存在锁存模块中。

9、在一些实施方式中,通过调节第一阻值调节模块的阻抗或者等效阻抗,对第一开关模块从第一状态到第二状态的电流进行调节,通过调节第二阻值调节模块的阻抗或者等效阻抗,对第二开关模块从第一状态到第二状态的电流进行调节,进而调节节点x和节点y在锁存模块建立锁存的过程中的电平,对比较器进行失配校准。

10、在一些实施方式中,第一电平为低电平,第二电平为高电平,第一状态为导通状态,第二状态为关断状态;或者,第一电平为高电平,第二电平为低电平,第一状态为导通状态,第二状态为关断状态。

11、在一些实施方式中,输入模块包括第一晶体管和第二晶体管,第一晶体管的控制端连接输入模块的第一输入端,第二晶体管的控制端连接输入模块的第二输入端,第一晶体管的第一端连接输入模块的第三端,第二晶体管的第一端连接输入模块的第四端,第一晶体管的第二端连接第二晶体管的第二端和输入模块的第五端。

12、在一些实施方式中,锁存模块包括第三晶体管、第四晶体管、第五晶体管和第六晶体管;第三晶体管的第一端连接第五晶体管的第一端、第六晶体管的控制端、第四晶体管的控制端和锁存模块的第一端;第四晶体管的第一端连接第六晶体管的第一端、第五晶体管的控制端、第三晶体管的控制端和锁存模块的第二端;第三晶体管的第二端连接锁存模块的第三端,第四晶体管的第二端连接锁存模块的第四端;第五晶体管的第二端和第六晶体管的第二端用于连接第一预设电平。

13、在一些实施方式中,第一开关模块还包括第七晶体管;第七晶体管的第一端连接第一开关模块的输出端,第七晶体管的第二端连接第一阻值调节模块的第一端,第七晶体管的控制端用于获取控制电压ck,第一阻值调节模块的第二端用于连接第一预设电平;或者,第七晶体管的第一端连接第一阻值调节模块的第一端,第七晶体管的第二端用于连接第一预设电平,第七晶体管的控制端用于获取控制电压ck,第一阻值调节模块的第二端连接第一开关模块的输出端。

14、在一些实施方式中,第二开关模块还包括第八晶体管;第八晶体管的第一端连接第二开关模块的输出端,第八晶体管的第二端连接第二阻值调节模块的第一端,第八晶体管的控制端用于获取控制电压ck,第二阻值调节模块的第二端用于连接第一预设电平;或者,第八晶体管的第一端连接第二阻值调节模块的第一端,第八晶体管的第二端用于连接第一预设电平,第八晶体管的控制端用于获取控制电压ck,第二阻值调节模块的第二端连接第二开关模块的输出端。

15、在一些实施方式中,第三开关模块包括第九晶体管;第九晶体管的第一端连接第三开关模块的第一端,第九晶体管的第二端连接第三开关模块的第二端,第九晶体管的控制端用于获取控制电压ck。

16、在一些实施方式中,第四开关模块包括第十晶体管;第十晶体管的第一端连接第四开关模块的输出端,第十晶体管的第二端用于连接第二预设电平,第十晶体管的控制端用于获取控制电压ck。

17、在一些实施方式中,第一阻值调节模块包括可调电阻和压控mos管至少其中之一。

18、在一些实施方式中,第二阻值调节模块包括可调电阻和压控mos管至少其中之一。

19、总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:在比较器的两条控制路径上的开关模块中引入阻值调节模块,使得两条控制路径的关断过程出现差别,且能够通过引入的阻值调节模块调节这个差别,进而调节比较器中锁存模块的建立过程,实现失配补偿的目的。由于引入的阻值调节模块不会对比较器的关键路径节点产生影响,因此不会导致比较器的速度降低或者功耗变大。

- 还没有人留言评论。精彩留言会获得点赞!