一种多模式功率放大器的制作方法

本发明涉及射频集成电路设计领域,具体涉及多模式功率放大器。

背景技术:

1、多模式功率放大器在军事领域中,可根据任务、环境、目标的变化,快速敏捷地完成发射通道的重构和参数优化配置,对军事化应用的电子装备发展有较大意义;民用领域中无线通信终端对于各通信标准的兼容性成为了通信技术发展的目标与趋势,多模式功率放大器以契合整体射频系统的应用需求成为当前民用通信系统研究的重要部分。

2、当前多模式功率放大器主要采用封装技术、宽带匹配技术实现。例如skyworks公司的sky77432产品、rfmd公司的rf7178产品、文献《可重构射频前端功率放大器和滤波器集成协同设计与研究》均采用基于多颗芯片/器件的封装技术实现多模多频模组芯片功放,但该实现方案导致模组芯片体积大,对无线通信终端的小型化存在弊端;文献《面向td-scdma/td-lte/td-lte-a的多模可重构射频功率放大器研究》利用宽带匹配技术实现了一款可支持1880-1920mhz、2010-2025mhz、2300-2400mhz和2570-2620mhz的功率放大器。从上述内容中可看出当前多模式功率放大器主要集中在多频段的研究,可重构性相对较单一,难以支持当前通信终端产品实现对工作频段、功耗、增益等参数的调整以满足各类通信场景的需求。

技术实现思路

1、针对当前多模功率放大器可重构性较单一,本发明从无线通信终端系统架构角度考虑,提出了基于单款芯片即可实现工作类型、增益、功耗、工作频段等多维度可重构的功率放大器,可满足恒定包络/非恒定包络的调制通信方式,与当前多模式功率放大器相比具有可重构性强、体积小易于片内集成等特点。

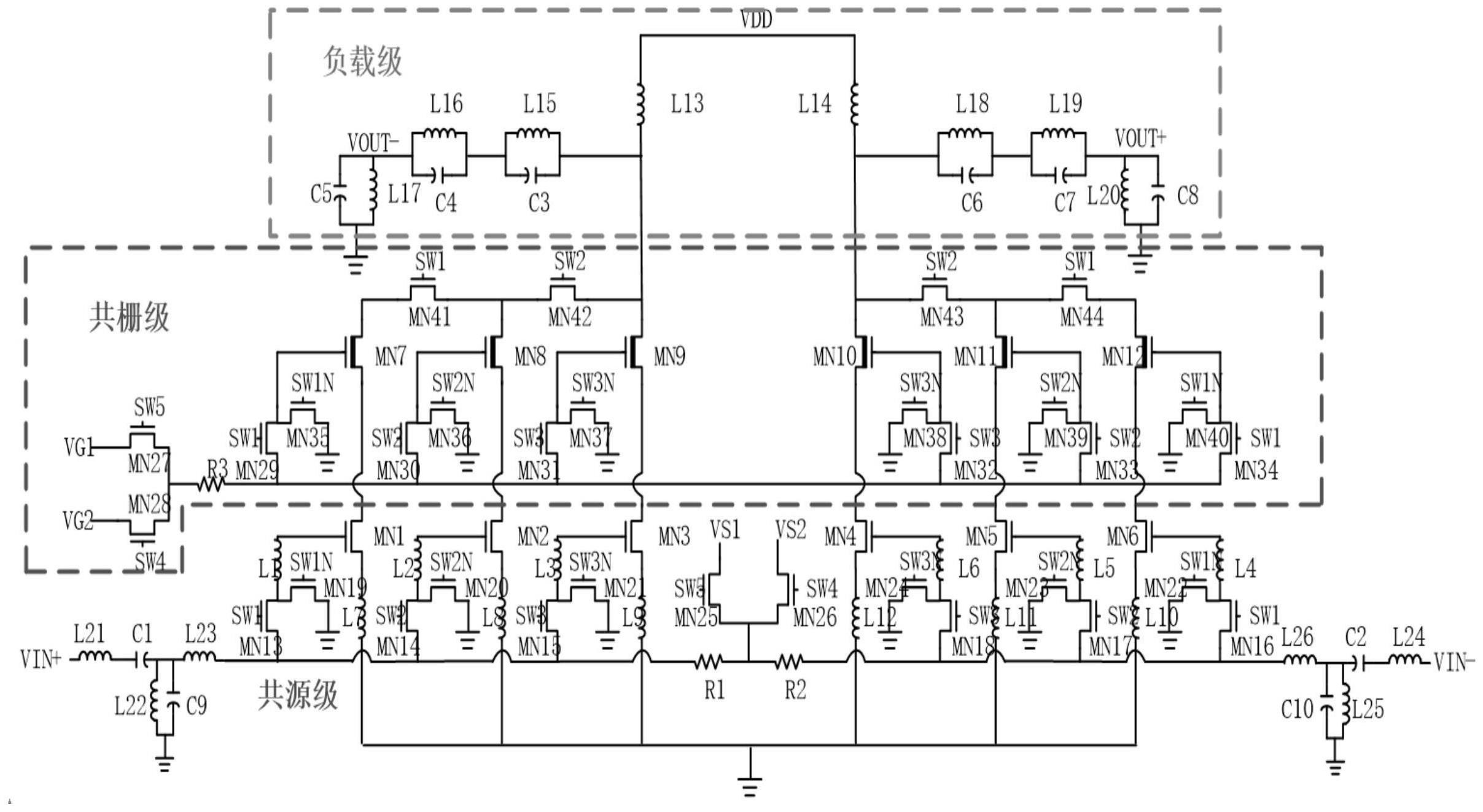

2、本发明为解决上述技术问题所采用的技术方案是:本发明依次包括括共源级、共栅极、负载级。所述多模式功率放大器整体采用共源共栅架构,其中采用薄栅的共源晶体管来获得较高的跨导效率,以及厚栅的共栅晶体管来提高输出电压摆幅并改善电路的可靠性;同时利用改变电路的偏置状态实现ab类和f类的切换,可在共享相同的电路结构前提下满足非恒包络与恒包络通信方式,达到输出线性度与效率兼顾的特性;共源晶体管栅极加入带通滤波器与源级退化电感、晶体管自身寄生电容实现宽频带内输入阻抗匹配,达到支持多频段工作的模式;另外多模式功率放大器整体由三条尺寸比例为1:1:2的并联支路组成,利用控制信号可实现各支路的导通与关闭,从而在保持较好输入驻波比的情况下实现增益的改变;负载级采用三阶、五阶奇次并联谐波网络提高输出端电压摆幅实现效率提升。本发明具有工作类型可重构、增益可变化的特点,实现工作效率与线性度的兼顾,可满足以幅移键控(ask)、正交幅度调制(qsm)、星座调制(mqsk)的非恒包络调制方式以及以四相相移键控(qpsk)、二相相移键控(bpsk)、最小频移键控(msk)的恒定包络调制方式的通信系统需求,能够用于导航收发机、卫星通信收发机、蓝牙收发机等无线通信射频集成电路中;

3、所述共源级包括薄栅nmos管mn1、mn2、mn3、mn4、mn5、mn6、mn13、mn14、mn15、mn16、mn17、mn18、mn19、mn20、mn21、mn22、mn23、mn24、mn25、mn26,电阻r1、r2,电容c1、c2、c9、c10,电感l1、l2、l3、l4、l5、l6、l7、l8、l9、l10、l11、l12、l21、l22、l23、l24、l25、l26;

4、所述共栅极包括厚栅nmos管mn7、mn8、mn9、mn10、mn11、mn12,薄栅nmos管mn27、mn28、mn29、mn30、mn31、mn32、mn33、

5、mn34、mn35、mn36、mn37、mn38、mn39、mn40、mn41、mn42、mn43、mn44,电阻r3;

6、所述负载级包括电感l13、l14、l15、l16、l17、l18、l19、l20,电容c3、c4、c5、c6、c7、c8,

7、其中vin+与电感l21左端相连接,电感l21与电容c1上极板相连接,电容c1下极板与电感l22上端、电容c9上极板、电感l23左端相连接,电感l22下端与电容c9下极板均与地相连接,电感l23右端与薄栅nmos管mn13、mn14、mn15源级以及电阻r1左端相连接,vin-与电感l24右端相连接,电感l24与电容c2上极板相连接,电容c2下极板与电感l25上端、电容c10上极板、电感l26左端相连接,电感l25下端与电容c10下极板均与地相连接,电感l26左端与薄栅nmos管mn16、mn17、mn18源级以及电阻r2右端相连接,薄栅cmos管mn13栅极与控制信号sw1相连接,漏级与薄栅cmos管mn19漏级和电感l1下端相连接,电感l1上端与晶体管mn1栅极相连接,薄栅cmos管mn19栅极与控制信号sw1n相连接,源级与地相连接,薄栅cmos管mn1漏级与厚栅cmos管mn7源级相连接,漏级与电感l7上端相连接,电感l7下端与地相连接,薄栅cmos管mn14栅极与控制信号sw2相连接,漏级与薄栅cmos管mn20漏级和电感l2下端相连接,电感l2上端与晶体管mn2栅极相连接,薄栅cmos管mn20栅极与控制信号sw2n相连接,源级与地相连接,薄栅cmos管mn2漏级与厚栅cmos管mn8源级相连接,漏级与电感l8上端相连接,电感l8下端与地相连接,薄栅cmos管mn15栅极与控制信号sw3相连接,漏级与薄栅cmos管mn21漏级和电感l3下端相连接,电感l3上端与晶体管mn3栅极相连接,薄栅cmos管mn21栅极与控制信号sw3n相连接,源级与地相连接,薄栅cmos管mn3漏级与厚栅cmos管mn9源级相连接,漏级与电感l9上端相连接,电感l9下端与地相连接,薄栅cmos管mn16栅极与控制信号sw1相连接,漏级与薄栅cmos管mn22漏级和电感l4下端相连接,电感l4上端与晶体管mn6栅极相连接,薄栅cmos管mn22栅极与控制信号sw1n相连接,源级与地相连接,薄栅cmos管mn6漏级与厚栅cmos管mn12源级相连接,漏级与电感l10上端相连接,电感l10下端与地相连接,薄栅cmos管mn17栅极与控制信号sw1相连接,漏级与薄栅cmos管mn23漏级和电感l5下端相连接,电感l5上端与晶体管mn5栅极相连接,薄栅cmos管mn23栅极与控制信号sw2n相连接,源级与地相连接,薄栅cmos管mn5漏级与厚栅cmos管mn11源级相连接,漏级与电感l11上端相连接,电感l11下端与地相连接,薄栅cmos管mn18栅极与控制信号sw3相连接,漏级与薄栅cmos管mn24漏级和电感l6下端相连接,电感l6上端与晶体管mn4栅极相连接,薄栅cmos管mn24栅极与控制信号sw3n相连接,源级与地相连接,薄栅cmos管mn4漏级与厚栅cmos管mn10源级相连接,漏级与电感l12上端相连接,电感l12下端与地相连接,薄栅cmos管mn25栅极与控制信号sw5相连接,漏级与偏置电压vs1相连接,源级与薄栅cmos管mn26源级以及电阻r1右端、电阻r2左端相连接,薄栅cmos管mn26栅极与控制信号sw4相连接,漏级与偏置电压vs2相连接,薄栅cmos管nm27栅极与控制信号sw5相连接,漏级与偏置电压vg1相连接,源级与电阻r3左端以及薄栅cmos管mn28源级相连接,薄栅cmos管nm28栅极与控制信号sw4相连接,漏级与偏置电压vg2相连接,电阻r3右端与薄栅cmos管mn35、mn36、mn37、mn38、mn39、mn40的源级相连接,薄栅cmos管mn29栅极与控制信号sw1相连接,漏级与薄栅cmos管mn35漏级以及厚栅cmos管mn7栅极相连接,薄栅cmos管mn35栅极与控制信号sw1n相连接,源级与地相连接,厚栅cmos管mn7漏级与薄栅晶体cmos管mn41漏级相连接,薄栅cmos管mn30栅极与控制信号sw2相连接,漏级与薄栅cmos管mn36漏级以及厚栅cmos管mn8栅极相连接,薄栅cmos管mn36栅极与控制信号sw2n相连接,源级与地相连接,厚栅cmos管mn8漏级与薄栅cmos管mn42源级以及薄栅cmos管mn42漏级相连接,薄栅cmos管mn31栅极与控制信号sw3相连接,漏级与薄栅cmos管mn37漏级以及厚栅cmos管mn9栅极相连接,薄栅cmos管mn37栅极与控制信号sw3n相连接,源级与地相连接,厚栅cmos管mn9漏级与薄栅晶体cmos管mn42源级以及电感l3下端、电感l15右端、电容c3上极板相连接,薄栅cmos管mn34栅极与控制信号sw1相连接,漏级与薄栅cmos管mn40漏级以及厚栅cmos管mn12栅极相连接,薄栅cmos管mn40栅极与控制信号sw1n相连接,源级与地相连接,厚栅cmos管mn12漏级与薄栅晶体cmos管mn44漏级相连接,薄栅cmos管mn33栅极与控制信号sw2相连接,漏级与薄栅cmos管mn39漏级以及厚栅cmos管mn1栅极相连接,薄栅cmos管mn39栅极与控制信号sw2n相连接,源级与地相连接,厚栅cmos管mn11漏级与薄栅cmos管mn44源级以及薄栅cmos管mn43漏级相连接,薄栅cmos管mn32栅极与控制信号sw3相连接,漏级与薄栅cmos管mn38漏级以及厚栅cmos管mn10栅极相连接,薄栅cmos管mn38栅极与控制信号sw3n相连接,源级与地相连接,厚栅cmos管mn10漏级与薄栅晶体cmos管mn43源级以及电感l4下端、电感l18右端、电容c6上极板相连接,薄栅cmos管mn41、mn44栅极均与控制信号sw1相连接,薄栅cmos管mn42、mn43栅极均与控制信号sw2相连接,电感l13、l14上端均与电源相连接,电感l15左端与电容c3下极板、电容c4上极板、电感l16右端相连接,电感l16左端与电容c4下极板、电容c5上极板、电感l17上端相连接至vout-,电感l17下端、电容c5下极板均与地相连接,电感l18右端与电容c6下极板、电容c7上极板、电感l19左端相连接,电感l19右端与电容c7下极板、电容c8上极板、电感l20上端相连接至vout+,电感l20下端、电容c8下极板均与地相连接。薄栅cmos管尺寸关系为:(mn1=mn6):(mn2=mn5):(mn3=mn4)=1:1:2,厚栅cmos管尺寸关系为(mn7=mn12):(mn8=mn11):(mn9=mn10)=1:1:2。

8、本发明与现有技术相比的有益效果是:

9、1、仅利用芯片内部开关切换,以及匹配网络的调整可实现工作类型、增益、功耗、工作频段等多维度参数调整,具有可重构性强特点;

10、2、该芯片基于单颗芯片实现,具有体积小易于片内集成的特点;

- 还没有人留言评论。精彩留言会获得点赞!