脉冲上升下降沿延迟电路及脉冲上升下降沿延迟芯片的制作方法

本发明涉及脉冲信号处理,尤其涉及一种脉冲上升下降沿延迟电路及脉冲上升下降沿延迟芯片。

背景技术:

1、当部分电路存在多个开关信号以控制该电路的启停时,若多个开关信号同步切换将为该电路带来信号噪声,干扰该电路的正常工作。因此,需要一种能够分别在上升沿和下降沿产生延迟信号组的开关脉冲信号以控制下级电路,从而解决上述同步开关切换导致的信号噪声问题。

技术实现思路

1、本发明提供一种脉冲上升下降沿延迟电路及脉冲上升下降沿延迟芯片,用以解决现有技术中多个开关信号同步切换为电路带来信号噪声,干扰电路正常工作的缺陷。

2、本发明提供一种脉冲上升下降沿延迟电路,包括:

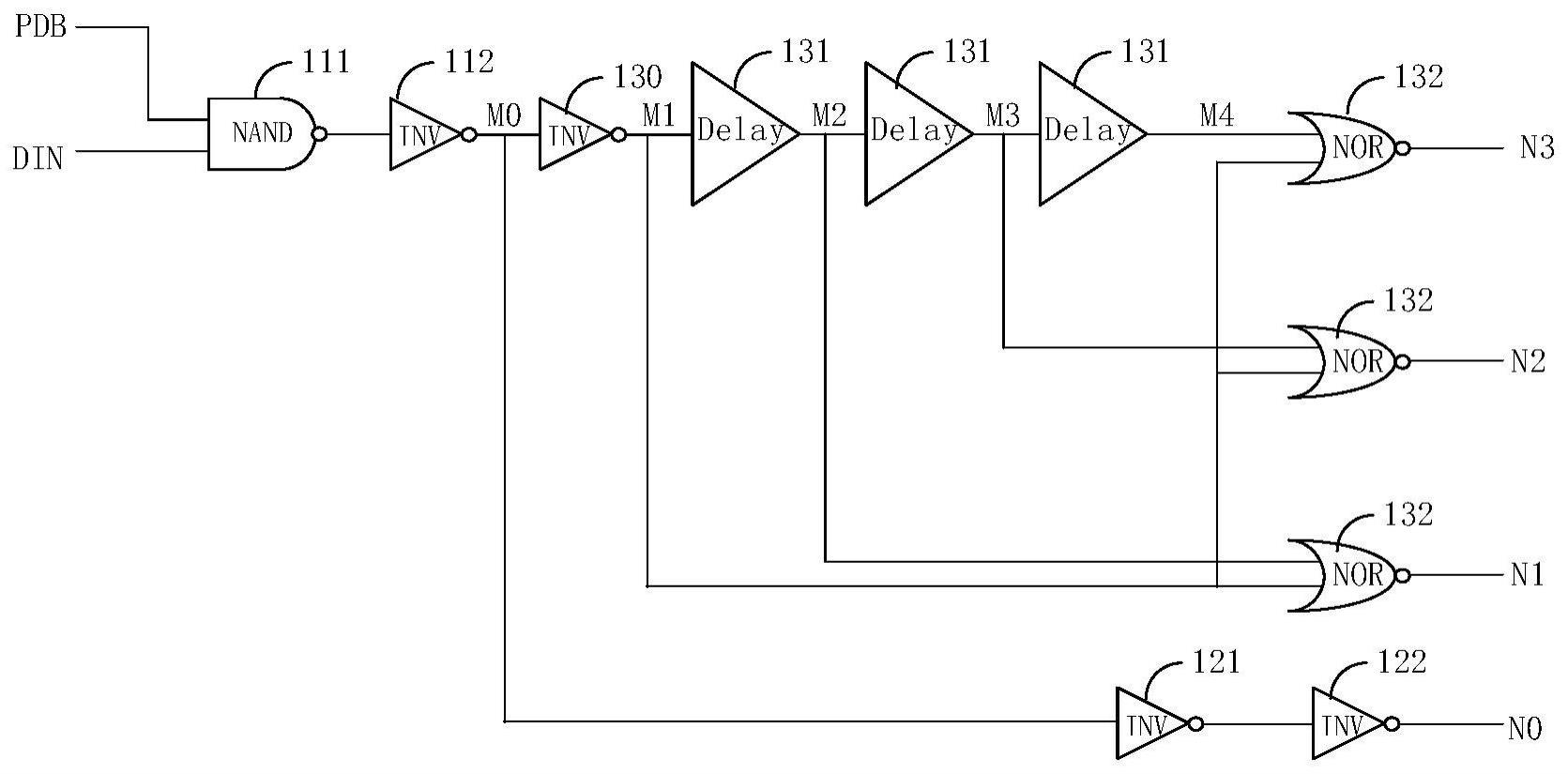

3、脉冲上升沿延迟电路;所述脉冲上升沿延迟电路包括第一原始信号处理单元、第一初始延迟信号生成单元和多个延迟程度递增的上升沿延迟单元;

4、其中,第一原始信号处理单元用于生成第一初始信号,其中包括串联的与非门和反相器;所述脉冲上升沿延迟电路的输入信号和通断控制信号与所述第一原始信号处理单元的与非门的输入端相连,所述第一原始信号处理单元的反相器输出所述第一初始信号;

5、第一初始延迟信号生成单元用于生成第一初始延迟信号,其中包括串联的两个反相器,且所述第一初始信号与所述第一初始延迟信号生成单元的首个反相器的输入端相连;

6、多个延迟程度递增的上升沿延迟单元用于对所述第一初始信号进行上升沿延迟并输出相应的上升沿延迟信号,任一上升沿延迟单元包括串联的信号延迟单元和或非门,所述任一上升沿延迟单元的信号延迟单元用于对反相的第一初始信号或前一上升沿延迟单元的信号延迟单元输出的信号进行延迟,所述任一上升沿延迟单元的或非门的输入端与所述任一上升沿延迟单元的信号延迟单元的输出端以及所述反相的第一初始信号相连。

7、根据本发明提供的一种脉冲上升下降沿延迟电路,所述第一初始延迟信号生成单元和每一所述上升沿延迟单元中还包括第一通断控制单元,用于开闭所述第一初始延迟信号生成单元和每一所述上升沿延迟单元的上升沿延迟功能;

8、其中,所述第一初始延迟信号生成单元的第一通断控制单元的输入端与所述第一初始延迟信号生成单元的第二个反相器的输出端以及所述通断控制信号相连,所述第一初始延迟信号生成单元的第一通断控制单元的输出端输出所述第一初始延迟信号;所述上升沿延迟单元的第一通断控制单元的输入端与所述上升沿延迟单元的或非门的输出端以及所述通断控制信号相连,所述上升沿延迟单元的第一通断控制单元的输出端输出相应的上升沿延迟信号。

9、根据本发明提供的一种脉冲上升下降沿延迟电路,所述第一通断控制单元包括串联的与非门和反相器;

10、所述第一初始延迟信号生成单元的第一通断控制单元中与非门的输入端与所述第一初始延迟信号生成单元的第二个反相器的输出端以及所述通断控制信号相连;所述上升沿延迟单元的第一通断控制单元中与非门的输入端与所述上升沿延迟单元的或非门的输出端以及所述通断控制信号相连;所述第一初始延迟信号生成单元的第一通断控制单元中反相器的输出端输出所述第一初始延迟信号;所述上升沿延迟单元的第一通断控制单元中反相器的输出端输出相应的上升沿延迟信号。

11、根据本发明提供的一种脉冲上升下降沿延迟电路,所述上升沿延迟单元中的信号延迟单元由若干个反相器串联而成,且所述上升沿延迟单元的信号延迟单元中反相器的数量为单数。

12、根据本发明提供的一种脉冲上升下降沿延迟电路,还包括脉冲下降沿延迟电路,所述脉冲下降沿延迟电路包括:

13、第二原始信号处理单元,用于生成第二初始信号,其中包括串联的或非门和反相器;所述脉冲下降沿延迟电路的输入信号和通断控制信号与所述第二原始信号处理单元的或非门的输入端相连,所述第二原始信号处理单元的反相器输出所述第二初始信号;

14、第二初始延迟信号生成单元,用于生成第二初始延迟信号,其中包括串联的两个反相器,且所述第二初始信号与所述第二初始延迟信号生成单元的首个反相器的输入端相连;

15、多个延迟程度递增的下降沿延迟单元,用于对所述第二初始信号进行下降沿延迟并输出相应的下降沿延迟信号,任一下降沿延迟单元包括串联的信号延迟单元和与非门,所述任一下降沿延迟单元的信号延迟单元用于对反相的第二初始信号或前一下降沿延迟单元的信号延迟单元输出的信号进行延迟,所述任一下降沿延迟单元的与非门的输入端与所述任一下降沿延迟单元的信号延迟单元的输出端以及所述反相的第二初始信号相连。

16、根据本发明提供的一种脉冲上升下降沿延迟电路,所述第二初始延迟信号生成单元和每一所述下降沿延迟单元中还包括第二通断控制单元,用于开闭所述第二初始延迟信号生成单元和每一所述下降沿延迟单元的下降沿延迟功能;

17、其中,所述第二初始延迟信号生成单元的第二通断控制单元的输入端与所述第二初始延迟信号生成单元的第二个反相器的输出端以及所述通断控制信号相连,所述第二初始延迟信号生成单元的第一通断控制单元的输出端输出所述第二初始延迟信号;所述下降沿延迟单元的第二通断控制单元的输入端与所述下降沿延迟单元的与非门的输出端以及所述通断控制信号相连,所述下降沿延迟单元的第二通断控制单元的输出端输出相应的下降沿延迟信号。

18、根据本发明提供的一种脉冲上升下降沿延迟电路,所述第二通断控制单元包括串联的或非门和反相器;

19、所述第二初始延迟信号生成单元的第二通断控制单元中或非门的输入端与所述第二初始延迟信号生成单元的第二个反相器的输出端以及所述通断控制信号相连;所述下降沿延迟单元的第二通断控制单元中或非门的输入端与所述下降沿延迟单元的与非门的输出端以及所述通断控制信号相连;所述第二初始延迟信号生成单元的第二通断控制单元中反相器的输出端输出所述第二初始延迟信号;所述下降沿延迟单元的第二通断控制单元中反相器的输出端输出相应的下降沿延迟信号。

20、根据本发明提供的一种脉冲上升下降沿延迟电路,所述下降沿延迟单元中的信号延迟单元由若干个反相器串联而成,且所述下降沿延迟单元的信号延迟单元中反相器的数量为单数。

21、根据本发明提供的一种脉冲上升下降沿延迟电路,所述脉冲下降沿延迟电路的通断控制信号为原始控制信号,所述脉冲上升沿延迟电路的通断控制信号为反相的所述原始控制信号。

22、本发明还提供一种脉冲上升下降沿延迟芯片,包括:

23、如上述任一种脉冲上升下降沿延迟电路的集成电路。

24、本发明提供的脉冲上升下降沿延迟电路及脉冲上升下降沿延迟芯片,通过生成第一/二初始信号的第一/二原始信号处理单元、生成第一/二初始延迟信号的第一/二初始延迟信号生成单元以及对第一/二初始信号进行上升/下降沿延迟并输出相应的上升/下降沿延迟信号的多个延迟程度递增的上升/下降沿延迟单元,输出脉冲呈现梯度变化,上升/下降沿逐渐延迟,实现了信号上升/下降沿不同程度的延迟,输入信号经过该电路后,可以在上升/下降沿产生延迟信号组,这组脉冲用于控制下级电路可以解决同步开关切换导致的信号噪声,且可以调节下级电路输出信号的上升/下降沿的时间。

- 还没有人留言评论。精彩留言会获得点赞!