基于二维材料异质结半浮栅结构的多功能逻辑存储器件

本发明属于半导体领域,具体涉及一种基于二维材料异质结半浮栅结构的多功能逻辑存储器件。

背景技术:

1、目前,快速发展的信息技术对快速运算和高效能运算设备的要求快速提升,然而,目前大规模使用的运算设备大都采用冯诺依曼架构,这种数据处理单元和数据存储单元相互分立的架构极大限制了传统计算机的运算速度和能源效率,开发超越冯诺依曼架构的新一代计算机势在必行。结合逻辑操作和数据存储的运算单元可以作为新型芯片超越冯诺依曼架构的突破口之一。

2、近些年来,随着对二维材料研究的深入,二维材料众多良好的性能诸如:超高的迁移率,无悬挂键的界面等优势表明其在存储器,发光二极管和光电探测器等低功耗器件领域有广泛的应用前景。运用二维材料可以通过弱范德华相互作用垂直组合成范德华异质结,这种异质结不受晶格失配的约束,可以制备基于二维材料异质结的浮栅存储器件。

3、现有的二维材料异质结浮栅存储器采用重掺杂硅衬底作为控制栅,sio2或者高k介质作为控制栅介质层,石墨烯作为浮栅,氮化硼作为隧穿层,过渡金属硫化物作为沟道层。

4、现有的二维材料异质结浮栅存储器虽然可以同时实现存储和逻辑计算功能,但无法在同一器件架构下实现存储功能和逻辑与,逻辑或,逻辑与非,逻辑或非和逻辑非这五项逻辑功能。因此,传统二维材料异质结浮栅存储器应用场景受限。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种基于二维材料异质结半浮栅结构的多功能逻辑存储器件。本发明要解决的技术问题通过以下技术方案实现:

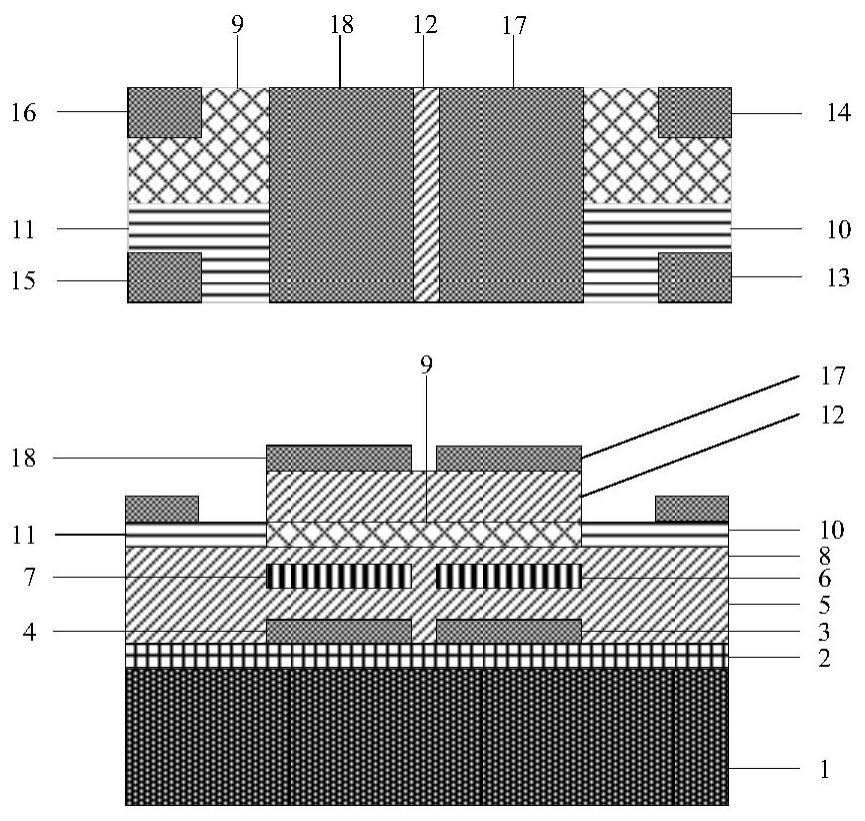

2、第一方面,本发明实施例提供了一种基于二维材料异质结半浮栅结构的多功能逻辑存储器件,包括:

3、半导体衬底;生长在所述半导体衬底上的绝缘介质层;生长在所述绝缘介质层表面的多个金属输入电极;生长在所述多个金属输入电极表面的第一二维材料绝缘介质层;生长在所述第一二维材料绝缘介质层表面的、多个平行间隔设置的二维材料浮栅层;生长在所述多个平行间隔设置的二维材料浮栅层表面的二维材料隧穿层;生长在所述二维材料隧穿层表面的n型二维材料沟道层,且所述n型二维材料沟道层通过刻蚀指定区域得到;生长在所述n型二维材料沟道层被刻蚀的指定区域内的、且与所述n型二维材料沟道层高度平齐的p型二维材料接触层;生长在所述n型二维材料沟道层表面的第二二维材料绝缘介质层,且所述第二二维材料绝缘介质层的区域与所述多个平行间隔设置的二维材料浮栅层的区域垂直对齐;生长在所述第二二维材料绝缘介质层表面的若干金属电极,包括金属输入电极、p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极;

4、其中,所述基于二维材料异质结半浮栅结构的多功能逻辑存储器件在实现存储器功能的基础上,通过选择一组对应的金属输入电极以及一组对应的源电极和漏电极进行电调制实现目标逻辑功能,所述目标逻辑功能包括逻辑与、逻辑或、逻辑与非、逻辑或非,以及逻辑非中的任意一种。

5、在本发明的一个实施例中,所述绝缘介质层的材料包括满足高介电常数要求的绝缘材料,包括hfo2,al2o3,zro2,hf0.5zr0.5o2,hf0.5al0.5o2,la0.5al0.5o2,sio2,la2o3;

6、所述第一二维材料绝缘介质层、所述第二二维材料绝缘介质层和所述二维材料隧穿层的材料包括满足禁带宽度较大要求的二维绝缘材料,包括cuinp2s6、h-bn;

7、所述二维材料浮栅层的材料包括石墨烯和过渡金属硫化物;其中,所述过渡金属硫化物包括mos2、ws2、res2、wse2、mose2、pts2、ptse2、rese2;

8、所述n型二维材料沟道层和所述p型二维材料接触层的材料包括满足高电子迁移率要求的二维过渡金属硫化物,包括mos2、ws2、res2、wse2、mose2、pts2、ptse2、rese2;

9、包含金属输入电极在内的金属电极包括任一种预设单种金属或者任意两种预设单种金属的堆叠;其中,所述预设单种金属包括钛、铬、钨、金、银、铂和铜。

10、第二方面,本发明实施例提供了一种基于二维材料异质结半浮栅结构的多功能逻辑存储器件的制备方法,用于制备第一方面所述的基于二维材料异质结半浮栅结构的多功能逻辑存储器件,所述方法包括:

11、步骤1,选取具有掺杂的半导体衬底进行标准rca清洗;

12、步骤2,在清洗后的半导体衬底表面生长绝缘介质层;

13、步骤3,在所述绝缘介质层表面制备多个金属输入电极;

14、步骤4,在所述多个金属输入电极表面生长第一二维材料绝缘介质层;

15、步骤5,在所述第一二维材料绝缘介质层表面生长多个二维材料浮栅层,且所述多个二维材料浮栅层在所述第一二维材料绝缘介质层表面平行间隔设置;

16、步骤6,在所述多个二维材料浮栅层表面生长二维材料隧穿层;

17、步骤7,在所述二维材料隧穿层表面生长n型二维材料沟道层;

18、步骤8,对生长出的n型二维材料沟道层表面的指定区域进行刻蚀得到特定图案;

19、步骤9,在刻蚀后的n型二维材料沟道层表面生长p型二维材料接触层;

20、步骤10,对生长出的p型二维材料接触层进行刻蚀以使得其仅位于所述n型二维材料沟道层被刻蚀的指定区域内且与所述n型二维材料沟道层高度平齐;

21、步骤11,在得到的n型二维材料沟道层表面生长第二二维材料绝缘介质层;

22、步骤12,刻蚀所述第二二维材料绝缘介质层表面以垂直对齐多个二维材料浮栅层所在区域;

23、步骤13,在所述第二二维材料绝缘介质层表面制备若干金属电极,包括金属输入电极、p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极。

24、在本发明的一个实施例中,所述步骤2中,生长绝缘介质层的方法包括原子层电极法或磁控溅射法;

25、所述步骤3中,制备多个金属输入电极的方法包括热蒸镀法、电子束蒸发法或转移电极法;

26、所述步骤4中,生长第一二维材料绝缘介质层的方法包括机械剥离法或化学气相淀积法;

27、所述步骤5中,生长多个二维材料浮栅层的方法包括机械剥离法或化学气相淀积法;

28、所述步骤6中,生长二维材料隧穿层的方法包括机械剥离法或化学气相淀积法;

29、所述步骤7中,生长n型二维材料沟道层的方法包括机械剥离法或化学气相淀积法;

30、所述步骤8中,采用的刻蚀方法包括等离子体刻蚀法;

31、所述步骤9中,生长p型二维材料接触层的方法包括机械剥离法或化学气相淀积法;

32、所述步骤10中,采用的刻蚀方法包括等离子气体刻蚀法;

33、所述步骤11中,生长第二二维材料绝缘介质层的方法包括机械剥离法或化学气相淀积法;

34、所述步骤12中,采用的刻蚀方法包括等离子气体刻蚀法;

35、所述步骤13中,制备若干金属电极的方法包括热蒸镀法、电子束蒸发法或转移电极法。

36、第三方面,本发明实施例提供了一种基于二维材料异质结半浮栅结构的多功能逻辑存储器件的电调控方法,用于对第一方面所述的基于二维材料异质结半浮栅结构的多功能逻辑存储器件进行电调控,所述方法包括:

37、针对任一目标逻辑功能,从所有金属输入电极中选择一组作为目标金属输入电极;从p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极中选择对应的一个源电极和一个漏电极作为目标金属输出电极;

38、在所述目标金属输入电极上输入适当的正电压作为输入电平值1,在所述目标金属输入电极上输入适当的负电压作为输入电平值0;将所述目标金属输出电极中的源电极接地,漏电极接适当的正电压,测量该源电极与该漏电极之间的电流作为输出,将输出的两种电流值中较小的作为输出电平值0,将输出的两种电流值中较大的作为输出电平值1,以实现该目标逻辑功能的电调控。

39、在本发明的一个实施例中,金属输入电极包括第一金属输入电极3、第二金属输入电极4、第三金属输入电极17和第四金属输入电极18;p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极分别为p端金属源电极13、n端金属源电极14、p端金属漏电极15和n端金属漏电极16;

40、相应的,当所述目标逻辑功能为逻辑与功能时,电调控的过程包括:

41、逻辑与功能情况一:

42、对应的目标金属输入电极包括所述第三金属输入电极17和所述第四金属输入电极18;对应的目标金属输出电极包括所述n端金属源电极14和所述n端金属漏电极16;

43、在所述第三金属输入电极17上输入负电压,在所述第四金属输入电极18上输入负电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入00,输出0;

44、在所述第三金属输入电极17上输入负电压,在所述第四金属输入电极18上输入正电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入01,输出0;

45、在所述第三金属输入电极17上输入正电压,在所述第四金属输入电极18上输入负电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入10,输出0;

46、在所述第三金属输入电极17上输入正电压,在所述第四金属输入电极18上输入正电压,所述n端金属源电极14和所述n端金属漏电极16之间输出大电流,表示情况:输入11,输出1;

47、逻辑与功能情况二:

48、对应的目标金属输入电极包括所述第一金属输入电极3和所述第二金属输入电极4;对应的目标金属输出电极包括所述p端金属源电极13和所述p端金属漏电极15;

49、在所述第一金属输入电极3上输入负电压,在所述第二金属输入电极4上输入负电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入00,输出0;

50、在所述第一金属输入电极3上输入负电压,在所述第二金属输入电极4上输入正电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入01,输出0;

51、在所述第一金属输入电极3上输入正电压,在所述第二金属输入电极4上输入负电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入10,输出0;

52、在所述第一金属输入电极3上输入正电压,在所述第二金属输入电极4上输入正电压,所述p端金属源电极13和所述p端金属漏电极15之间输出大电流,表示情况:输入11,输出1;

53、在本发明的一个实施例中,金属输入电极包括第一金属输入电极3、第二金属输入电极4、第三金属输入电极17和第四金属输入电极18;p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极分别为p端金属源电极13、n端金属源电极14、p端金属漏电极15和n端金属漏电极16;

54、相应的,当所述目标逻辑功能为逻辑或功能时,电调控的过程包括:

55、对应的目标金属输入电极包括所述第二金属输入电极4和所述第三金属输入电极17;对应的目标金属输出电极包括所述n端金属源电极14和所述p端金属漏电极15;

56、在所述第二金属输入电极4上输入负电压,在所述第三金属输入电极17上输入负电压,所述n端金属源电极14和所述p端金属漏电极15之间输出小电流,表示情况:输入00,输出0;

57、在所述第二金属输入电极4上输入负电压,在所述第三金属输入电极17上输入正电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入01,输出1;

58、在所述第二金属输入电极4上输入正电压,在所述第三金属输入电极17上输入负电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入10,输出1;

59、在所述第二金属输入电极4上输入正电压,在所述第三金属输入电极17上输入正电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入11,输出1;

60、在本发明的一个实施例中,金属输入电极包括第一金属输入电极3、第二金属输入电极4、第三金属输入电极17和第四金属输入电极18;p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极分别为p端金属源电极13、n端金属源电极14、p端金属漏电极15和n端金属漏电极16;

61、相应的,当所述目标逻辑功能为逻辑与非功能时,电调控的过程包括:

62、对应的目标金属输入电极包括所述第一金属输入电极3和所述第四金属输入电极18;对应的目标金属输出电极包括所述n端金属源电极14和所述p端金属漏电极15;

63、在所述第一金属输入电极3上输入负电压,在所述第四金属输入电极18上输入负电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入00,输出1;

64、在所述第一金属输入电极3上输入负电压,在所述第四金属输入电极18上输入正电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入01,输出1;

65、在所述第一金属输入电极3上输入正电压,在所述第四金属输入电极18上输入负电压,所述n端金属源电极14和所述p端金属漏电极15之间输出大电流,表示情况:输入10,输出1;

66、在所述第一金属输入电极3上输入正电压,在所述第四金属输入电极18上输入正电压,所述n端金属源电极14和所述p端金属漏电极15之间输出小电流,表示情况:输入11,输出0;

67、在本发明的一个实施例中,金属输入电极包括第一金属输入电极3、第二金属输入电极4、第三金属输入电极17和第四金属输入电极18;p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极分别为p端金属源电极13、n端金属源电极14、p端金属漏电极15和n端金属漏电极16;

68、相应的,当所述目标逻辑功能为逻辑或非功能时,电调控的过程包括:

69、逻辑或非功能情况一:

70、对应的目标金属输入电极包括所述第三金属输入电极17和所述第四金属输入电极18;对应的目标金属输出电极包括所述p端金属源电极13和所述p端金属漏电极15;

71、在所述第三金属输入电极17上输入负电压,在所述第四金属输入电极18上输入负电压,所述p端金属源电极13和所述p端金属漏电极15之间输出大电流,表示情况:输入00,输出1;

72、在所述第三金属输入电极17上输入负电压,在所述第四金属输入电极18上输入正电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入01,输出0;

73、在所述第三金属输入电极17上输入正电压,在所述第四金属输入电极18上输入负电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入10,输出0;

74、在所述第三金属输入电极17上输入正电压,在所述第四金属输入电极18上输入正电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入11,输出0;

75、逻辑或非功能情况二:

76、对应的目标金属输入电极包括所述第一金属输入电极3和所述第二金属输入电极4;对应的目标金属输出电极包括所述n端金属源电极14和所述n端金属漏电极16;

77、在所述第一金属输入电极3上输入负电压,在所述第二金属输入电极4上输入负电压,所述n端金属源电极14和所述n端金属漏电极16之间输出大电流,表示情况:输入00,输出1;

78、在所述第一金属输入电极3上输入负电压,在所述第二金属输入电极4上输入正电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入01,输出0;

79、在所述第一金属输入电极3上输入正电压,在所述第二金属输入电极4上输入负电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入10,输出0;

80、在所述第一金属输入电极3上输入正电压,在所述第二金属输入电极4上输入正电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入11,输出0;

81、在本发明的一个实施例中,金属输入电极包括第一金属输入电极3、第二金属输入电极4、第三金属输入电极17和第四金属输入电极18;p端金属源电极、n端金属源电极、p端金属漏电极和n端金属漏电极分别为p端金属源电极13、n端金属源电极14、p端金属漏电极15和n端金属漏电极16;

82、相应的,当所述目标逻辑功能为逻辑非功能时,电调控的过程包括:

83、逻辑非功能情况一:

84、对应的目标金属输入电极包括所述第三金属输入电极17和所述第四金属输入电极18;对应的目标金属输出电极包括所述p端金属源电极13和所述p端金属漏电极15;

85、在所述第三金属输入电极17和所述第四金属输入电极18上输入负电压,所述p端金属源电极13和所述p端金属漏电极15之间输出大电流,表示情况:输入0,输出1;

86、在所述第三金属输入电极17和所述第四金属输入电极18上输入正电压,所述p端金属源电极13和所述p端金属漏电极15之间输出小电流,表示情况:输入1,输出0;

87、逻辑非功能情况二:

88、对应的目标金属输入电极包括所述第一金属输入电极3和所述第二金属输入电极4;对应的目标金属输出电极包括所述n端金属源电极14和所述n端金属漏电极16;

89、在所述第一金属输入电极3和所述第二金属输入电极4上输入负电压,所述n端金属源电极14和所述n端金属漏电极16之间输出大电流,表示情况:输入0,输出1;

90、在所述第一金属输入电极3和所述第二金属输入电极4上输入正电压,所述n端金属源电极14和所述n端金属漏电极16之间输出小电流,表示情况:输入1,输出0。

91、本发明的有益效果:

92、本发明实施例提出的基于二维材料异质结半浮栅结构的多功能逻辑存储器件,通过改良器件结构并在多个金属电极中选择对应的输入电极和输出电极,通过电调控方式控制电极电压来实现任一种功能逻辑以及实现不同功能逻辑的快速切换,因此,可以在实现存储功能的基础上,在同一器件上集成逻辑与、逻辑或、逻辑与非、逻辑或非和逻辑非这五项逻辑功能,可用于简化集成电路结构,减少集成电路器件数目,提高集成电路集成度,提升运算速度,减少运算能耗,有助于逻辑存储器件应用于新一代低功耗集成电路芯片中。

- 还没有人留言评论。精彩留言会获得点赞!