一种无复位功耗双向动态比较器及其信号采集系统和应用

本发明涉及集成电路,具体是一种无复位功耗双向动态比较器及其信号采集系统和应用。

背景技术:

1、在能量受限的应用领域,如无线传感器和生物医学植入物,功率高效的模数转换器(adc)具有重要意义,在这些场景中,adc 扮演着关键角色,用于将感测信号转换为数字形式进行处理。此时,选择适当的adc类型对于实现长时间的稳定运行和高效能量管理至关重要。而逐次逼近模数转换器(sar adc)在这方面具备明显的优势,能够平衡性能和功耗需求,为无线传感器和生物医学植入物等领域提供可靠的数字信号转换解决方案。

2、sar adc的工作原理以逐步逼近为基础,通过逐个比特位的精确逼近,完成对输入模拟信号的精确数字化表示。起初,模拟信号经过采样后被保持,随后逼近寄存器的比特位从最高位开始逐一设定。在每一步中,都需要逼近值与输入信号进行比较,指引比特位是保持为1还是重置为0。这个逐步比较的过程会持续进行,直到所有比特位都经过处理。

3、由于sar adc这一特殊的工作原理,导致比较器的功耗非常大,通常占整个adc的40%,这对减少功耗十分不利。强臂(strongarm)动态比较器由于没有静态电流,减小了比较器本身需要的功耗。但由于其单级的架构,锁存级与预放大级之间没有隔离,strongarm比较器的噪声性能受到锁存级回踢噪声的影响而变差。双尾电流型(double-tail)静态比较器预防大级不存在动态开关的,不存在晶体管的导通与关断,所以不受回踢噪声的影响,但由于其一直存在对地通路,静态功耗也相当显著。

4、针对强臂比较器噪声性能差而静态比较器的功耗过高这一问题,目前通常采用双尾电流型(double-tail)动态比较器。该比较器通过预防大级别与锁存级分离的两级结构,减小锁存级的回踢噪声;同时,通过开关控制,仅在比较阶段存在对地电流通路,仅有动态功耗不存在静态功耗。但其复位功耗无法避免,每一次比较结束之后都需要对预防大级的输出节点电容进行充放电复位,造成了额外功耗。

5、为此,针对以上各种比较器目前存在的缺陷,本发明提出了一种应用于逐次逼近模数转换器中的无复位功耗双向动态比较器解决上述技术问题。

技术实现思路

1、本发明的目的在于提供一种无复位功耗双向动态比较器及其信号采集系统和应用,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:一种无复位功耗双向动态比较器,所述比较器结构采用预防大级与锁存级分离的两级结构,所述比较器包括用于双向比较的预防大级、用于充电速度比较的第一锁存级和用于放电速度比较的第二锁存级。

3、进一步的,所述预防大级包括用于采样阶段复位的pmos管m6/m7、用于控制放电电流通路与充电电流通路的尾电流管m0/m5、用于对p/n节点电容放电速度比较的nmos输入对管m1/m2以及用于充电速度比较的pmos输入对管m3/m4;所述m5的栅极连接时钟信号clkp,m5的漏极连接所述m3和m4的源极;所述m3的漏极节点p,同时连接m1和m6的漏极;所述m3和m1的栅极连接输入信号vinp;所述m4的漏极节点n,同时连接m2和m7的漏极;所述m4和m2的栅极连接输入信号vinn;所述m6和m7的栅极连接时钟信号clks;所述m1和m2的源极连接m0的漏极,所述m0的栅极连接时钟信号clkn;所述m6/m7在采样阶段导通,将p/n节点电容充电到vdd。

4、进一步的,所述第一锁存级包括pmos管m8、pmos管m9、pmos管m10、nmos管m11、nmos管m12、nmos管m13和nmos管m14;所述m8源极连接与vdd连接,所述m8的漏极连接所述m9和m10的源极,所述m8的栅极与时钟控制信号相连接,所述m9的漏极连接到输出节点outp1,同时连接到所述m11、m12的漏极以及所述m10和m13的栅极;所述m10漏极连接到输出节点outn1,同时连接到所述m13、m14的漏极以及所述m9和m12的栅极;所述m11栅极连接节点p,所述m8栅极连接节点n。

5、进一步的,所述第二锁存级包括nmos管m15、nmos管m16、nmos管m17、pmos管m18、pmos管m19、pmos管m20、pmos管m21;所述m11、m12、m13、m14的源极与vdd连接,所述m15的漏极连接所述m16和m17的源极,所述m15的栅极与时钟控制信号相连接,所述m16的漏极连接到输出节点outp2,同时连接到所述m18、m19的漏极以及所述m20和m17的栅极;所述m17漏极连接到输出节点outn2,同时连接到所述m20、m21的漏极以及所述m16和m19的栅极;所述m18栅极连接节点p,所述m21栅极连接节点n。

6、进一步的,所述用于放电速度比较的第一锁存级,当p/n节点电容处的电位下降(vdd-vthn)时,输入对管nmos管m11/m14关断,第一锁存级启动,将比较结果锁存输出;其中,vdd为电源电压,vthn为nmos管m11/m14的阈值电压(vthn)。

7、进一步的,所述用于充电速度比较的第二锁存级,当p/n节点电容处的电位上升vthp时,pmos管m18/m21关断,第二锁存级启动,将比较结果锁存输出;其中,vthp为pmos管m18/m21的阈值电压(vthp)。

8、进一步的,所述的一种应用于逐次逼近模数转换器中的无复位功耗双向动态比较器,其特征在于,所述的预防大级增益(pre amp)与p/n节点电容、锁存级输入对管的启动电压关系的表达式为:

9、;

10、;

11、;

12、其中,为第一锁存级/ 第二锁存级输入对管关断、锁存器启动时的启动电压;为预防大级尾电流管m0/m5的导通电流;为预防大级p/n节点的节点电容;为从比较阶段开始到锁存级启动所需要的时间;为预防大级输入对m1/m2或m3/m4的跨导;为预防大级的增益。

13、进一步的,所述的一种应用于逐次逼近模数转换器中的无复位功耗双向动态比较器,其特征在于,所述比较器的等效输入噪声()与p/n节点电容()、锁存级输入对管的启动电压()和跨导()关系的表达式为:

14、;

15、;

16、;

17、其中,为预防大级输入对管m1/m2和m3/m4栅极的等效热电阻;为mos管的噪声系数;为噪声的积分带宽;k是玻尔兹曼常数;t是绝对温度。

18、进一步的,所述一种应用于逐次逼近模数转换器中的无复位功耗双向动态比较器,其特征在于,比较器无需额外的复位阶段,该比较器通过nmos输入对与pmos输入对交替执行比较功能,前一次比较结束正好为后一次比较提供了复位状态,比较阶段无需额外的复位步骤,减少了比较器预防大级别一半的功耗,所述比较器的功耗( e c)与p/n节点电容()、电源电压(vdd)关系的表达式为:

19、;

20、;

21、其中, 为电源电压;为常规动态比较器的功耗;为提出的无复位功耗双向动态比较器的功耗,有上式可知,所述的无复位功耗双向动态比较器无需复位,故功耗仅为传统动态比较器的一半。

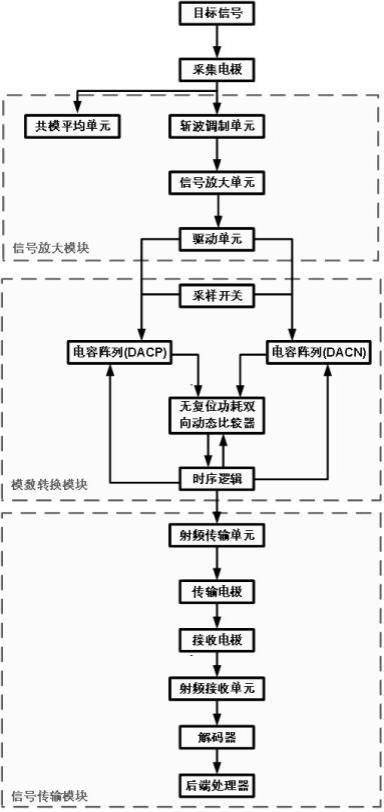

22、本发明提供了一种基于上述比较器的信号采集系统,包括:

23、信号放大模块:用于对输入信号中的目标信号进行放大处理,得到放大的目标信号;

24、模数转换模块:用于将放大的目标信号进行转换,编码和传输形成转换后的数字信号,并将转换后的数字信号传输至用户电极;

25、信号传输模块:用于对模数转换模块输出的数字信号进行接收、传输、解码和处理形成得到最终的目标信号。

26、进一步的,所述信号放大模块包括斩波调制单元、固定增益放大单元和共模平均单元;所述斩波调制单元用于将目标信号进行斩波调制,输出斩波调制后的脑电信号;所述固定增益放大器单元用于将脑电信号进行放大处理;所述共模平均单元:用于将输入信号中的共模干扰信号动态耦合至接地端和电源端。

27、进一步的,所述模数转换模块包括比较器、电容阵列、采样开关和逐次逼近逻辑;所述电容阵列采用分段电容阵列的形式;所述采样开关采用上极板采样的栅压自举开关;所述逐次逼近逻辑采用同步时序逻辑。

28、进一步的,所述信号传输模块包括射频传输单元、传输电极、接收电极、射频接收单元、解码器、后端数据处理单元;所述射频传输单元:用于将串行的数字信号通过传输电极传输至接收电极;所述射频接收单元:用于接收串行的数字信号,并传输至解码器;所述解码器:用于对串行的数字信号解码并传输至后端数据处理单元;所述后端处理器:用于将解码后的数字信号处理得到最终的目标信号。

29、本发明还提供一种信号采集系统在逐次逼近模数转换器中的应用,其特征在于,包括以下步骤:

30、步骤s1:信号采集设备的采集电极将采集到的输入信号通过信号放大通路的输入端传输至信号放大模块,所述信号放大模块对所述输入信号中的目标信号进行放大处理,得到放大的目标信号;

31、步骤s2:采样阶段所述的放大的目标信号传输至逐次逼近模数转换器,由一个高线性度低失真的栅压自举采样开关将所述放大的目标信号采样至电容阵列的上极板;同时,逐次逼近模数转换器中时序逻辑对电容阵列的下极板进行复位;

32、步骤s3:比较阶段比较器根据输入电压的大小,得出比较结果,比较结束后,时序逻辑会根据上次的比较结果对电容阵列的下极板进行置位,置位完成后,进行下一次比较,依此重复直至所有比特所有位都完成;

33、步骤s4:通过所述逐次逼近模数转换器转换后的数字信号传输至信号接收及处理模块;通过所述信号传输模块进行接收,解码和处理得到最终的目标信号。

34、进一步的,所述步骤s4具体包括以下子步骤:通过所述接收电极将转换后的数字信号传输至射频接收单元,并将数字信号通过译码器进行解码,并将解码后的数字信号通过后端处理器处理得到最终的目标信号。

35、与现有技术相比,本发明的有益效果是:逐次逼近模数转换器(sar adc)在能量受限的应用领域有着广泛的使用,在这些应用场景中,sar adc的功耗是其关键指标。而比较器是影响sar adc功耗的核心模块。本发明首先通过由全动态时序来控制比较器的工作,仅在比较阶段存在对地通路,当不处于比较阶段时,晶体管关断,不存在对地通路,无静态功耗,极大的减小了比较器的功耗;同时,由于双向比较策略的存在,nmos输入对与pmos输入对交替执行比较功能,前一次比较结束正好为后一次比较提供了复位状态,比较阶段无需额外的复位步骤,无复位功耗,减少了比较器预防大级别一半的功耗。最后,预防大级与锁存级分离的两级结构极大的减小了锁存级耦合到预防大级的回踢噪声。

- 还没有人留言评论。精彩留言会获得点赞!