一种4H-SiCMOSFET的宽温度范围逻辑门电路结构

本发明属于集成电路,涉及一种4h-sic mosfet的宽温度范围逻辑门电路结构。

背景技术:

1、现有的逻辑门使用n型金属-氧化物-半导体(n-metal-oxide-semiconductor,nmos)和p型金属-氧化物-半导体(n-metal-oxide-semiconductor,pmos),由于其阈值电压量受温度的影响有差异,当电路工作温度升高,上拉网络即pmosfet信号上拉能力变强,下拉网络即nmosfet信号下拉能力变强,但是二者的变化量并不相同,因此,互补金属氧化物半导体(complementary metal oxide semiconductor,cmos)非门、与非门和或非门的开关阈值会受到温度的影响。因此,需要设计宽温度范围的电路。

2、在4h-sic金氧半场效晶体管(metal-oxide-semiconductor field-effecttransistor,mosfet)的宽温度范围电路设计方法中,数字电路设计是重要的一环,简单非门、与非门和或非门三种逻辑运算的实现,可以满足数字电路设计的基础要求。但是,由于4h-sic器件的空穴迁移率低,4h-sic mosfet制造的数字逻辑门其上拉与下拉网络受温度影响后的改变量差别较大,会导致在大温度跨度下电路性能的不稳定,因此常用的硅基cmos数字逻辑门电路结构无法直接应用到4h-sic集成电路中。所以,对4h-sic mosfet构成的数字逻辑门进行研究和设计非常必要。

技术实现思路

1、本发明的目的是提供一种4h-sic mosfet的宽温度范围逻辑门电路结构。本发明所采用的技术方案是:

2、一种4h-sic mosfet的宽温度范围逻辑门电路结构,包括至少两个mos管,各个所述mos管按照预设连接关系进行连接,以使逻辑门电路实现相应的逻辑运算;

3、所述逻辑门电路包括逻辑非门电路、逻辑与非门电路和逻辑或非门电路;

4、所述预设连接关系为非门连接关系、与非门连接关系和或非门连接关系;

5、所述mos管均为4h-sic mosfet器件。

6、在本发明的一个实施例中,所述逻辑运算包括非逻辑、与非逻辑和或非逻辑;

7、所述逻辑非门电路中,当输入为高电平时,电路输出低电平,当输入信号为低电平时,电路输出信号为高电平;

8、所述逻辑与非门电路中,当两输入信号均为高电平时,电路输出低电平,其余情况下均输出高电平;

9、所述逻辑或非门电路中,当两输入信号均为低电平时,电路输出信号为高电平,其余情况下均输出低电平。

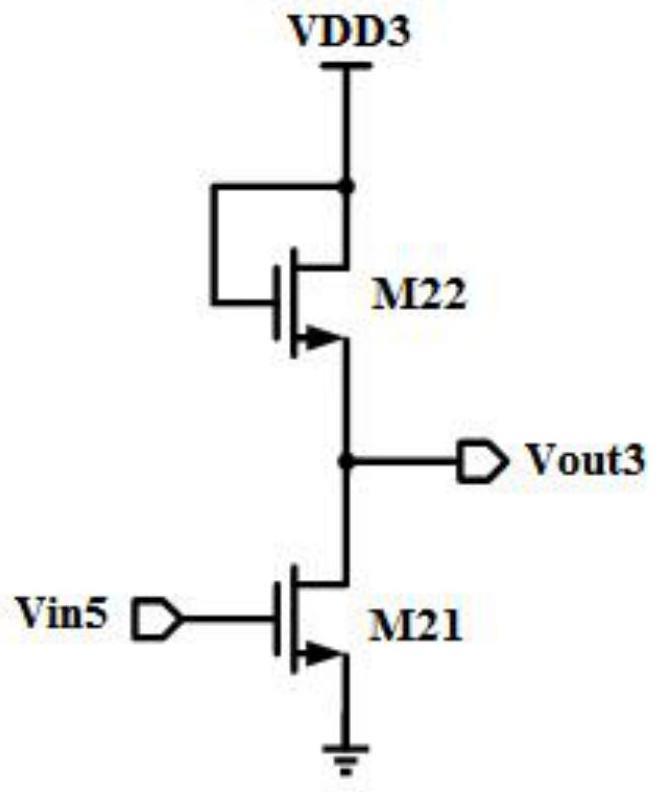

10、在本发明的一个实施例中,所述逻辑非门电路包括第二十一mos管m21和第二十二mos管m22;

11、所述第二十一mos管m21的源极接地,所述第二十一mos管m21的栅极与第五信号输入端vin5连接,所述第二十一mos管m21的漏极和所述第二十二mos管m22的源极均与第三信号输出端vout3连接,所述第二十二mos管m22的漏极和栅极均与第三输入电源端vdd3连接。

12、在本发明的一个实施例中,所述逻辑与非门电路包括:第一mos管m1、第二mos管m2、第三mos管m3、第四mos管m4、第五mos管m5、第六mos管m6、第七mos管m7、第八mos管m8、第九mos管m9、第十mos管m10和第一电阻r1;

13、所述第一mos管m1的栅极与第一信号输入端vin1连接,所述第九mos管m9的栅极与第二信号输入端vin2连接,所述第一mos管m1的漏极和所述第二mos管m2的源极均与所述第三mos管m3的栅极连接,所述第三mos管m3的漏极和所述第四mos管m4的源极与所述第六mos管m6的栅极连接,所述第九mos管m9的漏极和所述第十mos管m10的源极与所述第七mos管m7的栅极连接,所述第七mos管m7的漏极和所述第八mos管m8的源极与所述第五mos管m5的栅极连接,所述第五mos管m5的漏极与所述第六mos管m6的源极连接,所述第一mos管m1的源极、所述第三mos管m3的源极、所述第五mos管m5的源极、所述第七mos管m7的源极和所述第九mos管m9的源极均接地,所述第一电阻r1的一端与所述第二mos管m2的栅极和漏极、所述第四mos管m4的栅极和漏极、所述第八mos管m8的栅极和漏极、所述第十mos管m10的栅极和漏极均与第一输入电源端vdd1连接,所述第一电阻r1的另一端和所述第六mos管m6的漏极均与第一信号输出端vout1连接。

14、在本发明的一个实施例中,所述逻辑或非门电路包括:第十一mos管m11、第十二mos管m12、第十三mos管m13、第十四mos管m14、第十五mos管m15、第十六mos管m16、第十七mos管m17、第十八mos管m18、第十九mos管m19、第二十mos管m20和第二电阻r2;

15、所述第十一mos管m11的栅极与第三信号输入端vin3连接,所述第十九mos管m19的栅极与第四信号输入端vin4连接,所述第十一mos管m11的漏极和所述第十二mos管m12的源极均与所述第十三mos管m13的栅极连接,所述第十三mos管m13的漏极和第十四mos管m14的源极均与第十五mos管m15的栅极连接,所述第十九mos管m19的漏极和所述第二十mos管m20的源极均与第十七mos管m17的栅极连接,所述第十七mos管m17的漏极和所述第十八mos管m18的源极均与所述第十六mos管m16的栅极连接,所述第十一mos管m11的源极、所述第十三mos管m13的源极、所述第十五mos管m15的源极、所述第十六mos管m16的源极、所述第十七mos管m17的源极、所述第十九mos管m19的源极均接地,所述第二电阻r2的一端与所述第十二mos管m12的栅极和漏极、所述第十四mos管m14的栅极和漏极、所述第十八mos管m18的栅极和漏极、所述第二十mos管m20的栅极和漏极均与第二输入电源端vdd2连接,所述第二电阻r2的另一端、所述第十六mos管m16的漏极和所述第十五mos管m15的漏极均与第二信号输出端vout2连接。

16、在本发明的一个实施例中,所述逻辑非门电路是由两个增强型nmos管构成的e/e饱和负载nmos反相器。

17、在本发明的一个实施例中,当输入信号为低电平时,所述第二十一mos管m21管关断,所述第二十二mos管m22管开通作为上拉网络,输出端被拉高;当输入信号由低电平转高电平时,所述第二十一mos管m21管逐渐打开作为下拉网络,所述第二十二mos管m22管一直开通,所述第二十一mos管m21的vgs1值会逐渐超过所述第二十二mos管m22管,下拉能力逐渐增强;当输入信号彻底为高电平时,输出端被拉低。

18、在本发明的一个实施例中,所述e/e饱和负载nmos反相器中两个nmos宽长比相等时,所述逻辑非门电路的开关阈值稳定在所述第三输入电源端vdd3所给电压的一半。

19、在本发明的一个实施例中,所述逻辑与非门电路和所述逻辑或非门电路均以两级所述逻辑非门电路作为信号输入端,当所述逻辑非门电路中nmos宽长比一致时,所述逻辑与非门电路和所述逻辑或非门电路的信号输入端将不会有开关阈值的变化。

20、本发明的有益效果:

21、本发明的宽温度范围逻辑门电路结构,包括逻辑非门电路、逻辑与非门电路和逻辑或非门电路,能够实现全部为4h-sic mosfet构成的逻辑门电路在25℃到500℃范围内稳定工作,可以适应不同半导体材料的mos管温度特性,具有普适性,而且电路结构复杂度低,可用于各种电路中产生参考电压。

- 还没有人留言评论。精彩留言会获得点赞!