电平转换电路的制作方法

本发明涉及一种半导体集成电路,特别是涉及一种电平转换电路(levelshifter)。

背景技术:

1、如图1所示,是现有电平转换电路的电路图;电平转换电路的下拉管包括第一nmos管mn101和第二nmos管mn102。所述电平转换电路的上拉管包括第一pmos管mp101和第二pmos管mp102。在仿真模型中,高压nmos管也称为nchh,高压pmos管也称为pchh。

2、所述第一nmos管mn101的栅极连接所述输入信号in。所述输入信号in还连接到反相器101的输入端,所述反相器101的输出端输出所述反相输入信号,所述第二nmos管mn102的栅极连接所述反相输入信号。

3、所述输入信号in的高电平为第一电源电压。

4、所述第一pmos管mp101的源极和所述第二pmos管mp102的源极都连接所述第二电源电压vsp。所述第二电源电压vsp大于第一电源电压,所述第一电源电压为芯片如闪存的内部电源电压,所述第二电源电压vsp则需要在所述闪存的内部电源电压的基础上通过电荷泵电路的升压得到。

5、所述第一pmos管mp101的漏极、所述第一nmos管mn101的漏极和所述第二pmos管mp102的栅极连接在一起并作为所述反相输出信号outb的输出端。

6、所述第二pmos管mp102的漏极、所述第二nmos管mn102的漏极和所述第一pmos管mp101的栅极连接在一起并作为所述正相输出信号out的输出端。

7、所述输出信号由一对互为反相的所述正相输出信号out和所述反相输出信号outb组成。

8、图1所示的现有电平转换电路通常应用于闪存(flash)的译码(decoder)电路中,55nm的flash的电源电压即所述第一电源电压是1.2v,实际仿真需要考虑1.05v,在sf/sflt工艺角(corner)下,nchh的管子要非常大如沟道宽度为16微米即w=16μm才能翻转5v~7v的所述第二电源电压vsp,这造成了decoder面积的大大增加,使得55nm flash知识产权核(ip)面积偏大。

技术实现思路

1、本发明所要解决的技术问题是提供一种电平转换电路,能增加高压电平转换电路的下拉管的沟道宽度的驱动能力且不是通过增加下拉管的沟道宽度来增加下拉管的驱动能力,从而能保证高压电平转换电路实现很好的翻转的同时减少下拉管的沟道宽度,从而减少芯片面积。

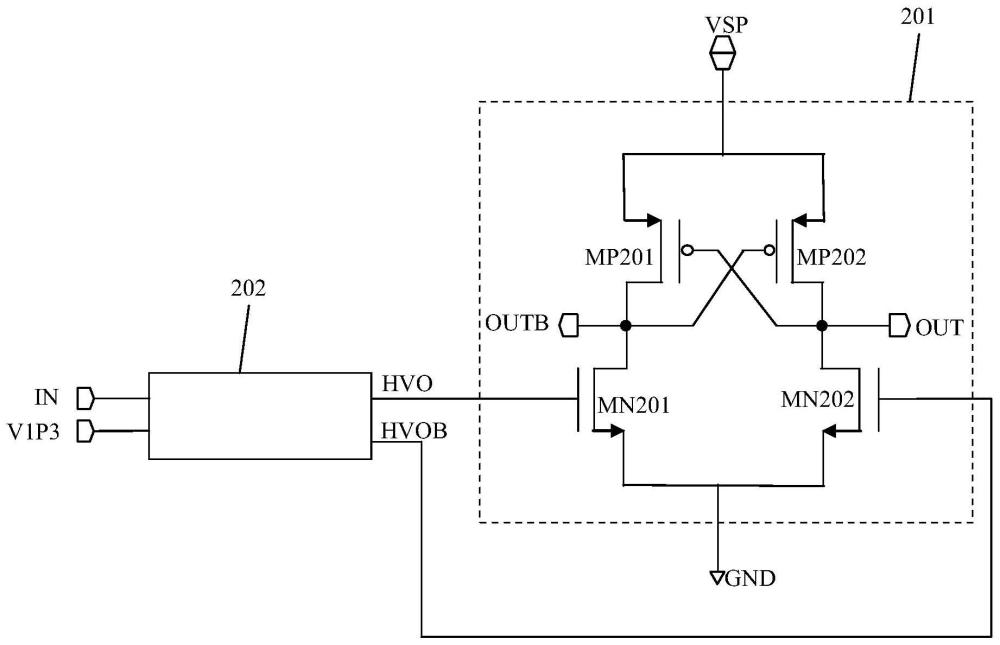

2、为此解决上述技术问题,本发明提供的电平转换电路包括:辅助电平转换电路和主体电平转换电路。

3、所述辅助电平转换电路的输入端连接输入信号,所述输入信号的高电平为第一电源电压。

4、所述辅助电平转换电路的电源端连接第二电源电压,所述辅助电平转换电路输出第一输出信号,所述第一输出信号的高电平为所述第二电源电压;所述第二电源电压高于所述第一电源电压。

5、所述主体电平转换电路的输入端连接所述第一输出信号,所述主体电平转换电路的电源端连接第三电源电压,所述主体电平转换电路输出第二输出信号,所述第二输出信号的高电平为所述第三电源电压;所说第三电源电压高于所述第二电源电压。

6、所述主体电平转换电路包括下拉管和上拉管,所述主体电平转换电路的下拉管的栅极为所述主体电平转换电路的输入端。

7、在所述主体电平转换电路的下拉管导通时,所述第一输出信号的高电平用于增加所述主体电平转换电路的下拉管的下拉电流,从而减少实现所述第二输出信号的翻转所需要的所述主体电平转换电路的下拉管的沟道宽度。

8、进一步的改进是,所述主体电平转换电路的下拉管和上拉管都采用工作电压大于所述第三电源电压的高压管。

9、进一步的改进是,所述主体电平转换电路的下拉管包括第一nmos管和第二nmos管。

10、所述主体电平转换电路的上拉管包括第一pmos管和第二pmos管。

11、所述第一pmos管的源极和所述第二pmos管的源极都连接所述第三电源电压。

12、所述第一pmos管的漏极、所述第一nmos管的漏极和所述第二pmos管的栅极连接在一起并作为所述第二反相输出信号的输出端。

13、所述第二pmos管的漏极、所述第二nmos管的漏极和所述第一pmos管的栅极连接在一起并作为所述第二正相输出信号的输出端。

14、所述第二输出信号由一对互为反相的所述第二正相输出信号和所述第二反相输出信号组成。

15、所述第一nmos管的栅极连接第一正相输出信号,所述第二nmos管的栅极连接第一反相输出信号;所述第一输出信号由一对互为反相的所述第一正相输出信号和所述第一反相输出信号组成。

16、所述第一nmos管的源极和所述第二nmos管的源极都接地。

17、进一步的改进是,所述辅助电平转换电路的下拉管和上拉管都采用低压管,所述低压管的工作电压大于所述第二电源电压且小于所述第三电源电压。

18、进一步的改进是,所述辅助电平转换电路的下拉管包括第三nmos管和第四nmos管。

19、所述辅助电平转换电路的上拉管包括第三pmos管和第四pmos管。

20、所述第三pmos管的源极和所述第四pmos管的源极都连接所述第二电源电压。

21、所述第三pmos管的漏极、所述第三nmos管的漏极和所述第四pmos管的栅极连接在一起并作为所述第一反相输出信号的输出端。

22、所述第四pmos管的漏极、所述第四nmos管的漏极和所述第三pmos管的栅极连接在一起并作为所述第一正相输出信号的输出端。

23、所述第一输出信号由一对互为反相的所述第二正相输出信号和所述第二反相输出信号组成。

24、所述第三nmos管的栅极连接所述输入信号。

25、所述输入信号还连接到反相器的输入端,所述反相器的输出端输出所述反相输入信号,所述第四nmos管的栅极连接所述反相输入信号。

26、进一步的改进是,电平转换电路作为闪存的译码电路的组成部分。

27、进一步的改进是,所述第一电源电压为所述闪存的内部电源。

28、进一步的改进是,所述第二电源电压为所述闪存的内部电源。

29、或者,所述第二电源电压由ldo电路输出得到,所述ldo电路的电源端连接第四电源电压,所述第四电源电压也为所述闪存的内部电源且大于所述第一电源电压。

30、或者,所述第二电源电压由第一电荷泵电路输出得到,所述第一电荷泵电路的电源端连接所述第一电源电压。

31、进一步的改进是,所述第三电源电压由第二电荷泵电路输出得到,所述第二电荷泵电路的电源端连接所述第一电源电压。

32、进一步的改进是,所述闪存的工艺节点包括50nm。

33、进一步的改进是,所述闪存的工艺节点包括50nm或40nm以下。

34、进一步的改进是,所述闪存的工艺节点越小,所述第一电源电压越小;50nm工艺节点对应的所述第一电源电压为1.2v且具有±10%的波动,40nm工艺节点对应的所述第一电源电压为1.1v且具有±10%的波动。

35、进一步的改进是,所述第二电源电压取为所述第一电源电压的1.1倍。

36、进一步的改进是,所述第三电源电压的大小包括5v~7v。

37、进一步的改进是,所述主体电平转换电路的下拉管的沟道宽度缩小到2微米以下。

38、本发明的电平转换电路在主体电平转换电路的基础上增加辅助电平转换电路,辅助电平转换电路的电源端连接第二电源电压,第二电源电压会大于输入信号的高电平对应的第一电源电压,这样就能保证输入到主体电平转换电路的输入端的信号即第一输出信号具有较高值,防止第一电源电压过低时对主体电平转换电路的下拉管的驱动能力过低的不利影响,所以,通过调节第二电源电压的大小就能提升主体电平转换电路的下拉管的驱动能力,而不需要通过增加主体电平转换电路的下拉管的沟道宽度来增加下拉管的驱动能力,这样就能减少电平转换电路的总体面积;当电平转换电路应用于大容量的闪存知识产权核(ip)的译码器时,对芯片减少是明显的,最终能节约芯片成本。

- 还没有人留言评论。精彩留言会获得点赞!