逐次逼近型模数转换器、转换方法、装置及存储介质

本发明涉及模数转换器,尤其是一种逐次逼近型模数转换器、转换方法、装置及存储介质。

背景技术:

1、近年来,逐次逼近型模数转换器以中等转换精度、中等转换速度、低功耗、低成本和易于按比例缩小的优势,被广泛采用,研究方向也开始向着更高速、更高精度、更低功耗发展。相关技术中的模数转换器,电容个数随位数的增加呈指数增加,同时带来面积及功耗增大的问题。即当模数转换器的分辨率提高时,电容阵列所占面积和功耗也会大幅度扩大。

技术实现思路

1、本发明的目的在于至少一定程度上解决现有技术中存在的技术问题之一。

2、为此,本发明的目的在于提供一种低功耗、高分辨率的逐次逼近型模数转换器、转换方法、装置及存储介质。

3、为了达到上述技术目的,本发明实施例所采取的技术方案包括:

4、一方面,本发明实施例提供了一种逐次逼近型模数转换器的转换方法,包括以下步骤:

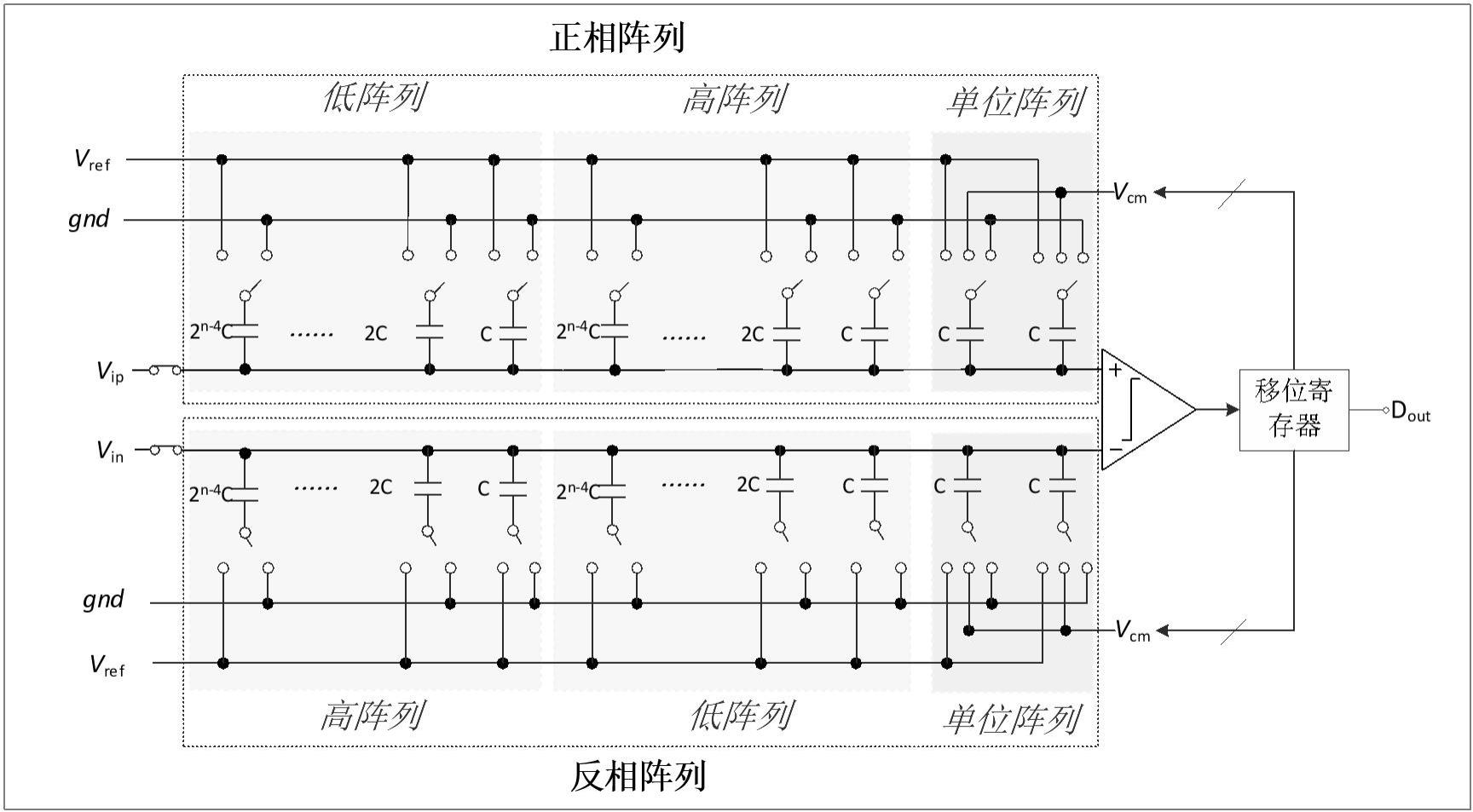

5、本发明实施例的逐次逼近型模数转换器,包括:移位寄存器、比较器、电容阵列和控制模块:其中,输入电压通过所述电容阵列与所述比较器相连,所述比较器与所述移位寄存器相连;所述电容阵列包括高阵列、低阵列和单位阵列,所述高阵列包括第一高阵列和第二高阵列,所述低阵列包括第一低阵列和第二低阵列,所述单位阵列包括第一单位阵列和第二单位阵列;所述第一低阵列、所述第一高阵列、所述第一单位阵列依次相连后与所述比较器的正相输入端相连;所述第二高阵列、所述第二低阵列、所述第二单位阵列依次相连后与所述比较器的反相输入端相连;所述第一低阵列、所述第一高阵列、所述第二低阵列和所述第二高阵列的结构相同,所述第一高阵列包括若干电容,所述若干电容的电容量呈指数变化;所述若干电容的每个电容的顶板与所述比较器相连,所述每个电容的底板通过第一转换开关连接参考电压或参考地,所述第一转换开关与所述控制模块相连;所述第一单位阵列和所述第二单位阵列的结构相同,所述第一单位阵列包括若干单位电容;所述若干单位电容的每个单位电容的顶板与所述比较器相连,所述每个单位电容的底板通过第二转换开关连接参考电压、共模电压或参考地中的一种,所述第二转换开关与所述控制模块相连;所述移位寄存器用于根据所述比较器的输出结果确定数字信号,所述控制模块用于根据所述比较器的输出结果确定第一转换开关或第二转换开关的状态。本技术实施例通过高阵列、低阵列和单位阵列排序的电容阵列构建模数转换器的电容阵列,能够以较少的电容数量,实现较多位数的输出;提升分辨率的同时,降低模数转换器的面积和功耗。

6、另外,根据本发明上述实施例的逐次逼近型模数转换器的转换方法,还可以具有以下附加的技术特征:

7、进一步地,本发明实施例的逐次逼近型模数转换器,所述模数转换器还包括第一采样开关和第二采样开关,所述正相输入信号通过所述第一采样开关与所述比较器的正相输入端相连,所述反相输入信号通过所述第二采样开关与所述比较器的反相输入端相连;

8、在所述模数转换器工作的第一阶段,所述控制模块用于将所述高阵列中电容的底板与所述参考电压相连;所述控制模块用于将所述低阵列中电容的底板与所述参考地相连;所述控制模块用于将所述单位阵列中单位电容的底板与所述共模电压相连。

9、进一步地,在本发明的一个实施例中,所述控制模块用于根据所述比较器的输出结果确定第一转换开关或第二转换开关的状态,包括:

10、在所述模数转换器工作的第二阶段,所述控制模块用于根据比较器上一次的输出结果,确定所述比较器中高电压输入端对应的高阵列中电容的底板与所述参考地相连,并确定所述比较器中低电压输入端对应的低阵列中电容的底板与所述参考电压相连;其中,所述高电压输入端的电势大于所述低电压输入端的电势。

11、进一步地,在本发明的一个实施例中,所述控制模块用于根据所述比较器的输出结果确定第一转换开关或第二转换开关的状态,包括:

12、在所述模数转换器工作的第三阶段,所述控制模块用于根据比较器上一次的输出结果,确定所述比较器中高电压输入端对应的单位阵列中第一单位电容的底板与参考地相连,并确定所述比较器中低电压输入端对应的单位阵列中第一单位电容的底板与参考电压相连;其中,所述高电压输入端的电势大于所述低电压输入端的电势,所述第一单位电容用于表征所述单位阵列中远离所述比较器位置的第一位电容。

13、进一步地,在本发明的一个实施例中,所述控制模块用于根据所述比较器的输出结果确定第一转换开关的状态,包括:

14、在所述模数转换器工作的第四阶段,所述控制模块用于根据比较器上一次的输出结果,确定所述比较器中高电压输入端对应的单位阵列中第二单位电容的底板与参考地相连;其中,所述比较器包括高电压输入端和低电压输入端,所述高电压输入端的电势大于所述低电压输入端的电势,所述第二单位电容用于表征所述单位阵列中远离所述比较器位置的第二位电容。

15、另一方面,本技术实施例还提供一种逐次逼近型模数转换器的转换方法,应用于前述的逐次逼近型模数转换器,所述转换方法包括:

16、通过闭合第一采样开关和第二采样开关,接收模拟输入信号;

17、通过调节第一转换开关,确定将高阵列中电容的底板与参考电压相连,确定将低阵列中电容的底板与参考地相连;通过调节第二转换开关,确定将单位阵列中单位电容的底板与共模电压相连;

18、根据所述比较器的输出结果,输出数字信号;

19、根据比较器的输出结果,确定所述第一转换开关或所述第二转换开关的状态;并返回至所述根据所述比较器的输出结果,输出数字信号这一步骤。

20、进一步地,在本发明的一个实施例中,所述根据比较器的输出结果,确定所述第一转换开关或所述第二转换开关的状态,包括:

21、在所述模数转换器工作的第二阶段,根据比较器上一次的输出结果,确定所述第一转换开关的状态,以使所述比较器中高电压输入端对应的高阵列中电容的底板与所述参考地相连,所述比较器中低电压输入端对应的低阵列中电容的底板与所述参考电压相连;其中,所述高电压输入端的电势大于所述低电压输入端的电势;

22、或者,

23、在所述模数转换器工作的第三阶段,根据比较器上一次的输出结果,确定所述第二转换开关的状态,以使所述比较器中高电压输入端对应的单位阵列中第一单位电容的底板与参考地相连,所述比较器中低电压输入端对应的单位阵列中第一单位电容的底板与参考电压相连;其中,所述高电压输入端的电势大于所述低电压输入端的电势,所述第一单位电容用于表征所述单位阵列中远离所述比较器位置的第一位电容;

24、或者,

25、在所述模数转换器工作的第四阶段,根据比较器上一次的输出结果,确定所述第一转换开关的状态,以使所述比较器中高电压输入端对应的单位阵列中第二单位电容的底板与参考地相连;其中,所述比较器包括高电压输入端和低电压输入端,所述高电压输入端的电势大于所述低电压输入端的电势,所述第二单位电容用于表征所述单位阵列中远离所述比较器位置的第二位电容。

26、进一步地,在本发明的一个实施例中,该方法还包括:

27、在所述模数转换器工作的第二阶段,依次根据比较器上一次的输出结果,按第一顺序调节高阵列中每个第一转换开关的状态,并根据当前比较器的输出结果,按第二顺序输出数字信号;所述第一顺序用于表征对所述电容按照电容量从大到小或从小到大的顺序排列,所述第二顺序用于表征从左到右或从右到左的顺序。

28、另一方面,本发明实施例提供了一种逐次逼近型模数转换器的转换装置,包括:

29、至少一个处理器;

30、至少一个存储器,用于存储至少一个程序;

31、当所述至少一个程序被所述至少一个处理器执行时,使得所述至少一个处理器实现上述的逐次逼近型模数转换器的转换方法。

32、另一方面,本发明实施例提供了一种存储介质,其中存储有处理器可执行的程序,所述处理器可执行的程序在由处理器执行时用于实现上述的逐次逼近型模数转换器的转换方法。

33、本技术实施例提供了一种逐次逼近型模数转换器,包括移位寄存器、比较器、电容阵列和控制模块:其中,输入电压通过所述电容阵列与所述比较器相连,所述比较器与所述移位寄存器相连;所述电容阵列包括高阵列、低阵列和单位阵列,所述高阵列包括第一高阵列和第二高阵列,所述低阵列包括第一低阵列和第二低阵列,所述单位阵列包括第一单位阵列和第二单位阵列;所述第一低阵列、所述第一高阵列、所述第一单位阵列依次相连后与所述比较器的正相输入端相连;所述第二高阵列、所述第二低阵列、所述第二单位阵列依次相连后与所述比较器的反相输入端相连;所述第一低阵列、所述第一高阵列、所述第二低阵列和所述第二高阵列的结构相同,所述第一高阵列包括若干电容,所述若干电容的电容量按照排列位置呈指数变化;所述若干电容的每个电容的顶板与所述比较器相连,所述每个电容的底板通过第一转换开关连接参考电压或参考地,所述第一转换开关与所述控制模块相连;所述第一单位阵列和所述第二单位阵列的结构相同,所述第一单位阵列包括若干单位电容;所述若干单位电容的每个单位电容的顶板与所述比较器相连,所述每个单位电容的底板通过第二转换开关连接参考电压、共模电压或参考地中的一种,所述第二转换开关与所述控制模块相连;所述移位寄存器用于根据所述比较器的输出结果确定数字信号,所述控制模块用于根据所述比较器的输出结果确定第一转换开关或第二转换开关的状态。本技术实施例通过高阵列、低阵列和单位阵列排序的电容阵列构建模数转换器的电容阵列,能够以较少的电容数量,实现较多位数的输出;提升分辨率的同时,降低模数转换器的功耗。

- 还没有人留言评论。精彩留言会获得点赞!