时钟数据恢复装置的制作方法

本发明涉及时钟数据恢复装置。更具体地本发明涉及一种时钟数据恢复装置,其可以减小bang-bang环路中的环路迟延以便改善时钟和数据恢复特性。

背景技术:

1、通常,利用bang-bang鉴相器的时钟数据恢复环路为了保持正常状态(steady-stage),即锁定状态(locking state)动作,执行比较数据和时钟的时序而快速或缓慢地变更时钟频率的动作。

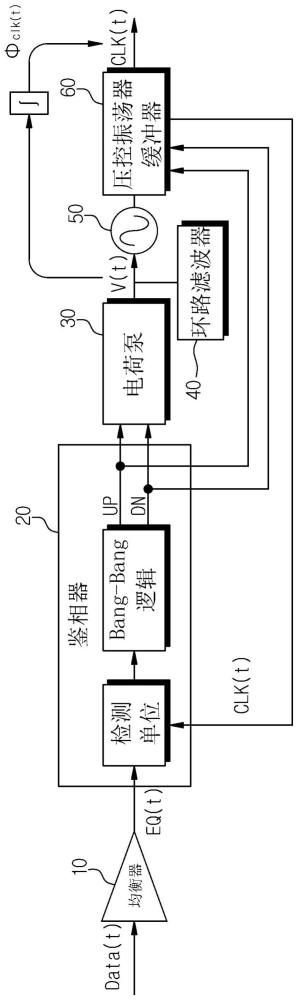

2、图1是示例性示出根据现有技术的时钟数据恢复装置的图,图2是示例性示出根据现有技术的时钟数据恢复装置中用于使时钟与数据同步的信号处理时序的图。

3、参照图1和图2,现有技术的时钟数据恢复装置包括:均衡器10,所述均衡器10补偿输入的数据的通道损耗;鉴相器20,所述鉴相器20比较均衡器10输出的数据与从压控振荡器50获得反馈的时钟并输出上升信号(up)和下降信号(dn);电荷泵30,所述电荷泵30根据上升信号和下降信号进行操作以输出控制压控振荡器50的控制信号;环路滤波器40,所述环路滤波器40去除电荷泵30输出的控制信号中包含的高频成分;及压控振荡器50,所述压控振荡器50根据去除了高频成分的控制信号来转换时钟的频率并输出。

4、但是,根据这种现有技术,比较数据与时钟的时序后,应用与其相应的压控振荡器的频率变更,而由于发生相当长时间的迟延,这成为增加bang-bang环路抖动(jitter)的因素。

5、先行技术文献

6、专利文献

7、(专利文献1)韩国授权专利公报第10-0780959号(授权日:2007年11月23日,名称:能够减小bang-bang抖动的迟延同步环路电路)

8、(专利文献2)韩国授权专利公报第10-1706196号(授权日:2017年2月7日,名称:改善相位同步性能的bang-bang鉴相器)

9、(专利文献3)韩国授权专利公报第10-2012-0025179号(授权日:2012年3月15日,名称:利用bang-bang鉴相器改善抖动特性的时钟数据恢复电路)

技术实现思路

1、技术课题

2、本发明的目的在于提供一种时钟数据恢复装置,其可以减小bang-bang环路中的环路迟延以便改善时钟和数据恢复特性。

3、此外,本发明的进一步目的在于,无迟延地把bang-bang环路的上升信号和下降信号立即反映到作为压控振荡器的输出信号的时钟上,而减小bang-bang抖动,改善在时钟数据恢复电路内部生成的内部时钟和数据的时序容限(timing margin),在外部输入噪声(input noise)上也改善数据和时钟恢复特性,在时钟数据恢复电路中发生数据对比时钟的时序错误(timing error)时立即反映到各个环路,从而提高时钟数据恢复环路的跟踪(tracking)性能。

4、要解决的技术问题

5、为了解决这些问题,本发明的时钟数据恢复装置,用于减小bang-bang环路中的环路迟延,包括:均衡器,所述均衡器补偿输入的数据的通道损耗;鉴相器,所述鉴相器比较所述均衡器输出的数据与获得反馈的时钟并输出上升信号(up)和下降信号(dn);电荷泵,所述电荷泵根据所述上升信号和所述下降信号进行操作以输出控制信号;环路滤波器,所述环路滤波器去除所述电荷泵输出的控制信号中包含的高频成分;压控振荡器,所述压控振荡器根据所述去除了高频成分的控制信号来转换所述时钟的频率并输出;及压控振荡器缓冲器,所述压控振荡器缓冲器根据从所述鉴相器直接传递的上升信号和下降信号,调节所述压控振荡器输出的时钟的压摆率(slew rate)并传递给所述鉴相器。

6、根据本发明的时钟数据恢复装置,其特征在于,所述鉴相器为bang-bang鉴相器。

7、根据本发明的时钟数据恢复装置,其特征在于,当从所述压控振荡器获得反馈的时钟的相位慢于所述均衡器输出的数据时,所述鉴相器输出所述上升信号,当从所述压控振荡器获得反馈的时钟的相位快于所述均衡器输出的数据时,所述鉴相器输出所述下降信号,当接收了所述上升信号时,流入所述压控振荡器缓冲器的电流增加,所述压控振荡器输出的时钟的压摆率增大,从而所述均衡器输出的数据与所述压控振荡器输出的时钟实现同步。

8、根据本发明的时钟数据恢复装置,其特征在于,当接收了所述下降信号时,流入所述压控振荡器缓冲器的电流减少,所述压控振荡器输出的时钟的压摆率减小,从而所述均衡器输出的数据与所述压控振荡器输出的时钟实现步骤。

9、根据本发明的时钟数据恢复装置,其特征在于,所述压控振荡器缓冲器包括:第一cmos,所述第一cmos的栅极端共同连接于所述压控振荡器的输出端;第一开关,所述第一开关连接于电源端与构成所述第一cmos的第一pmos的源极端之间,并始终保持导通状态;第二开关,所述第二开关连接于构成所述第一cmos的第一nmos的源极端与接地端之间,并始终保持导通状态;第三开关,所述第三开关连接于所述电源端与所述第一pmos的源极端之间,并根据所述上升信号而导通;第四开关,所述第四开关连接于所述第一nmos的源极端与所述接地端之间,并根据所述上升信号而导通;第五开关,所述第五开关连接于所述电源端与所述第一pmos的源极端之间,并根据使所述下降信号反转的信号而导通;第六开关,所述第六开关连接于所述第一nmos的源极端与所述接地端之间,并根据使所述下降信号反转的信号而导通;第二cmos,所述第二cmos的栅极端共同连接于所述第一cmos的漏极端;第七开关,所述第七开关连接于所述电源端与构成所述第二cmos的第二pmos的源极端之间,并始终保持导通状态;第八开关,所述第八开关连接于构成所述第二cmos的第二nmos的源极端与所述接地端之间,并始终保持导通状态;第九开关,所述第九开关连接于所述电源端与所述第二pmos的源极端之间,并根据所述上升信号而导通;第十开关,所述第十开关连接于所述第二nmos的源极端与所述接地端之间,并根据所述上升信号而导通;第十一开关,所述第十一开关连接于所述电源端与所述第二pmos的源极端之间,并根据使所述下降信号反转的信号而导通;及第十二开关,所述第十二开关连接于所述第二nmos的源极端与所述接地端之间,并根据使所述下降信号反转的信号而导通。

10、根据本发明的时钟数据恢复装置,其特征在于,当从所述鉴相器传递的上升信号和下降信号均为低电平时,所述第三开关、所述第四开关、所述第九开关、所述第十开关断开,所述第五开关、所述第六开关、所述第十一开关、所述第十二开关导通。

11、根据本发明的时钟数据恢复装置,其特征在于,当从所述鉴相器传递的上升信号为高电平时,所述第三开关、所述第四开关、所述第五开关、所述第六开关、所述第九开关、所述第十开关、所述第十一开关、所述第十二开关导通。

12、根据本发明的时钟数据恢复装置,其特征在于,当从所述鉴相器传递的上升信号为高电平时,所述上升信号和所述下降信号均与低电平进行比较,流入所述压控振荡器缓冲器的电流增加,所述压控振荡器输出的时钟的压摆率增大,从而所述均衡器输出的数据与所述压控振荡器输出的时钟实现同步。

13、根据本发明的时钟数据恢复装置,其特征在于,当从所述鉴相器传递的下降信号为高电平时,所述第三开关、所述第四开关、所述第五开关、所述第六开关、所述第九开关、所述第十开关、所述第十一开关、所述第十二开关断开。

14、根据本发明的时钟数据恢复装置,其特征在于,当从所述鉴相器传递的下降信号为高电平时,所述上升信号和所述下降信号均与低电平进行比较,流入所述压控振荡器缓冲器的电流减少,所述压控振荡器输出的时钟的压摆率减小,从而所述均衡器输出的数据与所述压控振荡器输出的时钟实现同步。

15、发明效果

16、根据本发明,提供一种时钟恢复装置,其可以减小bang-bang环路中的环路迟延以便改善时钟和数据恢复特性。

17、此外,可以无迟延地把bang-bang环路的上升信号和下降信号立即反映到作为压控振荡器的输出信号的时钟上,而减小bang-bang抖动,改善在时钟数据恢复电路内部生成的内部时钟和数据的时序容限(timing margin),在外部输入噪声(input noise)上也改善数据和时钟恢复特性,在时钟数据恢复电路中发生数据对比时钟的时序错误(timingerror)时立即反映到各个环路,从而提高时钟数据恢复环路的跟踪(tracking)性能。

- 还没有人留言评论。精彩留言会获得点赞!