滤波器件以及方法与流程

本公开大体上涉及信号滤波器件、电路和方法。

背景技术:

1、被配置为发射无线信号(例如,射频信号)的电子器件或电路是已知的,所述无线信号是具有在例如从1ghz到120ghz的射频范围内的载波频率的信号。

2、根据例如由标准定义的目标应用,由这些器件发送的信号的所有功率必须在第一给定频率范围内,或者由这些器件发送的信号的功率的至少一定百分比必须在第二给定频率范围内,第二范围比第一范围窄。

3、与发射条件有关的发射信号的功率的符合性需要实施滤波器,例如当信号在60-ghz频带中发射时,该滤波器产生许多问题。

技术实现思路

1、需要克服已知滤波电路、器件和方法的全部或部分缺点,例如,当实施滤波以对例如在60ghz频带中发送的射频信号整形时。

2、一个实施例克服了已知滤波电路、器件和方法的全部或部分缺点,例如,当滤波被实施以对例如60ghz频带中的待发射的射频信号进行整形时。

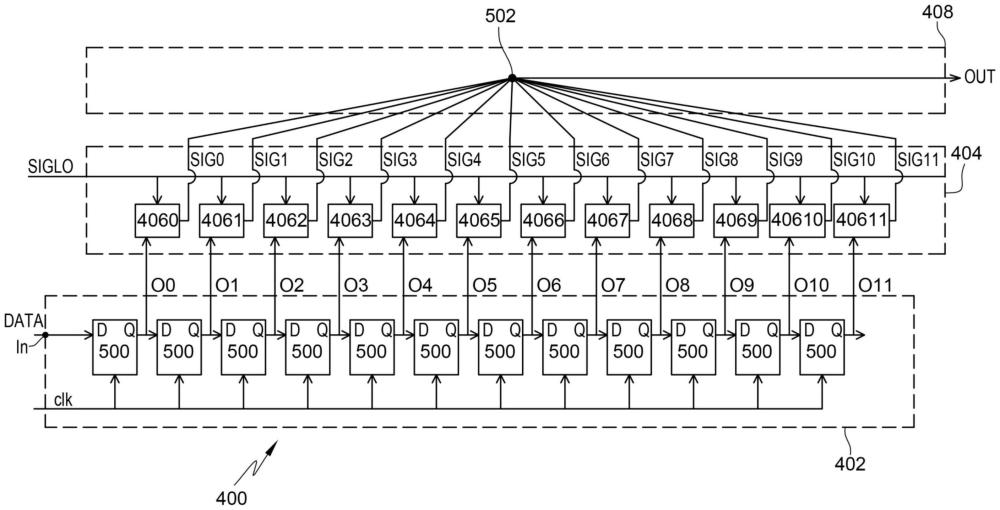

3、一个实施例提供了一种包括至少一个滤波电路的射频发射器,该至少一个滤波电路包括:串/并移位寄存器,其包括二进制输入和n个二进制输出oi,其中n是大于或等于osr的整数,osr是大于或等于2的整数,并且i是范围从0到n-1的整数索引,所述移位寄存器被配置为在其输入上接收处于频率fdata的二进制数据信号,并且在其输出oi上以等于fdata*osr的频率实施移位;第一电路,其由n个系数ci限定且被配置为针对每一非零系数ci传递模拟信号sigi,所述模拟信号sigi由所述系数ci及所述对应输出oi的二进制状态确定;以及加法器电路,被配置为传递等于模拟信号sigi的和的滤波电路的模拟输出信号。

4、另一实施例提供了一种在包括至少一个滤波电路的射频发射器中实施的方法,该方法包括:在所述至少一个滤波电路的串联/并联移位寄存器的二进制输入上接收处于频率fdata的二进制数据信号,所述移位寄存器包括n个二进制输出oi,其中n是大于或等于osr的整数,osr是大于或等于2的整数,并且i是范围从0到n-1的整数索引;用移位寄存器以频率fdata*osr实施将其输出oi的频率移位;利用至少一个滤波电路的第一电路,所述第一电路由n个系数ci定义,针对每个非零系数ci传递由系数ci和相应输出oi的二进制状态确定的模拟信号sigi;以及利用所述至少一个滤波电路的加法器电路传递等于模拟信号sigi之和的所述滤波电路的模拟输出信号。

5、根据一个实施例,系数ci由插值滤波器的脉冲响应h(t)确定,插值滤波器优选为升余弦型。

6、根据一个实施例:对于范围从0到n-1的i,每个系数ci等于整数索引p(等于i+min,min是正或零整数)的系数dp;每个系数dp,其中p是范围从0到p-1的整数索引并且p是大于n的奇数整数,是用以下算式以递归方式计算的:其中j为整数索引,如果j为负则dj为零,否则等于系数dp,其中p=j,并且bp为索引p的系数;并且每个系数bp,其中p是范围从0到p-1的整数索引,由以下算式确定:bp=h((2*p-p+1)/(2*osr))其中h(t)被归一化并以t=0为中心。

7、根据一个实施例,至少一个滤波电路的移位寄存器包括由频率等于fdata*osr/2的时钟信号控制的n个同步锁存器,n个锁存器通过交替地在时钟信号的第一电平上激活的锁存器和在时钟信号的第二电平上激活的锁存器串联耦合,输出oi对应于n个锁存器的输出。

8、根据实施例,所述至少一个滤波电路的移位寄存器还包括同步d型触发器,所述同步d型触发器具有耦合到(优选地连接到)移位寄存器的串联输入的数据输入,被配置为接收时钟信号的同步输入,以及连接到n个串联连接的锁存器中的第一个的数据输入的输出。

9、根据一个实施例,至少一个滤波电路的移位寄存器包括由频率等于fdata*osr的时钟信号控制的n个同步d型触发器,n个触发器被串联连接,并且输出oi对应于n个触发器的输出。

10、根据一个实施例,所述至少一个滤波电路的移位寄存器包括由频率等于fdata*osr/2的时钟信号控制的n个同步d型触发器,所述n个同步触发器通过交替地在时钟信号的上升沿激活的触发器和在时钟信号的下降沿激活的触发器而串联连接,并且输出oi对应于n个锁存器的输出。

11、根据一个实施例,对于每个非零系数ci:至少一个滤波电路的第一电路包括ki个相同的基本电路,每个基本电路具有被配置为传递以下各项的输出:当相应的输出oi处于第一二进制状态且系数ci为正时的模拟信号s0,当相应的输出oi处于第二二进制状态且系数ci为正时的与信号s0互补的信号s1,当相应的输出oi处于第一二进制状态且系数ci为负时的信号s1,以及当相应的输出oi处于第二二进制状态且系数ci为负时的信号s0;并且数ki等于对系数ci与所有系数ci相同的整数int的乘积的取整为整数值的绝对值。

12、根据实施例,所述至少一个滤波电路的第一电路包括用于每个系数ci的多个相同的基本电路,所述第一电路还包括选择电路,所述选择电路被配置为针对每个系数ci在所述多个基本电路中选择ki个基本电路,并且关断未选择的基本电路,对于等于零的系数ci,ki为零。

13、根据一个实施例,每个基本电路接收相同的周期信号,并且被配置为使得信号s0与该周期信号同相,并且与该周期信号的频率相同。

14、根据一个实施例:每个基本电路的输出包括第一输出节点和第二输出节点;每个基本电路包括:第一mos晶体管,其将参考节点耦合到第一内部节点,第二mos晶体管,其将所述参考节点耦合到第二内部节点,第三mos晶体管,其将所述第一内部节点耦合到所述第一输出节点且具有被配置为接收所述周期信号的栅极,第四mos晶体管,其将所述第一内部节点耦合到所述第二输出节点且具有被配置为接收与所述周期信号反相的信号的栅极,第五mos晶体管,其将所述第二内部节点耦合到所述第一输出节点且具有被配置为接收所述反相的信号的栅极,以及第六mos晶体管,其将所述第二内部节点耦合到所述第二输出节点且具有被配置为接收所述周期信号的栅极;并且对于每个非零系数ci和该系数ci的ki个基本电路中的每一个基本电路,第一和第二晶体管由相应的输出oi控制,或者彼此反相。

15、根据一个实施例:所述发射器包括两个滤波电路,所述两个滤波电路被配置为将它们的输出信号传递到耦合到所述发射器的天线的相同节点;两个滤波电路中的第一个滤波电路的移位寄存器的输入接收频率为fdata的第一二进制数据信号;两个电路中的第二个电路的移位寄存器的输入接收频率为fdata的第二二进制数据信号。

16、根据一个实施例:所述发射器包括至少一个本地振荡器,所述至少一个本地振荡器被配置为传递第一周期信号和与所述第一周期信号正交的第二周期信号;由第一滤波电路的基本电路接收的同一周期信号是第一周期信号;并且由第二滤波电路的基本电路接收的同一周期信号是第二周期信号。

17、根据实施例,发射器被配置为在60ghz频带中发射。

- 还没有人留言评论。精彩留言会获得点赞!