一种噪声整形的SARADC的时序逻辑控制电路

本发明属于激光雷达,具体涉及一种噪声整形的sar(successiveapproximation register,逐次逼近寄存器)adc(analog-to-digital converter,模数转换器)的时序逻辑控制电路。

背景技术:

1、早期激光雷达主要用于军事和民用地理测绘等领域,如地质测绘、监测树木生长、测量建筑项目进度等。随着自动驾驶的兴起,对于环境感知的要求日趋严格,在自动驾驶架构中,传感层被比作为汽车的“眼睛”,包括车载摄像头等视觉系传感器和车载毫米波雷达、车载激光雷达和车载超声波雷达等雷达系传感器,其中,激光雷达已经被广泛认为是实现自动驾驶的必要传感器。相比于其它类型的自动驾驶传感器如摄像头,激光雷达探测的距离更远,精度更高。相对于摄像头而言,激光雷达由于为主动发射光束,故比较不容易受周围环境如弱光、雨雪烟尘的影响,而且摄像头在进行图像识别处理时需要消耗大量的处理器能力,激光雷达产生的三维地图信息则更容易被计算机解析。相比毫米波雷达,激光雷达的分辨率更高,并且毫米波雷达也不适用于行人检测和目标识别等工作。在自动驾驶领域,激光雷达与其它传感器互为补充,可以有效提高车辆对于周围环境感知的准确度。

2、激光雷达并不是独立运作的,一般由激光发射器、接收器和惯性定位导航三个主要模块组成。接收机需要采集回波脉冲的时刻信息与幅度信息,现有技术中采用pdh的回波峰值采集方法,sar adc芯片完成将pdh采集到的信号进行数字量化并输出到fpga中做进一步的处理。随着对adc精度和功耗要求的提高,sar adc也进一步改进,主要采用噪声整形的sar adc(ns sar adc)。

3、但是,现有的噪声整形的sar adc多为同步时序进行比较器和环路滤波部分的控制,这对于外加时钟的频率要求比较高,导致整体功耗的增加,并且同步时序也不利于降低比较器工作阶段的功耗。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种噪声整形的sar adc的时序逻辑控制电路。本发明要解决的技术问题通过以下技术方案实现:

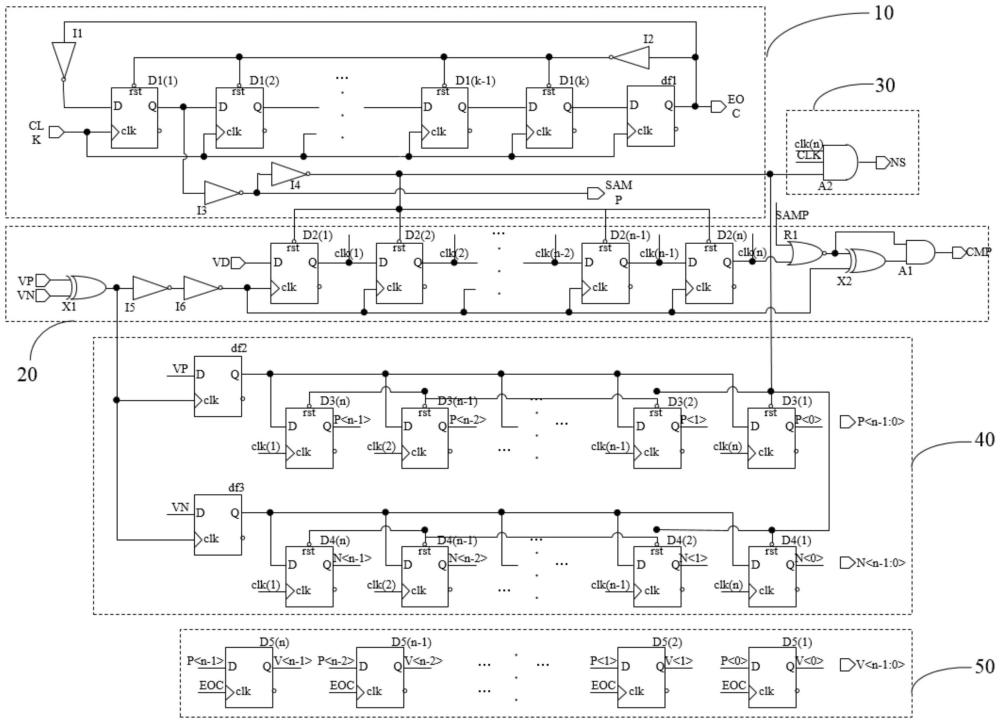

2、本发明提供一种噪声整形的sar adc的时序逻辑控制电路,包括:

3、采样信号产生模块,用于基于输入端口clk提供的输入时钟信号产生采样信号和输出标志信号;

4、异步时序控制信号产生模块,用于在所述采样信号变为低电平时,将比较器控制信号变为高电平,并获得sar adc中比较器的比较结果,进一步将所述比较器控制信号变为低电平,使所述比较器复位后输出低电平,并将所述比较器控制信号变为高电平;

5、同步时序控制信号产生模块,用于在所述比较器输出比较结果后,基于所述异步时序控制信号产生模块的时钟信号、所述输入时钟信号和所述采样信号,产生环路滤波电路控制信号,以控制sar adc中环路滤波电路工作,直至所述采样信号变为高电平;

6、电容阵列开关控制信号产生模块,用于根据所述比较器的比较结果产生开关控制信号,以控制sar adc中开关电容阵列的电压发生变化;

7、adc信号输出模块,用于存储并输出由所述比较器输出的为正的比较结果。

8、在本发明的一个实施例中,所述采样信号产生模块包括有复位功能的d触发器:d1(1)、d1(2)、……、d1(k-1)、d1(k)、无复位功能的d触发器df1、反相器:i1、i2、i3、i4、输出标志信号端口eoc及采样信号端口samp;其中,

9、d1(1)、d1(2)、……、d1(k-1)和d1(k)的时钟输入端clk以及df1的时钟输入端clk均与所述输入端口clk连接,d1(i)的输出端q与d1(i+1)的输入端d连接,d1(k)的输出端与df1的输出端d连接,i=1、2、……、k-1;i1、i2的输入端与df1的输出端d连接,并连接至所述输出标志信号端口eoc,i1的输出端与d1(1)的输入端d连接,i2的输出端与d1(1)、d1(2)、……、d1(k-1)和d1(k)的复位端rst连接,i3的输入端与d1(2)的输入端d连接,i3的输出端与所述采样信号端口samp及i4的输入端连接,i4的输出端连接至所述同步时序控制信号产生模块。

10、在本发明的一个实施例中,所述异步时序控制信号产生模块包括正输入端vp、反输入端vn、输入端口vd、输出端口cmp、异或门:x1、x2、二输入或非门r1、二输入与门a1、反相器:i5、i6以及有复位功能的d触发器:d2(1)、d2(1)、……、d2(n-1)、d2(n);其中,

11、x1的第一输入端、第二输入端分别接入正输入端vp和反输入端vn、输出端与i5的输入端连接,i5的输出端与i6的输入端连接;d2(1)、d2(1)、……、d2(n-1)、d2(n)的复位端rst均与i4的输出端连接,时钟输入端clk均与i6的输出端连接,d2(1)的输入端d与所述输入端口vd连接,d2(j)的输出端q与d2(j+1)的输入端d连接,并提供时钟信号clk(j),j=1、2、…、n-1,d2(n)的输出端连接至r1的第一输入端并提供时钟信号clk(n),r1的第二输入端接入所述采样信号,r1的输出端与x2的第一输入端连接,x2的第二输入端与i6的输出端连接、输出端与a1的第一输入端连接,a1的第二输入端与r1的输出端连接、输出端连接至所述输出端口cmp。

12、在本发明的一个实施例中,异步时序控制信号产生模块,还用于在时钟信号clk(n)变为高电平时,保持所述比较器控制信号为低电平。

13、在本发明的一个实施例中,所述同步时序控制信号产生模块包括三输入与门a2及滤波电路控制信号端ns;其中,

14、a2的第一输入端与d2(n)的输出端q连接,第二输入端与所述输入端口clk连接,第三输入端与i4的输出端连接,输出端与所述滤波电路控制信号端ns连接。

15、在本发明的一个实施例中,所述开关控制信号包括第一开关控制信号和第二开关控制信号,所述电容阵列开关控制信号产生模块包括具有复位功能的d触发器:d3(1)、d3(2)、……、d3(n-1)、d3(n)和d4(1)、d4(2)、……、d4(n-1)、d4(n),无复位功能的d触发器:df2、df3;其中,

16、df2的输入端d与所述正输入端vp连接、时钟输入端clk与x1的输出端连接;df3的输入端d与所述反输入端vn连接、时钟输入端clk与x1的输出端连接;d3(1)、d3(2)、……、d3(n-1)和d3(n)的复位端rst均连接至i4的输出端连接、输入端d均连接至df2的输出端q;d4(1)、d4(2)、……、d4(n-1)和d4(n)的复位端rst均与i4的输出端连接、输入端d均与df3的输出端q连接;d3(1)、d3(2)、……、d3(n-1)和d3(n)的时钟输入端clk分别接入时钟信号clk(n)、clk(n-1)、…、clk(1),d3(1)、d3(2)、…、d3(n)的输出端q分别产生第一开关控制信号p<0>、p<1>、…、p<n-1>;d4(1)、d4(2)、……、d4(n-1)和d4(n)的时钟输入端clk分别接入时钟信号clk(n)、clk(n-1)、…、clk(1),d4(1)、d4(2)、…、d4(n-1)和d4(n)的输出端q分别产生第二开关控制信号n<0>、n<1>、…、n<n-1>。

17、在本发明的一个实施例中,所述adc信号输出模块包含:无复位功能的d触发器:d5(1)、d5(2)、……、d5(n-1)、d5(n);其中,

18、d5(1)、d5(2)、……、d5(n-1)和d5(n)的时钟输入端clk接入所述输出端口eoc,d5(1)、d5(2)、……、d5(n-1)和d5(n)的输入端d分别接入所述第一开关控制信号p<0>、p<1>、…、p<n-1>,d5(1)、d5(2)、……、d5(n-1)和d5(n)的输出端q分别产生输出信号v<0>、v<1>、…、v<n-1>。

19、与现有技术相比,本发明的有益效果在于:

20、本发明通过引入触发器链和相应的逻辑门单元,实现了同步时序和异步时序的结合,使得噪声整形的sar adc在比较阶段使用异步时序,而在滤波电路处理阶段使用同步时序,从而降低了外部时钟频率的要求,减小了数字部分功耗的浪费;此外,比较器的异步时序操作可以减小比较阶段的功耗,同时在固定的采样频率下使得滤波电路的处理时间的裕度增加,从而利于实现更高阶的滤波电路。

21、以下将结合附图及实施例对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!